# JEDEC STANDARD

**GDDR5 SGRAM**

JESD212

DECEMBER 2009

JEDEC SOLID STATE TECHNOLOGY ASSOCIATION

### NOTICE

JEDEC standards and publications contain material that has been prepared, reviewed, and approved through the JEDEC Board of Directors level and subsequently reviewed and approved by the JEDEC legal counsel.

JEDEC standards and publications are designed to serve the public interest through eliminating misunderstandings between manufacturers and purchasers, facilitating interchangeability and improvement of products, and assisting the purchaser in selecting and obtaining with minimum delay the proper product for use by those other than JEDEC members, whether the standard is to be used either domestically or internationally.

JEDEC standards and publications are adopted without regard to whether or not their adoption may involve patents or articles, materials, or processes. By such action JEDEC does not assume any liability to any patent owner, nor does it assume any obligation whatever to parties adopting the JEDEC standards or publications.

The information included in JEDEC standards and publications represents a sound approach to product specification and application, principally from the solid state device manufacturer viewpoint. Within the JEDEC organization there are procedures whereby a JEDEC standard or publication may be further processed and ultimately become an ANSI standard.

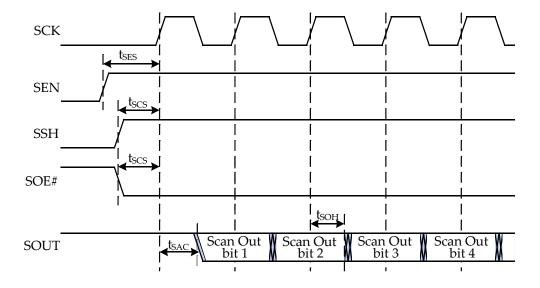

No claims to be in conformance with this standard may be made unless all requirements stated in the standard are met.

Inquiries, comments, and suggestions relative to the content of this JEDEC standard or publication should be addressed to JEDEC at the address below, or call (703) 907-7559 or www.jedec.org

Published by ©JEDEC Solid State Technology Association 2009 3103 North 10th Street Suite 240 South Arlington, VA 22201-2107

This document may be downloaded free of charge; however JEDEC retains the copyright on this material. By downloading this file the individual agrees not to charge for or resell the resulting material.

PRICE: Please refer to the current Catalog of JEDEC Engineering Standards and Publications online at http://www.jedec.org/Catalog/catalog.cfm

Printed in the U.S.A. All rights reserved

# PLEASE!

# DON'T VIOLATE THE LAW!

This document is copyrighted by the JEDEC Solid State Technology Association and may not be reproduced without permission.

Organizations may obtain permission to reproduce a limited number of copies through entering into a license agreement. For information, contact:

JEDEC Solid State Technology Association 3103 North 10th Street, Suite 240S Arlington, Virginia 22201 or call (703) 907-7559

# Contents

| 1 SCOPE                                             | 1    |

|-----------------------------------------------------|------|

| 2 GDDR5 SGRAM SPECIFICATION OVERVIEW                |      |

| 2.1 Features                                        |      |

| 2.2 Functional Description                          |      |

| 2.3 Definition of Signal State Terminology          |      |

| 2.4 Clocking                                        |      |

| 3 INITIALIZATION 3.1 Power-up Sequence              |      |

| 3.2 Initialization with Stable Power                |      |

| 3.3 Vendor ID                                       |      |

| 4 ADDRESS                                           |      |

| 4.1 Addressing                                      |      |

| 4.2 Address Bus Inversion (ABI)                     | . 13 |

| 4.3 Bank Groups                                     | . 15 |

| 5 TRAINING                                          |      |

| 5.1 Interface Training Sequence                     |      |

| 5.2 Address Training                                |      |

| 5.3 WCK2CK Training 5.4 READ Training               | . 19 |

| 5.5 WRITE Training                                  | . 20 |

| 6 MODE REGISTERS                                    |      |

| 6.1 Mode Register 0                                 |      |

| 6.2 Mode Register 1                                 | . 38 |

| 6.3 Mode Register 2                                 | . 40 |

| 6.4 Mode Register 3                                 |      |

| 6.5 Mode Register 4                                 |      |

| 6.6 Mode Register 5                                 |      |

| 6.7 Mode Register 6                                 |      |

| 6.9 Mode Register 8                                 |      |

| 6.10 Mode Register 15                               |      |

| 7 OPERATION                                         | . 54 |

| 7.1 Commands                                        | . 54 |

| 7.2 Deselect (NOP)                                  | . 55 |

| 7.3 No Operation (NOP)                              |      |

| 7.4 Mode Register Set                               | . 56 |

| 7.5 Activation                                      |      |

| 7.7 Write (WOM)                                     |      |

| 7.8 Write Data Mask (DM)                            |      |

| 7.9 Read                                            | . 70 |

| 7.10 DQ Preamble                                    |      |

| 7.11 Read and Write Data Bus Inversion (DBI)        | . 77 |

| 7.12 Error Detection Code (EDC).                    |      |

| 7.13 Precharge                                      |      |

| 7.14 Auto Precharge                                 |      |

| 7.16 Self Refresh                                   |      |

| 7.17 Power-Down.                                    |      |

| 7.18 Command Truth Tables                           |      |

| 7.19 Low Frequency Modes                            | . 93 |

| 7.20 RDQS Mode                                      |      |

| 7.21 Clock Frequency Change Sequence.               |      |

| 7.22 Dynamic Voltage Switching (DVS)                |      |

| 7.23 Temperature Sensor                             |      |

| 8.1 Absolute Maximum Ratings.                       |      |

| 8.2 AC & DC Characteristics.                        |      |

| 8.3 Clock-To-Data Timing Sensitivity                |      |

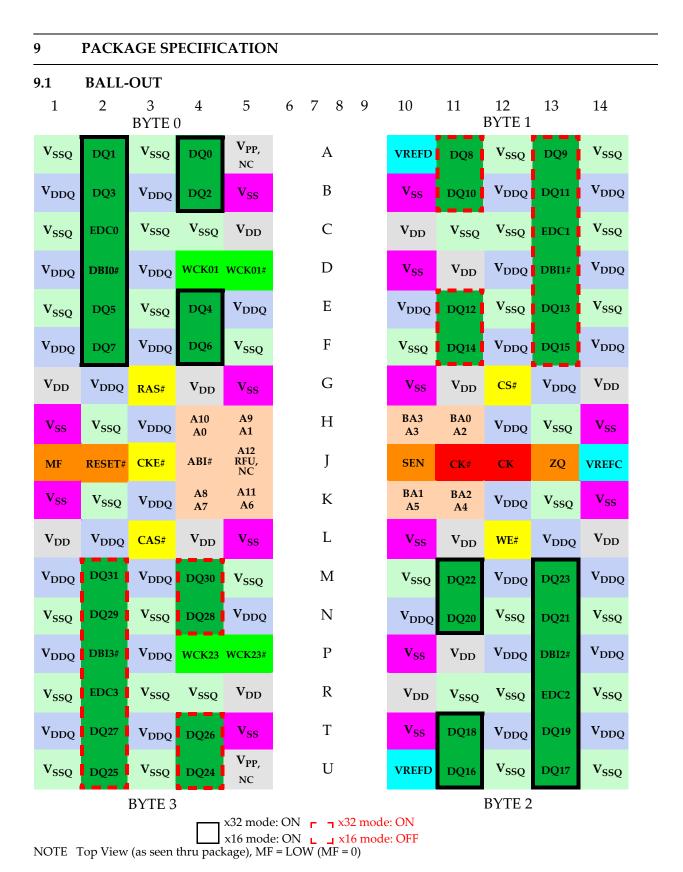

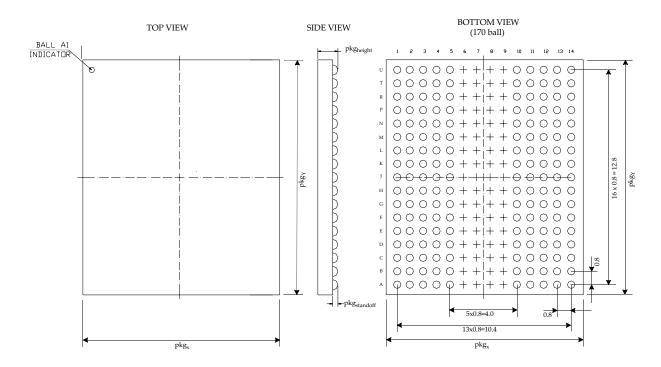

| 9 PACKAGE SPECIFICATION                             |      |

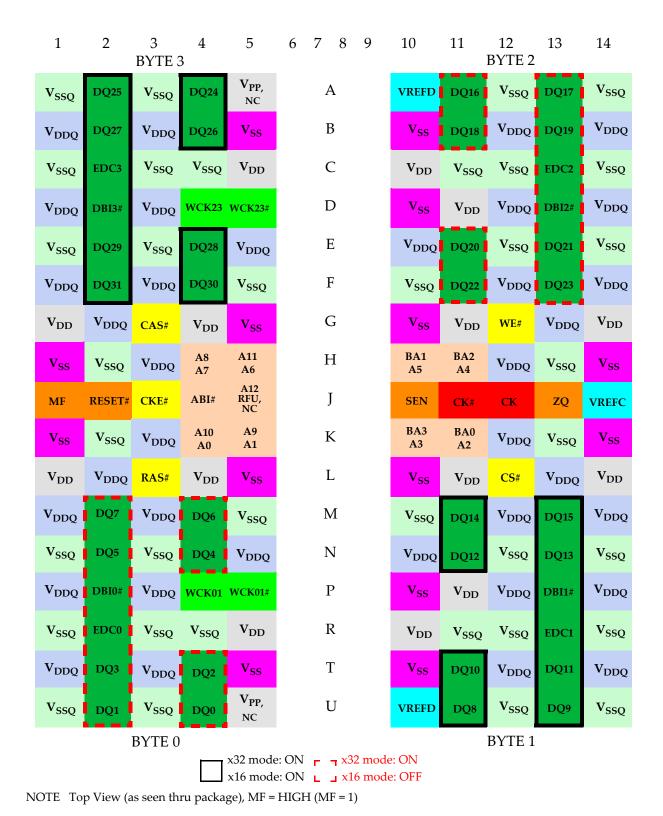

| 9.1 Ball-out                                        |      |

| 9.2 Signals                                         |      |

| 9.3 On Die Termination (ODT)                        |      |

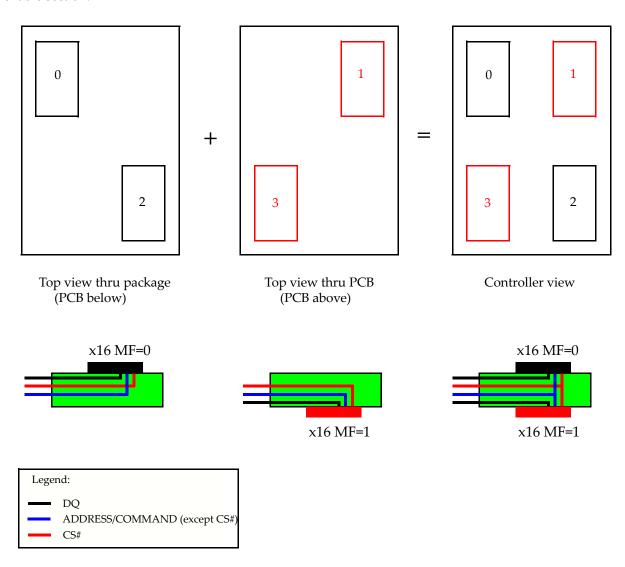

| 9.5 x16 Mode Enable and Mirror Function (MF) Enable |      |

| 10 BOUNDARY SCAN                                    |      |

# JEDEC Standard No. 212

# GRAPHICS DOUBLE DATA RATE (GDDR5) SGRAM STANDARD

(From JEDEC Board Ballot JCB-09-30, formulated under the cognizance of the JC-42.3C Subcommittee on Parametrics.)

# 1 SCOPE

This document defines the Graphics Double Data Rate 5 (GDDR5) Synchronous Graphics Random Access Memory (SGRAM) specification, including features, functionality, package, and pin assignments. This scope may be expanded in future to also include other higher density devices.

The purpose of this Specification is to define the minimum set of requirements for JEDEC standard compatible 512 Mb through 2 Gb  $\times$ 32 GDDR5 SGRAM devices. System designs based on the required aspects of this specification will be supported by all GDDR5 SGRAM vendors providing JEDEC standard compatible devices. Some aspects of the GDDR5 standard such as AC timings and capacitance values were not standardized. Some features are optional and therefore may vary among vendors. In all cases, vendor data sheets should be consulted for specifics.

This specification was created based on the DDR Standard (JESD79) and some aspects of the GDDR4 Standard (JESD21C - 3.11.5.8). Each aspect of the changes for high speed operation were considered and balloted. The accumulation of these ballots were then incorporated to prepare this GDDR5 SGRAM document, replacing whole sections and incorporating the changes into Functional Description and Operation.

### 2 GDDR5 SGRAM SPECIFICATION OVERVIEW

512 Mb = 16M x 32 (2M x 32 x 8 banks) / 32M x 16 (4M x 16 x 8 banks) 1 Gb = 32M x 32 (2M x 32 x 16 banks) / 64M x 16 (4M x 16 x 16 banks) 2 Gb = 64M x 32 (4M x 32 x 16 banks) / 128M x 16 (8Mx 16 x 16 banks)

# 2.1 FEATURES

- Single ended interface for data, address and command

- Quarter data-rate differential clock inputs CK/CK# for ADR/CMD

- Two half data-rate differential clock inputs WCK/WCK#, each associated with two data bytes (DQ, DBI#, EDC)

- Double Data Rate (DDR) data (WCK)

- Single Data Rate (SDR) command (CK)

- Double Data Rate (DDR) addressing (CK)

- 8 or 16 internal banks

- 4 bank groups for t<sub>CCDL</sub> = 3 t<sub>CK</sub> and 4 t<sub>CK</sub>

- 8n prefetch architecture: 256 bit per array read or write access

- Burst length: 8 only

- Programmable CAS latency: 5 to 36 t<sub>CK</sub>

- Programmable WRITE latency: 1 to 7 t<sub>CK</sub>

- WRITE Data mask function via address bus (single/double byte mask)

- Data bus inversion (DBI) & address bus inversion (ABI)

- Input/output PLL/DLL on/off mode

- Address training: address input monitoring by DQ pins

- WCK2CK clock training with phase information by EDC pins

- Data read and write training via READ FIFO

- READ FIFO pattern preload by LDFF command

- Direct write data load to READ FIFO by WRTR command

- Consecutive read of READ FIFO by RDTR command

- Read/Write data transmission integrity secured by cyclic redundancy check (CRC-8)

- READ/WRITE EDC on/off mode

- Programmable EDC hold pattern for CDR

- Programmable CRC READ latency = 0 to 3 t<sub>CK</sub>

- Programmable CRC WRITE latency = 7 to 14 t<sub>CK</sub>

- Low Power modes

- RDQS mode on EDC pin

- Optional on-chip temperature sensor with read-out

- Auto & self refresh modes

- Auto precharge option for each burst access

- 32ms, auto refresh (8k cycles)

- Temperature sensor controlled self refresh rate

- Optional digital t<sub>RAS</sub> lockout

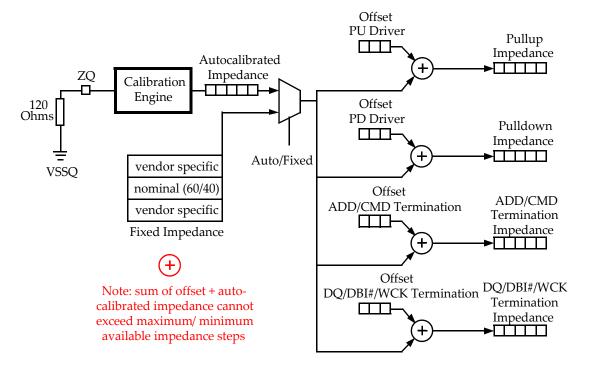

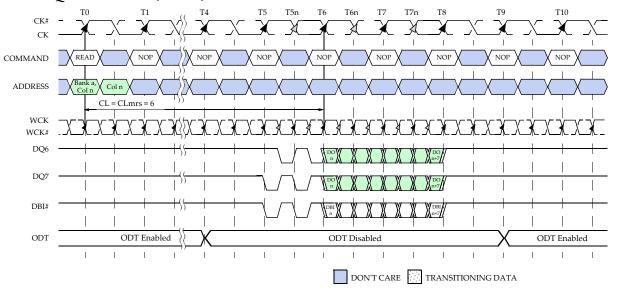

- On-die termination (ODT); nominal values of 60 ohm and 120 ohm

- Pseudo open drain (POD-15) compatible outputs (40 ohm pulldown, 60 ohm pullup)

- ODT and output drive strength auto-calibration with external resistor ZQ pin (120 ohm)

- Programmable termination and driver strength offsets

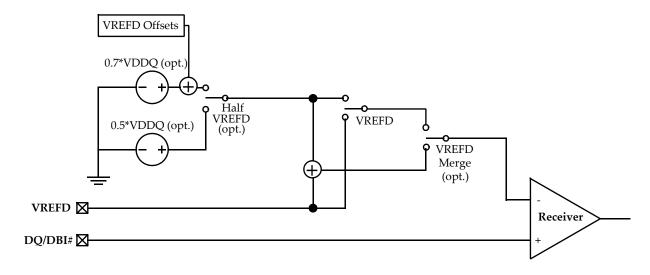

- Selectable external or internal VREF for data inputs; programmable offsets for internal VREF

- Separate external VREF for address / command inputs

- Vendor ID, FIFO depth and Density info fields for identification

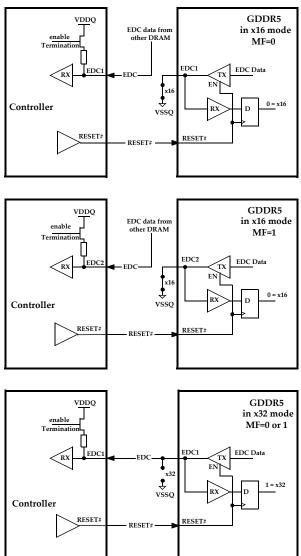

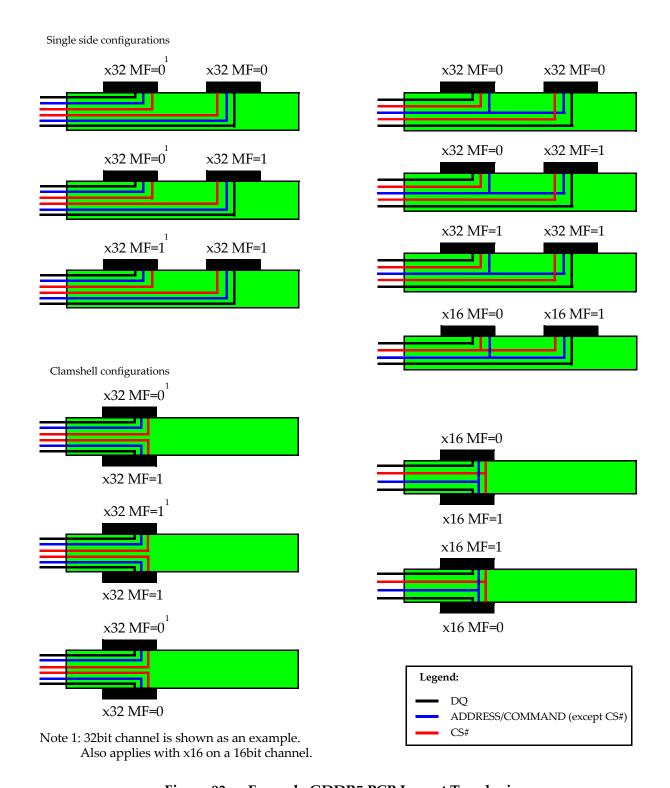

- x32/x16 mode configuration set at power-up with EDC pin

- Mirror function with MF pin

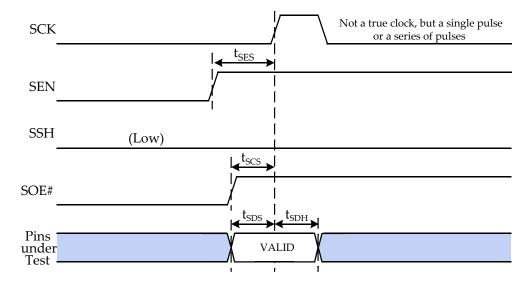

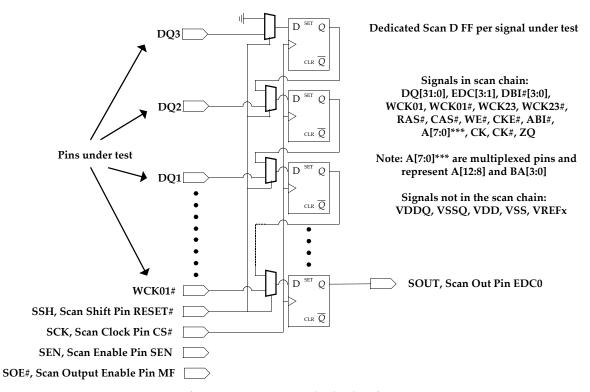

- Boundary scan function with SEN pin

- 1.5V +/- 0.045V supply for device operation (VDD)

- 1.5V +/- 0.045V supply for I/O interface (VDDQ)

- 170 ball BGA package

# 2.2 FUNCTIONAL DESCRIPTION

The GDDR5 SGRAM is a high speed dynamic random-access memory designed for applications requiring high bandwidth. GDDR5 devices contain the following number of bits:

512 Mb has 536,870,912 bits and eight banks 1 Gb has 1,073,741,824 bits and sixteen banks 2 Gb has 2,147,483,648 bits and sixteen banks

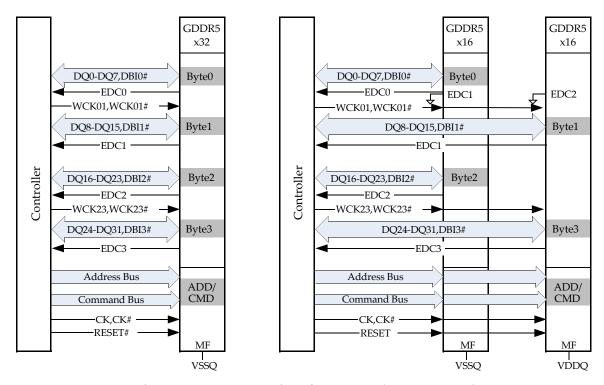

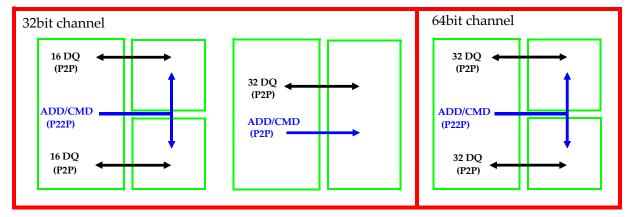

The GDDR5 SGRAM uses a 8n prefetch architecture and DDR interface to achieve high-speed operation. The device can be configured to operate in x32 mode or x16 (clamshell) mode. The mode is detected during device initialization. The GDDR5 interface transfers two 32 bit wide data words per WCK clock cycle to/from the I/O pins. Corresponding to the 8n-prefetch a single write or read access consists of a 256 bit wide, two CK clock cycle data transfer at the internal memory core and eight corresponding 32 bit wide one-half WCK clock cycle data transfers at the I/O pins.

The GDDR5 SGRAM operates from a differential clock CK and CK#. Commands are registered at every rising edge of CK. Addresses are registered at every rising edge of CK and every rising edge of CK#.

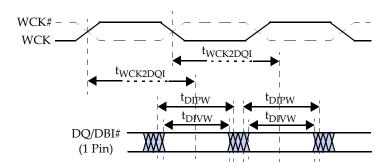

GDDR5 replaces the pulsed strobes (WDQS & RDQS) used in previous DRAMs such as GDDR4 with a free running differential forwarded clock (WCK/WCK#) with both input and output data registered and driven respectively at both edges of the forwarded WCK.

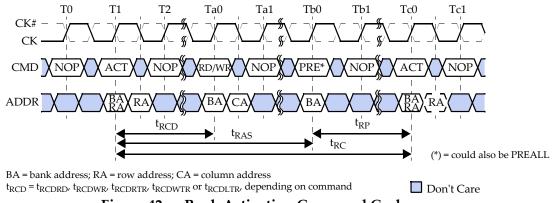

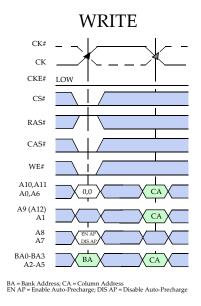

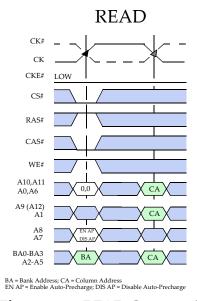

Read and write accesses to the GDDR5 SGRAM are burst oriented; an access starts at a selected location and consists of a total of eight data words. Accesses begin with the registration of an ACTIVE command, which is then followed by a READ or WRITE command. The address bits registered coincident with the ACTIVE command and the next rising CK# edge are used to select the bank and the row to be accessed. The address bits registered coincident with the READ or WRITE command and the next rising CK# edge are used to select the bank and the column location for the burst access.

This specification includes all features and functionality required for JEDEC GDDR5 SGRAM devices. Users benefit from knowing that any system design based on the required aspects of the specification are supported by all GDDR5 SGRAM vendors; conversely users seeking to use any superset specifications bear the responsibility to verify support with individual vendors.

# 2.3 DEFINITION OF SIGNAL STATE TERMINOLOGY

GDDR5 SGRAM will be operated in both ODT Enable (terminated) and ODT Disable (unterminated) modes. For highest data rates it is recommended to operate in the ODT Enable mode. ODT Disable mode is designed to reduce power and may operate at reduced data rates. There exist situations where ODT Enable mode can not be guaranteed for a short period of time, i.e. during power up.

Following are four terminologies defined for the state of a device (GDDR5 SGRAM or controller) pin during operation. The state of the bus will be determined by the combination of the device pins connected to the bus in the system. For example in GDDR5 it is possible for the SGRAM pin to be tristated while the controller pin is High or ODT. In both cases the bus would be High if the ODT is enabled. For details on the GDDR5 SGRAM pins and their function see "BALL-OUT" and "SIGNALS" in the section entitled "PACK-AGE SPECIFICATION".

# Device pin signal level:

- High: A device pin is driving the Logic "1" state.

- Low: A device pin is driving the Logic "0" state.

- Hi-Z: A device pin is tristate.

- ODT: A device pin terminates with ODT setting, which could be terminating or tristate depending on Mode Register setting.

# Bus signal level:

- High: One device on bus is High and all other devices on bus are either ODT or Hi-Z. The voltage level on the bus would be nominally VDDQ

- Low: One device on bus is Low and all other devices on bus are either ODT or Hi-Z. The voltage level on the bus would be nominally VOL(DC) if ODT was enabled, or VSSQ if Hi-Z.

- Hi-Z: All devices on bus are Hi-Z. The voltage level on bus is undefined as the bus is floating.

- ODT: At least one device on bus is ODT and all others are Hi-Z. The voltage level on the bus would be nominally VDDQ.

# 2.4 CLOCKING

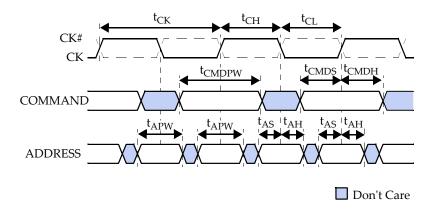

The GDDR5 SGRAM operates from a differential clock CK and CK#. Commands are registered at every rising edge of CK. Addresses are registered at every rising edge of CK and every rising edge of CK#.

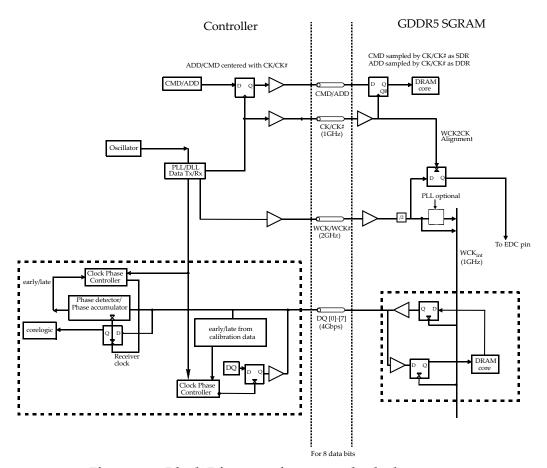

GDDR5 uses a DDR data interface and an 8n-prefetch architecture. The data interface uses two differential forwarded clocks (WCK/WCK#). DDR means that the data is registered at every rising edge of WCK and rising edge of WCK#. WCK and WCK# are continuously running and operate at twice the frequency of the command/address clock (CK/CK#).

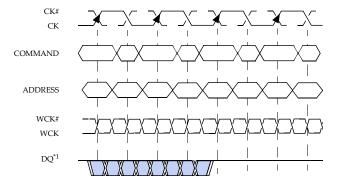

Figure 1 — GDDR5 Clocking and Interface Relationship

NOTE 1 Figure 1 shows the relationship between the data rate of the buses and the clocks and is not a timing diagram.

Figure 2 — Block Diagram of an example clock system

# 3 INITIALIZATION

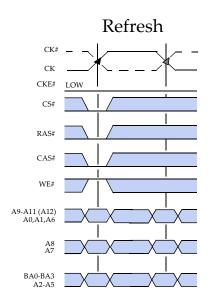

# 3.1 POWER-UP SEQUENCE

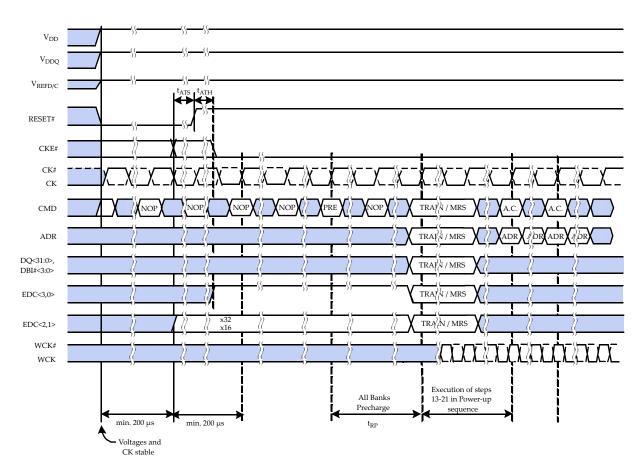

GDDR5 SGRAMs must be powered up and initialized in a predefined manner as shown in Figure 3. Operational procedures other than those specified may result in undefined operation. The Mode Registers do not have RESET default values, except for ABI#, ADR/CMD termination, and the EDC hold pattern. If the mode registers are not set during the initialization sequence, it may lead to unspecified operation.

| Step |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Apply power to VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2    | Apply power to VDDQ at same time or after power is applied to VDD                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3    | Apply VREFC and VREFD at same time or after power is applied to VDDQ                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4    | After power is stable, provide stable clock signals CK/CK#                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5    | Assert and hold RESET# low to ensure all drivers are in Hi-Z and all active terminations are off. Assert and hold NOP command.                                                                                                                                                                                                                                                                                                                                                                         |

| 6    | Wait a minimum of 200µs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

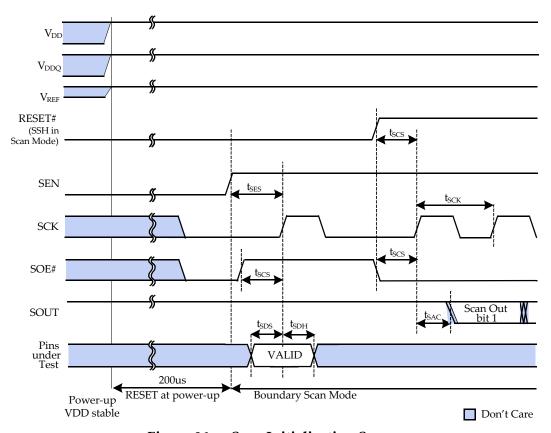

| 7    | If boundary scan mode is necessary, SEN can be asserted HIGH to enter boundary scan mode. Boundary scan mode must be entered directly after power-up while RESET# is low. Once boundary scan is executed, power-up sequence should be followed.                                                                                                                                                                                                                                                        |

| 8    | Set CKE# for the desired ADR/CMD ODT settings, then bring RESET# High to latch in the logic state of CKE#, t <sub>ATS</sub> and t <sub>ATH</sub> must be met during this procedure. See Table 1 for the values and logic states for CKE#. The rising edge of RESET# will determine x32 mode or x16 mode depending on the state of EDC1(EDC2 when MF=1). In normal x32 mode, EDC1 has to be sustained HIGH until RESET# is HIGH. See Table 56 for the values and logic states for EDC1(EDC2 when MF=1). |

| 9    | Bring CKE# Low after t <sub>ATH</sub> is satisfied                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 10   | Wait at least 200 $\mu$ s referenced from the beginning of $t_{ATS}$                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 11   | Issue at least 2 NOP commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

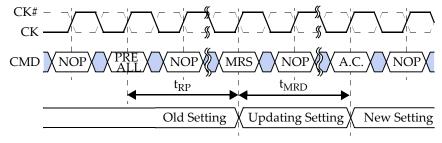

| 12   | Issue a PRECHARGE ALL command followed by NOP commands until $t_{RP}$ is satisfied                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 13   | Issue MRS command to MR15. Set GDDR5 SGRAM into address training mode (optional)                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 14   | Complete address training (optional)                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 15   | Issue MRS command to read the Vendor ID                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 16   | Issue MRS command to set WCK01/WCK01# and WCK23/WCK23# termination values                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 17   | Provide stable clock signals WCK01/WCK01# and WCK23/WCK23#                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 18   | Issue MRS commands to use PLL/DLL or not and select the position of a WCK/CK phase detector. The use of PLL/DLL and the position of a phase detector should be set before WCK2CK training. Issue MRS commands including PLL/DLL reset to the mode registers in any order. t <sub>MRD</sub> must be met during this procedure. WLmrs, CLmrs, CRCWL and CRCRL must be programmed before WCK2CK training.                                                                                                 |

| 19   | Issue two REFRESH commands followed by NOP until $t_{ m RFC}$ is satisfied                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 20   | After any necessary GDDR5 training sequences such as WCK2CK training, READ training (LDFF, RDTR) and WRITE training (WRTR, RDTR), the device is ready for operation.                                                                                                                                                                                                                                                                                                                                   |

Figure 3 — GDDR5 Power-up Sequence

# 3.1 POWER-UP SEQUENCE (cont'd)

Table 1 — Address and Command Termination

| VALUE (OHMS) | CKE# at RESET# high transition |

|--------------|--------------------------------|

| ZQ/2         | Low                            |

| ZQ           | High                           |

Note: A.C. = Any Command

Figure 4 — GDDR5 SGRAM Power-up Initialization

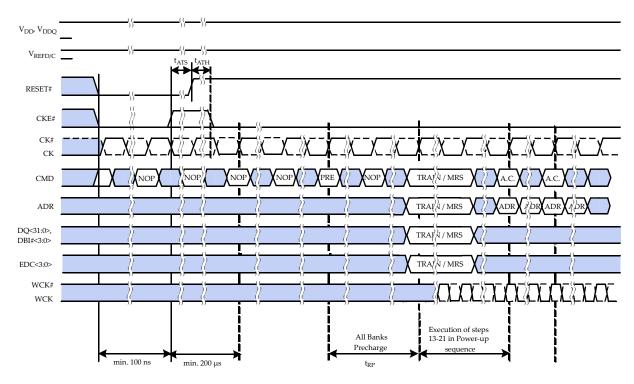

# 3.2 INITIALIZATION WITH STABLE POWER

The following sequence is required for reset subsequent to power-up initialization. This requires that the power has been stable within the specified VDD and VDDQ ranges since power-up initialization (see Figure 5):

- 1) Assert RESET# Low anytime when reset is needed.

- 2) Hold RESET# Low for minimum 100ns. Assert and hold NOP command.

- 3) Set CKE# for the desired ADR/CMD ODT settings, then bring RESET# High to latch in the logic state of CKE#;  $t_{ATS}$  and  $t_{ATH}$  must be met during this procedure. Keep EDC1 (MF=0) / EDC2 (MF=1) at the same logic level as during power-up initialization as device functionality is not guaranteed if the I/O width has changed.

- 4) Continue with step 9 of the power-up initialization sequence.

Notes: 1. A.C. = Any Command

2. Device functionality is not guaranteed if x32/x16 mode is not the same as during power-up initialization.

Figure 5 — Initialization with Stable Power

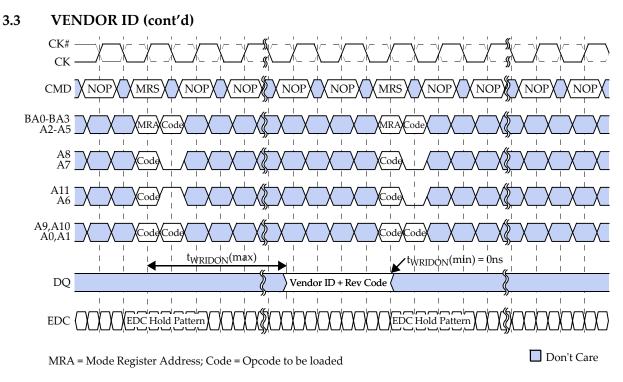

# 3.3 VENDOR ID

GDDR5 SGRAMs are required to include a Vendor ID feature that allows the controller to receive information from the GDDR5 SGRAM to differentiate between different vendors and different devices using a software algorithm.

When the Vendor ID function is enabled the GDDR5 SGRAM will provide its Manufacturers Vendor Code on bits [3:0] as shown in Table 2; Revision Identification on bits [7:4]; Density on bits [9:8] as shown in Table 3 and FIFO Depth on bits [11:10] as shown in Table 4. Bits [15:12] are RFU.

Vendor ID is part of the INFO field of Mode Register 3 (MR3) and is selected by issuing a MODE REGISTER SET command with MR3 bit A6 set to 1, and bit A7 set to 0. MR3 bits A0-A5 and A8-A11 are set to the desired values. Additional information can optionally be provided by the vendor using the vendor specific settings on the INFO field and will follow the same protocol as vendor ID unless explicitly stated in the vendor data sheet.

The Vendor ID will be driven onto the DQ bus after the MRS command that sets bits A6 to 1 and A7 to 0. The DQ bus will be continuously driven until an MRS command sets MR3 A6 and A7 back to 0 to disable the INFO field or to another valid state for the INFO field if the INFO field includes support for additional vendor specific information. The DQ bus will be in ODT state after  $t_{WRIDOFF}$  (max). The code can be sampled by the controller after waiting  $t_{WRIDON}$  (max) and before  $t_{WRIDOFF}$  (min). DBI is not enabled or ignored during all Vendor ID operations. Table 5 shows the mapping of the Vendor ID info to the physical DQs. The 16 bits of Vendor ID are sent on Byte 0 and 2 when MF=0. When MF=1 the 16 bits are sent on Byte 1 and 3. Optionally the vendor may replicate the data on the other 2 bytes when in x32 mode. Byte 0 would be replicated on Byte 1 and Byte 2 would be replicated on Byte 3 when MF=0. When MF=1, Byte 1 would be replicated on Byte 0 and Byte 3 would be replicated on Byte 2. The EDC hold pattern is continuously driven on the EDC pins provided a stable WCK clock is applied.

Table 2 — Manufacturers Vendor Code

| Manufacturers ID | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Name of Company |  |

|------------------|-------|-------|-------|-------|-----------------|--|

| 0                | 0     | 0     | 0     | 0     | Reserved        |  |

| 1                | 0     | 0     | 0     | 1     | Samsung         |  |

| 2                | 0     | 0     | 1     | 0     | Qimonda         |  |

| 3                | 0     | 0     | 1     | 1     | Elpida          |  |

| 4                | 0     | 1     | 0     | 0     | Etron           |  |

| 5                | 0     | 1     | 0     | 1     | Nanya           |  |

| 6                | 0     | 1     | 1     | 0     | Hynix           |  |

| 7                | 0     | 1     | 1     | 1     | ProMOS          |  |

| 8                | 1     | 0     | 0     | 0     | Winbond         |  |

| 9                | 1     | 0     | 0     | 1     | ESMT            |  |

| A                | 1     | 0     | 1     | 0     | Reserved        |  |

| В                | 1     | 0     | 1     | 1     | Reserved        |  |

| С                | 1     | 1     | 0     | 0     | Reserved        |  |

| D                | 1     | 1     | 0     | 1     | Reserved        |  |

| E                | 1     | 1     | 1     | 0     | Reserved        |  |

| F                | 1     | 1     | 1     | 1     | Micron          |  |

# 3.3 VENDOR ID (cont'd)

Table 3 — Density

| Bit 9 | Bit 8 | Density |

|-------|-------|---------|

| 0     | 0     | 512M    |

| 0     | 1     | 1G      |

| 1     | 0     | 2G      |

| 1     | 1     | RFU     |

Table 4 — FIFO Depth

| Bit 11 | Bit 10 | FIFO Depth |

|--------|--------|------------|

| 0      | 0      | 4          |

| 0      | 1      | 5          |

| 1      | 0      | 6          |

| 1      | 1      | RFU        |

Table 5 — Vendor ID to DQ mapping

| Bit     | 7    | 6                       | 5    | 4    | 3                         | 2    | 1    | 0    |

|---------|------|-------------------------|------|------|---------------------------|------|------|------|

| MF=0    | DQ7  | DQ6                     | DQ5  | DQ4  | DQ3                       | DQ2  | DQ1  | DQ0  |

| MF=1    | DQ31 | DQ30                    | DQ29 | DQ28 | DQ27                      | DQ26 | DQ25 | DQ24 |

| Feature |      | Revision Identification |      |      | Manufacturers Vendor Code |      |      |      |

|         |      |                         |      |      |                           |      |      |      |

| Bit     | 15   | 14                      | 13   | 12   | 11                        | 10   | 9    | 8    |

| MF=0    | DQ23 | DQ22                    | DQ21 | DQ20 | DQ19                      | DQ18 | DQ17 | DQ16 |

| MF=1    | DQ15 | DQ14                    | DQ13 | DQ12 | DQ11                      | DQ10 | DQ9  | DQ8  |

| Feature | RFU  |                         |      | FIFO | Depth                     | Der  | sity |      |

Figure 6 — Vendor ID Timing Diagram

### 4 ADDRESS

### 4.1 ADDRESSING

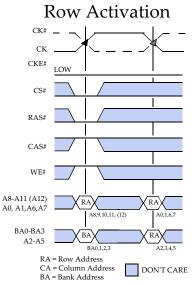

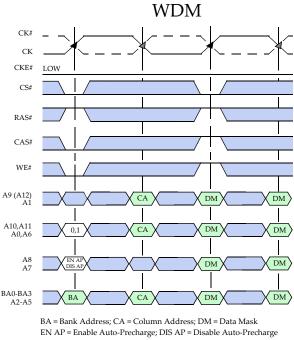

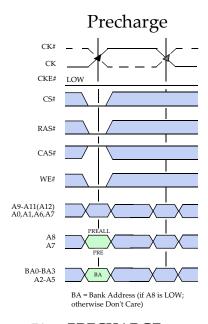

GDDR5 SGRAMs use a double data rate address scheme to reduce pins required on the GDDR5 SGRAM as shown in Table 6. The addresses should be provided to the GDDR5 SGRAM in two parts; the first half is latched on the rising edge of CK along with the command pins such as RAS#, CAS# and WE#; the second half is latched on the next rising edge of CK#.

The use of DDR addressing allows all address values to be latched in at the same rate as the SDR commands. All addresses related to command access have been positioned for latching on the initial rising edge for faster decoding.

Table 6 — Address Pairs

| Clock      |     |     |     |     |       |     |     |    |    |

|------------|-----|-----|-----|-----|-------|-----|-----|----|----|

| Rising CK  | BA3 | BA2 | BA1 | BA0 | (A12) | A11 | A10 | A9 | A8 |

| Rising CK# | A3  | A4  | A5  | A2  | (RFU) | A6  | A0  | A1 | A7 |

NOTE Address pin A12 is required only for 2G density.

GDDR5 addressing includes support for 512M, 1G and 2G densities. For all densities two modes are supported (x32 mode or x16 mode). x32 and x16 modes differ only in the number of valid column addresses, as shown in Table 7.

**Table 7** — Addressing Scheme

|                | 512M     |          | 1G       |          | 2G       |          |  |

|----------------|----------|----------|----------|----------|----------|----------|--|

|                | x32 mode | x16 mode | x32 mode | x16 mode | x32 mode | x16 mode |  |

| Row address    | A0~A11   | A0-A11   | A0~A11   | A0~A11   | A0~A12   | A0~A12   |  |

| Column address | A0~A5    | A0~A6    | A0~A5    | A0~A6    | A0~A5    | A0~A6    |  |

| Bank address   | BA0~BA2  | BA0-BA2  | BA0~BA3  | BA0~BA3  | BA0~BA3  | BA0~BA3  |  |

| Autoprecharge  | A8       | A8       | A8       | A8       | A8       | A8       |  |

| Page Size      | 2K       | 2K       | 2K       | 2K       | 2K       | 2K       |  |

| Refresh        | 8K/32ms  | 8K/32ms  | 8K/32ms  | 8K/32ms  | 16K/32ms | 16K/32ms |  |

| Refresh period | 3.9us    | 3.9us    | 3.9us    | 3.9us    | 1.9us    | 1.9us    |  |

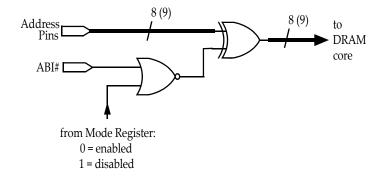

# 4.2 ADDRESS BUS INVERSION (ABI)

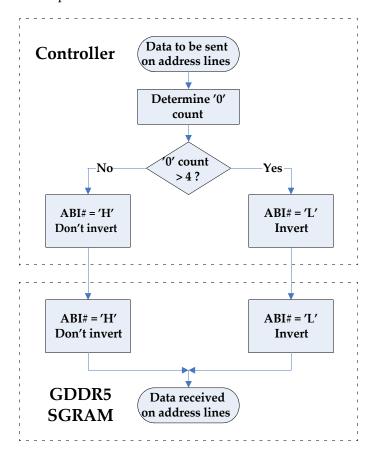

Address Bus Inversion (ABI) reduces the power requirements on address pins, as the no. of address lines driving a low level can be limited to 4 (in case A12/RFU is not wired) or 5 (in case A12/RFU is wired).

The Address Bus Inversion function is associated with the electrical signalling on the address lines between a controller and the GDDR5 SGRAM, regardless of whether the information conveyed on the address lines is a row or column address, a mode register op-code, a data mask, or any other pattern.

The ABI# input is an active Low double data rate (DDR) signal and sampled by the GDDR5 SGRAM at the rising edge of CK and the rising edge of CK# along with the address inputs.

Once enabled by the corresponding ABI Mode Register bit, the GDDR5 SGRAM will invert the pattern received on the address inputs in case ABI# was sampled Low, or leave the pattern non-inverted in case ABI# was sampled High, as shown in Figure 7

Note: bus width is 8 when A12/RFU pin is not present, and 9 when A12/RFU pin is present

Figure 7 — Example of Address Bus Inversion Logic

# 4.2 ADDRESS BUS INVERSION (ABI) (cont'd)

The flow diagram in Figure 8 illustrates the ABI operation. The controller decides whether to invert or not invert the data conveyed on the address lines. The GDDR5 SGRAM has to perform the reverse operation based on the level of the ABI# pin. Address input timing parameters are only valid with ABI being enabled and a maximum of 4 address inputs driven Low.

Figure 8 — Address Bus Inversion (ABI) Flow Diagram

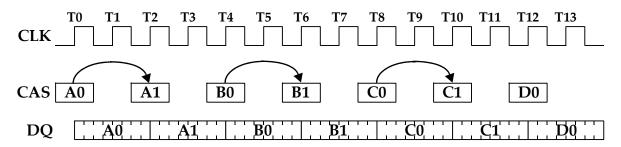

# 4.3 BANK GROUPS

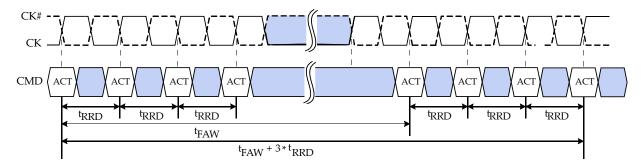

For GDDR5 SGRAM devices operating at frequencies above a certain threshold ( $f_{CKBG}$ ), the activity within a bank group must be restricted to ensure proper operation of the device. The 8 or 16 banks in GDDR5 SGRAMs are divided into four bank groups. The bank groups feature is controlled by bits A10 and A11 in Mode Register 3 (MR3). The assignment of the banks to the bank groups is shown in Table 8.

512M 1G 2GAddressing Bank BA<sub>3</sub> BA<sub>2</sub> BA1 BA<sub>0</sub> 8 banks 16 banks 16 banks Group A Group A Group A Group B Group C Group B Group B Group D Group C Group C Group D Group D

Table 8 — Bank Groups

These bank groups allow the specification of different command delay parameters depending on whether back-to-back accesses are to banks within one bank group or across bank groups as shown in Table 9.

| Tuble 5 Communic Sequences Firsteried by Busin Groups |                                   |                                   |                                     |       |  |  |  |  |

|-------------------------------------------------------|-----------------------------------|-----------------------------------|-------------------------------------|-------|--|--|--|--|

|                                                       | Corresponding AC Timing Parameter |                                   |                                     |       |  |  |  |  |

| Command Sequence                                      | Bank Groups                       | Bank Grou                         | ps Enabled                          | Notes |  |  |  |  |

| 1                                                     | Disabled                          | Accesses to different bank groups | Accesses within the same bank group |       |  |  |  |  |

| ACTIVE to ACTIVE                                      | t <sub>RRDS</sub>                 | t <sub>RRDS</sub>                 | t <sub>RRDL</sub>                   |       |  |  |  |  |

| WRITE to WRITE                                        | t <sub>CCDS</sub>                 | t <sub>CCDS</sub>                 | t <sub>CCDL</sub>                   |       |  |  |  |  |

| READ to READ                                          | t <sub>CCDS</sub>                 | t <sub>CCDS</sub>                 | t <sub>CCDL</sub>                   |       |  |  |  |  |

| Internal WRITE to READ                                | t <sub>WTRS</sub>                 | t <sub>WTRS</sub>                 | $t_{ m WTRL}$                       |       |  |  |  |  |

| READ to PRECHARGE                                     | t <sub>RTPS</sub>                 | 1 t <sub>ck</sub>                 | $t_{ m RTPL}$                       | 1     |  |  |  |  |

Table 9 — Command Sequences Affected by Bank Groups

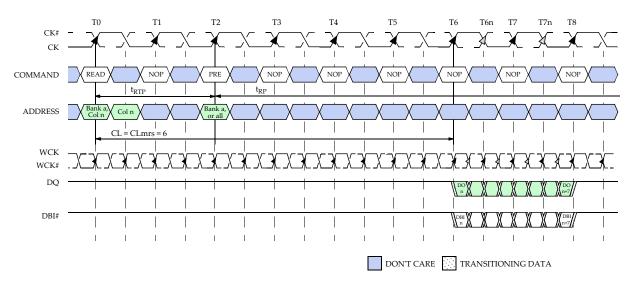

NOTE 1 Parameters  $t_{RTPS}$  and  $t_{RTPL}$  apply only when READ and PRECHARGE go to the same bank; use  $t_{RTPS}$  when BG are disabled, and  $t_{RTPL}$  when BG are enabled.

# 4.3 BANK GROUPS (cont'd)

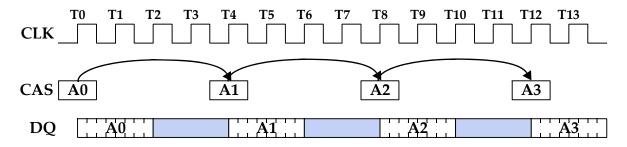

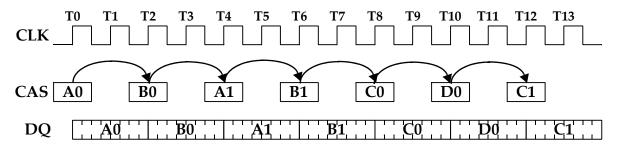

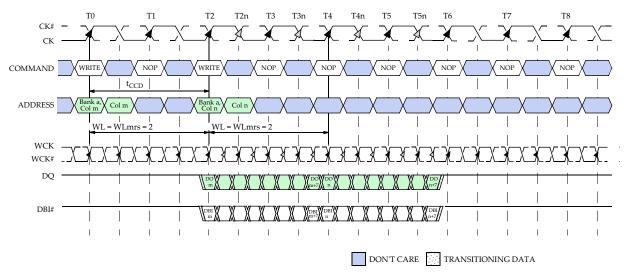

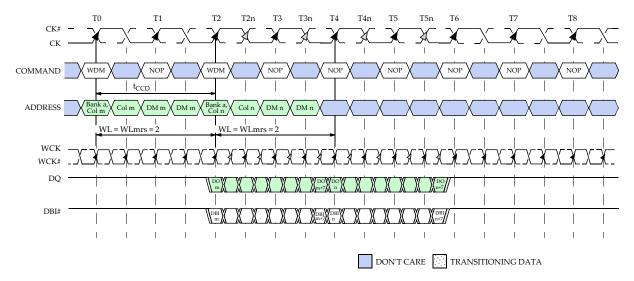

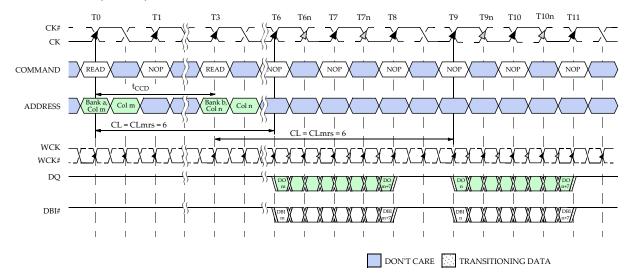

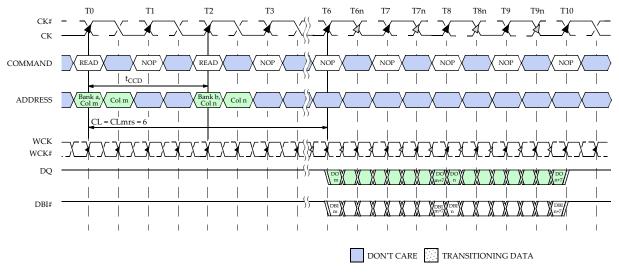

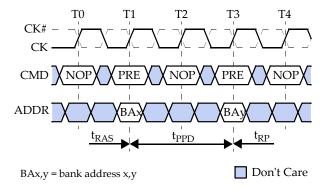

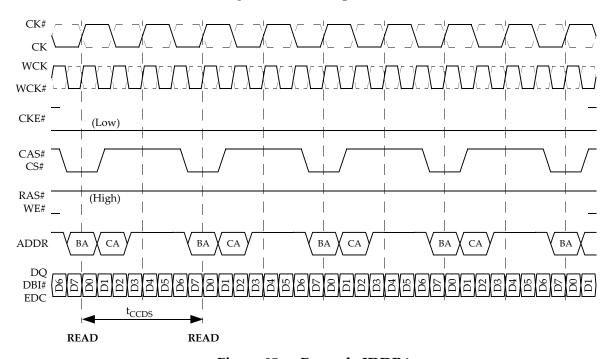

Figure 9 shows back-to-back column accesses based on  $t_{\text{CCDL}}$  and  $t_{\text{CCDS}}$  parameters.

# Example 1 (Bank Groups disabled): $t_{CCDS} = 2 * t_{CK}$

# Example 2: (Bank Groups enabled): $t_{CCDL} = 4 * t_{CK}$

# Example 3: (Bank Groups enabled): $t_{CCDS} = 2 * t_{CK}$

NOTE 1 Column accesses are to open banks, and  $t_{\text{RCD}}$  has been met.

NOTE 2 CL = 0 assumed

NOTE 3 Ax, Bx, Cx, Dx: accesses to bank groups A, B, C or D, respectively

NOTE 4 With bank groups enabled, t<sub>CCDL</sub> is 3t<sub>CK</sub> (optional) or 4 t<sub>CK</sub>, as programmed in MR3.

Figure 9 - t<sub>CCDS</sub> and t<sub>CCDL</sub>

# 5 TRAINING

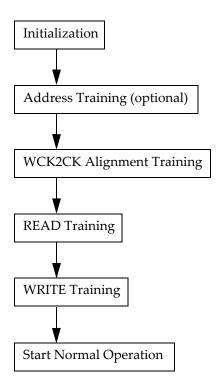

# 5.1 INTERFACE TRAINING SEQUENCE

Due to the high data rates of GDDR5, it is recommended that the interfaces be trained to operate with the optimal timings. GDDR5 SGRAM has features defined which allow for complete and efficient training of the I/O interface without the use of the GDDR5 SGRAM array. The interface trainings are required for normal DRAM functionality unless deemed optional by the DRAM vendor or unless running in lower frequency modes as described in the low frequency section. Interface timings will only be guaranteed after all required trainings have been executed.

A recommended order of training sequences has been chosen based on the following criteria:

The address training must be done first to allow full access to the Mode Registers. (MRS for address training is a special single data rate mode register set guaranteed to work without training). Address input timing shall function without training as long as  $t_{AS/H}$  are met at the GDDR5 SGRAM.

WCK2CK training should be done before read training because a shift in WCK relative CK will cause a shift in all READ timings relative to CK.

READ training should be done before WRITE training because optimal WRITE training depends on correct READ data.

Figure 10 — Interface Training Sequence

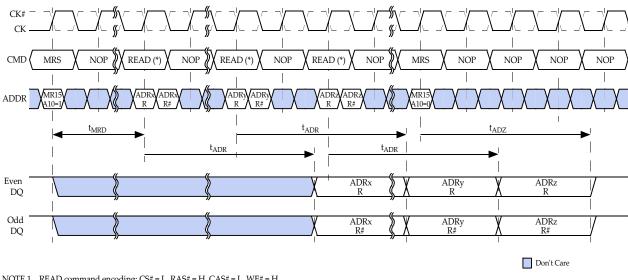

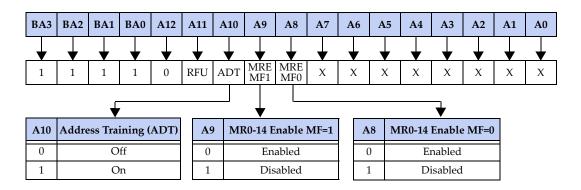

### 5.2 ADDRESS TRAINING

The GDDR5 SGRAM provides means for address bus interface training. The controller may use the address training mode to improve the timing margins on the address bus.

Address training mode is entered and exited via the ADT bit in Mode Register 15 (MR15). Mode Register 15 supports the same setup and hold times on the address pins as for commands to allow a safe entry into address training mode.

Address training mode uses an internal bridge between the GDDR5 SGRAM's address inputs and DQ/DBI# outputs. It also uses a special READ command for address capture that is encoded using the SDR command pins only (CS#,RAS#,CAS#,WE# = L,H,L,H). The address values normally used to encode the commands will not be interpreted. Once the address training mode has been entered, the address values registered coincident with this special READ command will be transmitted to the controller on the DQ/DBI# pins. The controller is then expected to compare the address pattern received to the expected value and to adjust the address transmit timing accordingly. The procedure may be repeated using different address pattern and interface timings.

No WCK clock is required for this special READ command operation during address training mode. The latched addresses are driven out asynchronously.

The only commands allowed during address training mode are this special READ, MRS (e.g. to exit address training mode) and NOP / DESELECT.

When enabled by the ABI bit in Mode Register 1, address bus inversion (ABI) is effective during address training mode. It is suggested to train the ABI# pin's interface timing together with the other address lines.

The timing diagram in Figure 11 illustrates the typical command sequence in address training mode. The DQ/DBI# output drivers are enabled as long as the ADT bit is set. The minimum spacing between consecutive special READ commands is 2 t<sub>CK</sub>.

NOTE 1 READ command encoding: CS# = L, RAS# = H, CAS# = L, WE# = H

NOTE 2 ADRxR = 1st half of address x, sampled on rising edge of CK;

$ADRxR\# = 2nd\ half\ of\ address\ x, sampled\ on\ rising\ edge\ of\ CK\# \\ NOTE\ 3\ Addresses\ sampled\ on\ rising\ edge\ of\ CK\ are\ returned\ on\ even\ DQ\ after\ tADR;$

addresses sampled on rising edge of CK# are returned on odd DQ simultaneously with even DQ NOTE 4 DQs are enabled when ADT bit in Mode Register 15 set to 1 (Enter Address Training Mode) DQs are disabled after  $t_{ADZ}$  when ADT bit in Mode Register 15 set to 0 (Exit Address Training Mode)

Figure 11 — Address Training Timing

# 5.2 ADDRESS TRAINING (cont'd)

Table 10 — AC timings in Address Training Mode

| Parameter                             | Symbol       | Min | Max             | Unit |

|---------------------------------------|--------------|-----|-----------------|------|

| READ command to data out delay        | $t_{ m ADR}$ | 0   | vendor specific | ns   |

| ADT off to DQ/DBI# in ODT state delay | $t_{ m ADZ}$ |     | vendor specific | ns   |

Table 11 defines the correspondence between address bits and DQ/DBI#. Devices configured to x16 mode reflect the address on the two bytes being enabled in that mode, which are bytes 0 and 2 for MF=0 and bytes 1 and 3 for MF=1 configurations. Devices configured to x32 mode reflect the address on the same DQ as in x16 mode; in addition they are allowed but not required to reflect the address on those bytes that are disabled in x16 mode, thus reflecting each address twice.

Devices not supporting an A12/RFU pin shall drive a logic High on the DBI# pins.

Table 11 — Address to DQ Mapping in Address Training Mode

| Output | Address bits registered at rising edge of CK  |      |      |      |      |      |      |      |     |

|--------|-----------------------------------------------|------|------|------|------|------|------|------|-----|

|        | A12                                           | A8   | A11  | BA1  | BA2  | BA3  | BA0  | A9   | A10 |

| DQ     | DBI0#                                         | DQ22 | DQ20 | DQ18 | DQ16 | DQ6  | DQ4  | DQ2  | DQ0 |

|        | DBI1#                                         | DQ30 | DQ28 | DQ26 | DQ24 | DQ14 | DQ12 | DQ10 | DQ8 |

|        |                                               |      |      |      |      |      |      |      |     |

| Output | Address bits registered at rising edge of CK# |      |      |      |      |      |      |      |     |

|        | RFU                                           | A7   | A6   | A5   | A4   | A3   | A2   | A1   | A0  |

| DQ     | DBI2#                                         | DQ23 | DQ21 | DQ19 | DQ17 | DQ7  | DQ5  | DQ3  | DQ1 |

|        | DBI3#                                         | DQ31 | DQ29 | DQ27 | DQ25 | DQ15 | DQ13 | DQ11 | DQ9 |

# 5.3 WCK2CK TRAINING

The purpose of WCK2CK training is to align the data WCK clock with the command CK clock to aid in the GDDR5 SGRAM's internal data synchronization between the logic clocked by CK/CK# and WCK/WCK#. This will help to define both Read and Write latencies between the GDDR5 SGRAM and memory controller. WCK2CK training mode is controlled via MRS.

Before starting WCK2CK training, the following conditions must be met:

- CK/CK# clock is stable and toggling

- The timing of all address and command pins must be guaranteed

- PLL on/off (MR1 bit A7) and PLL delay compensation enable (MR7 bit A2) are set to desired mode before WCK to CK training is started

- The desired WCK2CK alignment point (MR6, bit A0) is selected

- The EDC hold pattern (MR4, bits A0-A3) must be programmed to '1111'

- 2 Mode Register bits for internal WCK01 and WCK23 inversion (MR3, bits A2-A3) must be set to a known state

- All banks are idle and no other command execution is in progress

WCK2CK training must be done after any of the following conditions:

- Device initialization

- Any CLmrs, WLmrs, CRCRL or CRCWL latency change

- CK and WCK frequency changes

- PLL on/off (MR1 bit A7) and PLL delay compensation mode (MR7 bit A2) changes

- Change of the WCK2CK alignment point (MR6, bit A0)

- WCK state change from off to toggling, including self refresh exit or exit from power-down when bit A1 (LP2) in MR5 is set

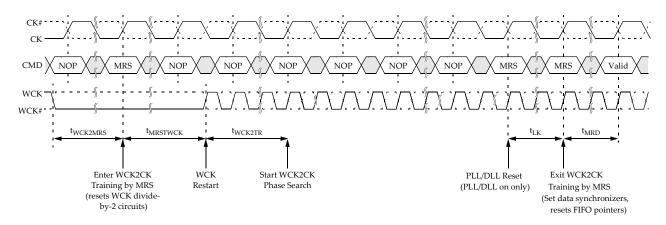

Figure 12 and Figure 13 show example WCK2CK training sequences. WCK2CK training is entered via MRS by setting bit A4 in MR3. This will initiate the WCK divide-by-2 circuits associated with WCK01 and WCK23 clocks in the GDDR5 SGRAM. In case the divide-by-2 circuits are at opposite output phases, which is indicated by opposite "early/late" phases on the EDC pins associated with WCK01 and WCK23 (see below), they may be put in phase by using the WCK01 and WCK23 inversion bits. Alternatively, the WCK clocks may be put into a stable inactive state for this initialization event to aid in resetting all dividers to the same output phase as shown in Figure 13. The challenge of this method is to restart the WCK clocks in a way that even their first clock edges meet the WCK clock input specification. Otherwise, divide-by-2 circuits for both WCK01 and WCK23 might again have opposite phase alignment.

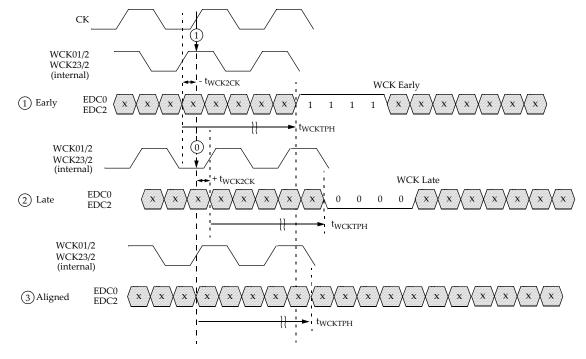

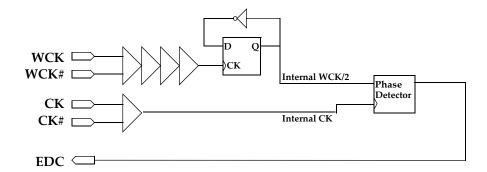

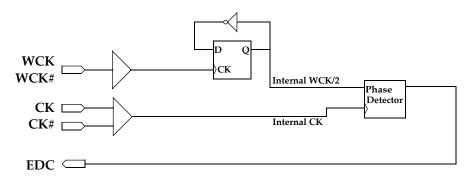

Figure 14 illustrates how the WCK phase information is derived. The phase detectors (PD) sample the internally divided-by-2 WCK clocks. Only one sample point is shown in the figure for clarity. In reality, when WCK2CK training mode is enabled, a sample will occur every  $t_{CK}$  and will be translated to the EDC pins accordingly. If the divided-by-2 WCK clock arrives early, then the EDC pin outputs the EDC hold pattern during the time interval specified in Figure 14. If the divided-by-2 WCK clock arrives late, then the EDC pin outputs the inverted EDC hold pattern during the time interval specified in Figure 14. This is shown in Table 12.

# CK CK# CMD NOP NOP NOP NOP NOP NOP NOP NOP MRS A.C. WCK WCK# Enter WCK2CK Training Start WCK2CK Phase Search PLL/DLL Reset (PLL/DLL on only) (sets data synchronizers, rests FIFO pointers)

Figure 12 — Example WCK2CK Training Sequence

Figure 13 — Example WCK2CK Training Sequence with WCK Stopping

Figure 14 — EDC pin Behaviour for WCK2CK Training (assumes '1111' as EDC Hold Pattern)

Table 12 — Phase Detector and EDC Pin behavior

| WCK/2 value sampled by CK | WCK2CK Phase | Data on EDC Pin            | Action                |  |  |

|---------------------------|--------------|----------------------------|-----------------------|--|--|

| ′1′                       | 'Early'      | EDC hold ('1111')          | Increase Delay on WCK |  |  |

| ′0′                       | 'Late'       | Inverted EDC Hold ('0000') | Decrease Delay on WCK |  |  |

The ideal alignment is indicated by the phase detector output transitioning from "early" to "late" when the delay of the WCK phase is continuously increased. The WCK phase range for ideal alignment is specified by the parameter t<sub>WCK2CKPIN</sub> in the vendor's datasheet; the value(s) vary with the PLL/DLL mode (on or off) and the selected alignment point.

If enabled, the PLL/DLL shall not interfere in the behavior of the WCK2CK training. Significantly moving the phase and/or stopping the WCK during training may disturb the PLL/DLL. It is required to perform a PLL/DLL reset after the WCK2CK training has determined and selected the proper alignment between WCK and CK clocks. The PLL/DLL lock time  $t_{\rm LK}$  must be met before exiting WCK2CK training to guarantee that the PLL/DLL is in lock such that the GDDR5 SGRAM data synchronizers are set upon WCK2CK training exit.

WCK2CK training is exited via MRS by resetting bit A4 in MR3. For proper reset of the data synchronizers it is required that the WCK and CK clocks are aligned within t<sub>WCK2CKSYNC</sub> at the time of the WCK2CK training exit.

After exiting WCK2CK training mode, the WCK phase is allowed to further drift from the ideal alignment point by a maximum of  $t_{WCK2CK}$  (e.g. due to voltage and temperature variation). Once this WCK phase drift exceeds  $t_{WCK2CK}$ (min) or  $t_{WCK2CK}$ (max), it is required to repeat the WCK2CK training and realign the clocks.

# WCK2CK alignment at PIN Mode (optional)

The WCK and CK phase alignment point can be changed via MRS by setting bit A0 in MR6. In normal mode, when MR6 A0 is set to '0', the phases of CK and WCK are aligned at CK pins and the end of WCK tree as shown in Figure 15. On the other hand, when MR6 A0 is set to '1', the phases of CK and WCK are aligned at the pin as shown in Figure 16. PIN mode is supported up to the max CK clock frequency of  $f_{\text{CKPIN}}$ , and is an option to reduce the time of WCK2CK training at low frequency.

Figure 15 — Normal Mode

Figure 16 — Pin Mode (optional)

# WCK2CK Auto Synchronization (Optional)

GDDR5 SGRAMs may optionally support a WCK2CK automatic synchronization mode that eliminates the need for WCK2CK training upon power-down exit. This mode is controlled by the autosync bit (MR7, bit A4), and is effective when the LP2 bit (MR5, bit A1) is set and the WCK clocks are stopped during power-down. Also, this mode works for both normal and PIN mode. When WCK2CK automatic synchronization mode is enabled, a full WCK2CK training including Phase search is not required after power-down exit, although WCK2CK MRS must be issued momentarily for setting the data synchronizers. However, WCK and CK clocks must meet the  $t_{WCK2CKSYNC}$  specification upon power-down exit. Any allowed command may be issued after  $t_{XPN}$  or after  $t_{LK}$  in case the PLL/DLL had been enabled upon power-down entry. The PLL/DLL sequence is not affected by this mode. The use of WCK2CK automatic synchronization mode is restricted to lower operating frequencies up to  $t_{CKAUTOSYNC}$  as described in vendor's datasheets.

Table 13 describes WCK2CK training methods for different frequency ranges. Each Frequency range is vendor specific. Normal and PIN mode of WCK2CK training are described in Table 13. Each frequency range is DRAM vendor specific. Divider initialization can be done by training with WCK2CK inversion, WCK2CK stopping, or WCK2CK auto-sync. If the user wants to use WCK2CK stop for divider initialization instead of WCK2CK auto-sync, the user must not set the WCK2CK auto-sync. Below middle frequency, the combined use of PIN and WCK2CK auto-sync modes can minimize WCK2CK training time.

Table 13 — An example of WCK2CK training simplified for Normal mode and PIN mode

|                             | High Frequency<br>(i.e. 5Gbps) |          | Middle Frequency<br>(i.e. 2Gbps) |     | Low Frequency<br>(i.e. 400Mbps) |     |  |

|-----------------------------|--------------------------------|----------|----------------------------------|-----|---------------------------------|-----|--|

| Frequency (Vendor Specific) |                                |          |                                  |     |                                 |     |  |

| WCK2CK alignment mode       | Normal                         | PIN      | Normal                           | PIN | Normal                          | PIN |  |

| Phase Search                | Required                       | Required | Required                         | No* | No*                             | No* |  |

<sup>\*</sup> Note: The divided WCK/WCK# should be aligned CK/CK# by WCK2CK Auto Synchronization or WCK stop mode

The following examples describe the WCK2CK training in more detail.

Example 1: outline of a basic WCK2CK training sequence without WCK clock stop:

- 1) Enable training mode via MRS and wait  $t_{MRD}$

- 2) Sweep and observe the phase independently for WCK01 on EDC0 and WCK23 on EDC2; in case the internal divide-by-2 circuits are at opposite phase use either the WCK01 or WCK23 inversion bit to flip one of the WCK divide-by-2 circuits

- 3) Adjust the WCK phase independently for WCK01 and WCK23 to the optimal point ("ideal alignment")

- 4) Issue a PLL/DLL reset and wait for t<sub>LK</sub> (PLL/DLL on mode only)

- 5) While all WCK and CK are aligned, exit WCK2CK training mode via MRS

- 6) Wait t<sub>MRD</sub> for the reset of data synchronizers

Example 2: outline of a basic WCK2CK training sequence with optional WCK clock stop:

- 1) Stop WCK clocks with WCK01/WCK23 LOW and WCK01#/WCK23# HIGH

- 2) Wait t<sub>WCK2MRS</sub> for internal WCK clocks to settle

- 3) Enable training mode via MRS and wait t<sub>MRD</sub> for divide-by-2 circuits to reset

- 4) Start WCK clocks without glitches (both divide-by-2 circuits remain in sync)

- 5) Wait t<sub>WCK2TR</sub> for internal WCK clocks to stabilize

- 6) Sweep and observe the phase independently for WCK01 on EDC0 and WCK23 on EDC2; adjust the WCK phase to the optimal point ("ideal alignment")

- 7) Issue a PLL/DLL reset and wait t<sub>LK</sub> (PLL/DLL on mode only)

- 8) While all WCK and CK are aligned, exit WCK2CK training mode via MRS

- 9) Wait t<sub>MRD</sub> for the reset of data synchronizers

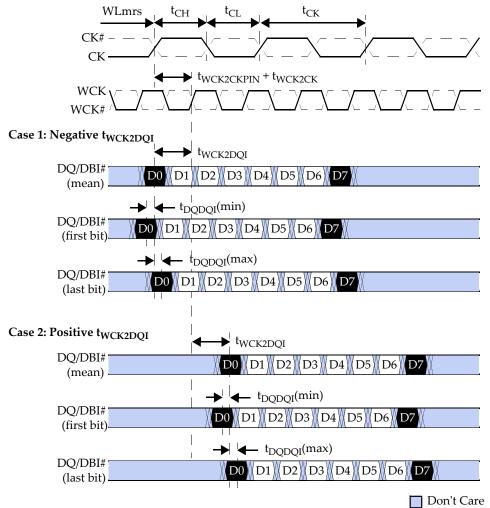

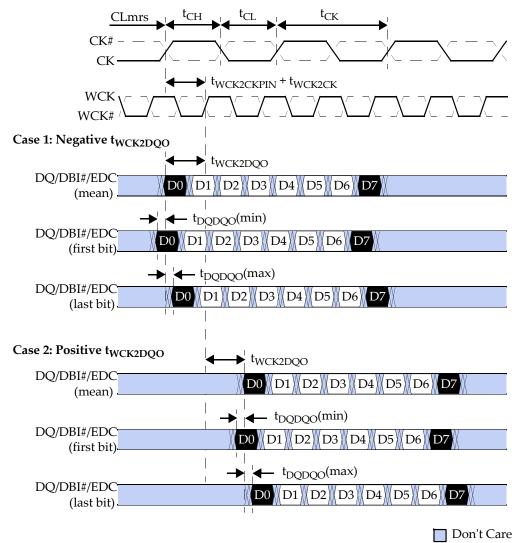

READ and WRITE latency timings are defined relative to CK. Any offset in WCK and CK at the pins and/or the phase detector will be reflected in the latency timings. The parameters used to define the relationship between WCK and CK are shown in Figure 17. For more details on the impact on READ and WRITE timings see the OPERATIONS section.

Note t<sub>WCK2CKPIN</sub> and t<sub>WCK2CK</sub> parameter values could be negative or positive numbers, depending on the selected WCK2CK alignment point, PLL-on-or PLL-off mode operation and design implementation. They also vary across PVT. WCK2CK training is required to determine the correct WCK-to-CK phase for stable device operation.

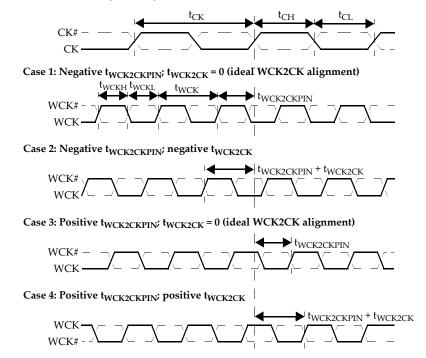

# Figure 17 — WCK2CK Timings

# GDDR5 WCK2CK Training in x16 mode

For configurations with WCK clocks not shared between two GDDR5 SGRAMs it is suggested to set the WCK phase to the ideal alignment point. However, for configurations where two GDDR5 SGRAMs (x16) share their WCK clocks as in a x16 clamshell, an offset given by the midpoint of both DRAM's ideal WCK positions may be required. The maximum allowed offset in this case is specified by parameter t<sub>WCK2CKSYNC</sub>: it defines the WCK offset range from the ideal alignment which still guarantees a GDDR5 SGRAM device to internally synchronize its WCK and CK clocks upon training exit.

Example: outline of training sequence for x32 and x16 configurations with 2 GDDR5 SGRAMs sharing their WCK clocks (e.g. clamshell):

- 1) Enable training mode for both DRAMs via MRS and wait t<sub>MRD</sub>

- 2) For both DRAMs sweep and observe the phase independently for WCK01 on EDC0 and WCK23 on EDC2; in case the internal divide-by-2 circuits are at opposite phases use either the WCK01 or WCK23 inversion bit to flip one of the WCK divide-by-2 circuits; in case of shared CS# signals use MREMF0 and MREMF1 bits in MR15 to explicitly direct the MRS command for this phase flipping to either DRAM1 or DRAM2 ("soft chip select");

- 3) Sweep and observe the phase on DRAM1 independently for WCK01 on EDC0 and WCK23 on EDC2; store the setting for the optimal WCK phase

- 4) Sweep and observe the phase on DRAM2 independently for WCK01 on EDC0 and WCK23 on EDC2; store the setting for the optimal WCK phase

- 5) Sweep WCK01 and WCK23 phase to midpoint of DRAM1 and DRAM2 optimal settings

- 6) Issue a PLL/DLL reset and wait for t<sub>LK</sub> (PLL/DLL on mode only)

- 7) While all WCK and CK are aligned, exit WCK2CK training mode via MRS

- 8) Wait t<sub>MRD</sub> for the reset of data synchronizers

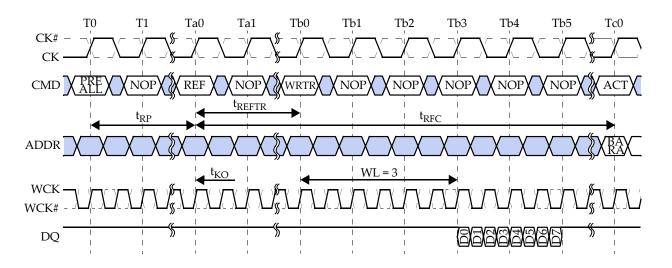

# 5.4 READ TRAINING

Read training allows the memory controller to find the data-eye center (symbol training) and burst frame location (frame training) for each high-speed output of the GDDR5 SGRAM. Each pin (DQ0-DQ31, DBI0#-DBI3#, EDC0-EDC3) can be individually trained during this sequence.

For Read Training the following conditions must be true:

- at least one bank is active, or an auto refresh must be in progress and bit A2 in Mode Register 5 (MR5) is set to 0 to allow training during auto refresh (to disable this special REF enabling of the WCK clock tree an ACT command must be issued, or the device must be set into power-down or self refresh mode)

- WCK2CK training must be complete

- the PLL/DLL must be locked, if enabled

- RDBI and WDBI must be enabled prior to and during Read Training if the training shall include the DBI# pins. RDCRC and WRCRC must be enabled prior to and during Read Training if the training shall include the EDC pins.

The following commands are associated with Read Training:

- LDFF to preload the Read FIFO;

- RDTR to read a burst of data directly out of the Read FIFO.

Neither LDFF nor RDTR access the memory core. No MRS is required to enter Read Training.

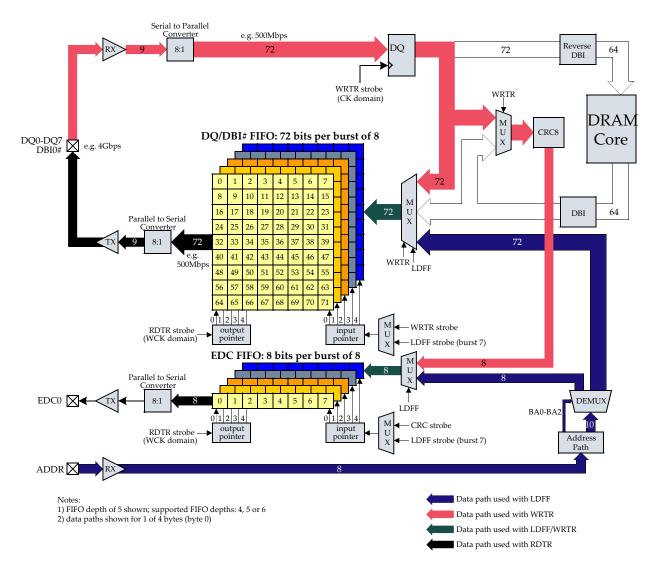

Figure 18 shows an example of the internal data paths used with LDFF and RDTR. Table 14 lists AC timing parameters associated with Read Training.

| PARAMETER                             | SYMBOL              | VAI | UNIT | NOTES           |       |

|---------------------------------------|---------------------|-----|------|-----------------|-------|

| TARAMETER                             |                     | MIN | MAX  | ONII            | NOTES |

| ACTIVE to LDFF command delay          | t <sub>RCDLTR</sub> |     | _    | ns              |       |

| ACTIVE to RDTR command delay          | t <sub>RCDRTR</sub> |     | _    | ns              |       |

| REFRESH to RDTR or WRTR command delay | t <sub>REFTR</sub>  |     | _    | ns              |       |

| RDTR to RDTR command delay            | t <sub>CCDS</sub>   |     | _    | $t_{CK}$        |       |

| LDFF to LDFF command cycle time       | t <sub>LTLTR</sub>  | 4   | _    | t <sub>CK</sub> |       |

| LDFF(111) to LDFF command cycle time  | t <sub>LTL7TR</sub> |     | _    | t <sub>CK</sub> | 1     |

| LDFF(111) to RDTR command delay       | t <sub>LTRTR</sub>  |     | _    | $t_{CK}$        |       |

$t_{RDTLT}$

$t_{CK}$

Table 14 — LDFF and RDTR TIMINGS

READ or RDTR to LDFF command delay

<sup>1.</sup> The min. value is vendor specific and does not exceed 8  $t_{\mbox{CK}}$ .

Figure 18 — Data Paths used for Read and Write Training

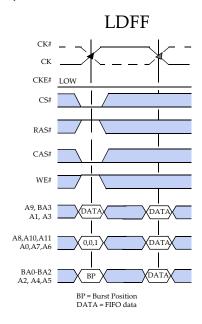

# LDFF Command

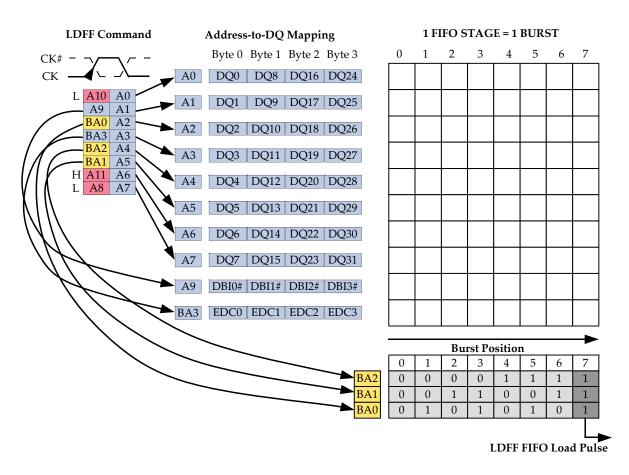

The LDFF command (Figure 19) is used to securely load data to the GDDR5 SGRAM Read FIFOs via the address bus. Depending on the GDDR5 SGRAM READ FIFO depth nFIFO (4-6), any bit pattern of length 32-48 can be loaded uniquely to every DQ, DBI# and EDC pin within a byte. The FIFO depth is fixed by design and can be read via the Vendor ID function.

Eight LDFF commands are required to fill one FIFO stage; each LDFF command loads one burst position, and the bank addresses BA0-BA2 select the burst position from 0 to 7.

The data pattern is conveyed on address pins A0-A7 for DQ0-DQ7, A9 for DBI0#, and BA3 for EDC0; the data are internally replicated to all 4 bytes, as shown in Figure 20.

LDFF loads the DBI FIFO regardless of the WDBI and RDBI Mode Register bits. It also loads the EDC FIFO regardless of the WRCRC and RDCRC Mode Register bits, and no CRC is calculated; however, RDBI and RDCRC must be enabled to read the DBI and EDC bits, respectively, with the RDTR command.

Figure 19 — LDFF Command

Figure 20 — LDFF Command Address to DQ/DBI#/EDC Mapping

All burst addresses 0 to 7 must be loaded; LDFF commands to burst address 0 to 6 may be issued in random order; the LDFF command to burst address 7 (LDFF7) must be the last of 8 consecutive LDFF commands, as it effectively loads the data into the FIFO and results in a FIFO pointer increment. Consecutive LDFF commands have to be spaced by at least  $t_{LTLTR}$ , and at least  $t_{LTLTR}$  cycles are required after each LDFF command to burst address 7.

LDFF pattern may efficiently be replicated to the next FIFO stages by issuing consecutive LDFF commands to burst address 7 (with identical data pattern). The data pattern in the scratch memory for LDFF will be available until the first RDTR command.

The DQ/DBI# output buffers remain in ODT state during LDFF.

An amount of LDFF commands to burst address 7 greater than the FIFO depth is allowed and shall result in a looping of the FIFO's data input.

The total number of LDFF commands to burst address 7 modulo FIFO depth must equal the total number of RDTR commands modulo FIFO depth when used in conjunction with RDTR. No READ or WRITE commands are allowed between LDFF and RDTR.

The EDC hold pattern is driven on the EDC pins during LDFF (provided RDQS mode is not enabled).

### **RDTR Command**

A RDTR burst is initiated with a RDTR command as shown in Figure 21. No bank or column addresses are used as the data is read from the internal READ FIFO, not the array. The length of the burst initiated with a RDTR command is eight. There is no interruption nor truncation of RDTR bursts.

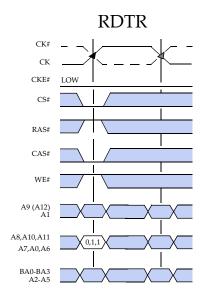

Figure 21 — RDTR Command

A RDTR command may only be issued when a bank is open or a refresh is in progress and bit A2 in MR5 is set to 0 to allow training during refresh.

RDBI and RDCRC must be enabled to read the DBI and EDC bits, respectively, with the RDTR command. If not set, the DBI# pins will remain in ODT state, and the EDC pins will drive the EDC hold pattern.

In case of the RDQS mode, the EDC pin functions like with a normal READ in this mode. The DBI# pin behaves like a DQ, and no encoding with DBI is performed.

An amount of RDTR commands greater than the FIFO depth is allowed and shall result in a looping of the FIFO's data output. The FIFO depth from which the RDTR data is read must be a number between 4-6 and must be specified by the DRAM vendor. The FIFO depth is read via the Vendor ID function.

During RDTR bursts, the first valid data-out element will be available after the CAS latency (CL). The latency is the same as for READ. The data on the EDC pins comes with additional CRC latency (t<sub>CRCRD</sub>) after the CL.

Upon completion of a burst, assuming no other RDTR command has been initiated, all DQ and DBI# pins will drive a value of '1' and the ODT will be enabled at a maximum of 1  $t_{CK}$  later. The drive value and termination value may be different due to separately defined calibration offsets. If the ODT is disabled, the pins will drive Hi-Z.

Data from any RDTR burst may be concatenated with data from a subsequent RDTR command. A continuous flow of data can be maintained. The first data element from the new burst follows the last element of a completed burst. The new RDTR command should be issued after the first RDTR command according to the  $t_{CCDS}$  timing.

A WRTR can be issued any time after a RDTR command as long as the bus turn around time t<sub>RTW</sub> is met.

The total number of RDTR commands modulo FIFO depth must be equal to total number of WRTR commands modulo FIFO depth when used in conjunction with WRTR. No READ or WRITE commands are allowed between WRTR and RDTR.

The total number of RDTR commands modulo FIFO depth must be equal to the total number of LDFF commands to burst position 7 modulo FIFO depth when used in conjunction with LDFF. No READ or WRITE commands are allowed between LDFF and RDTR.

#### 5.5 WRITE TRAINING

Write training allows the memory controller to find the data-eye center (symbol training) and burst frame location (frame training) for each high-speed input of the GDDR5 SGRAM. Each pin (DQ0-DQ31, DBI0#-DBI3#) can be individually trained during this sequence.

For Write Training the following conditions must be true:

- at least one bank is active, or an auto refresh must be in progress and bit A2 in Mode Register 5 (MR5) is set to 0 to allow training during auto refresh (to disable this special REF enabling of the WCK clock tree an ACT command must be issued, or the device must be set into power-down or self refresh mode)

- the PLL/DLL must be locked, if enabled.

- WCK2CK training should be complete

- Read training should be complete

- RDBI and WDBI must be enabled prior to and during Write Training if the training shall include the DBI# pins. RDCRC and WRCRC must be enabled prior to and during Write Training if the training shall include the EDC pins.

The following commands are associated with Write Training:

- WRTR to write a burst of data directly into the Read FIFO;

- RDTR to read a burst of data directly out of the Read FIFO.

Neither WRTR nor RDTR access the memory core. No MRS is required to enter Write Training.

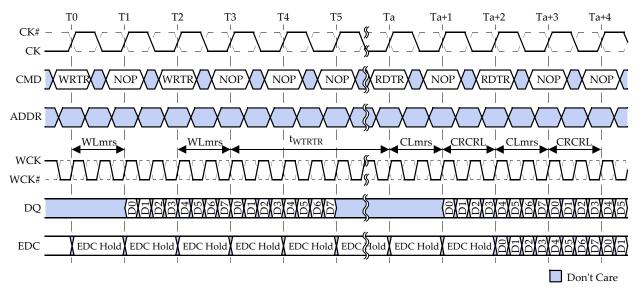

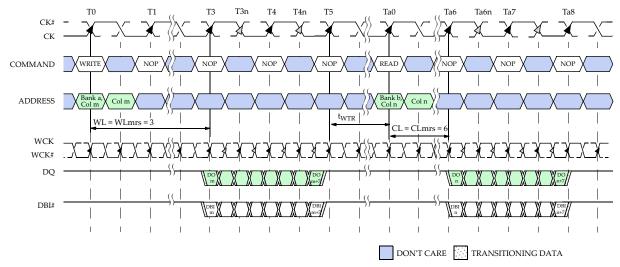

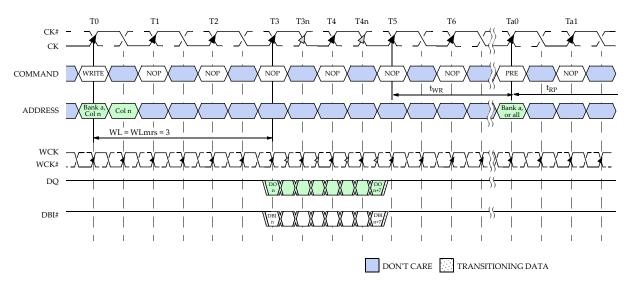

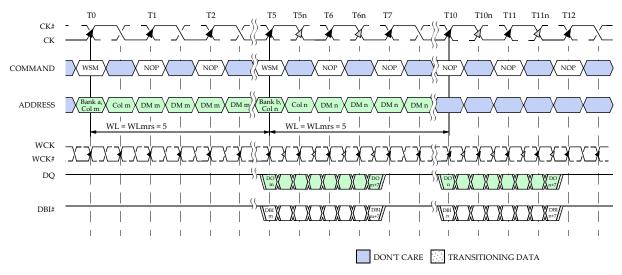

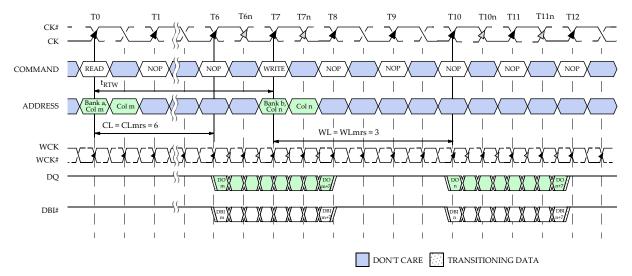

Figure 18 shows an example of the internal data paths used with WRTR and RDTR. Figure 23 shows a typical Write training command sequence using WRTR and RDTR. Table 15 lists AC timing parameters associated with WRITE Training.

| PARAMETER                                                        | SYMBOL              | VAI | UNIT | NOTES           |       |

|------------------------------------------------------------------|---------------------|-----|------|-----------------|-------|

| TARAMETER                                                        | SIMBOL              | MIN | MAX  | UNII            | NOTES |

| ACTIVE to WRTR command delay                                     | t <sub>RCDWTR</sub> |     | _    | ns              |       |

| ACTIVE to RDTR command delay                                     | t <sub>RCDRTR</sub> |     | _    | ns              |       |

| REFRESH to RDTR or WRTR command delay                            | t <sub>REFTR</sub>  |     | _    | ns              |       |

| RD/WR bank A to RD/WR bank B command delay different bank groups | t <sub>CCDS</sub>   |     | _    | t <sub>CK</sub> | 1     |

| WRTR to RDTR command delay                                       | t <sub>WTRTR</sub>  |     | -    | t <sub>CK</sub> |       |

| WRITE to WRTR command delay                                      | t <sub>WRWTR</sub>  |     | -    | t <sub>CK</sub> |       |

| READ or RDTR to WRITE or WRTR command delay                      | t <sub>RTW</sub>    |     | _    | ns              | 2     |

Table 15 — WRTR and RDTR Timings

t<sub>CCDS</sub> is either for gapless consecutive READ or RDTR (any combination), gapless consecutive WRITE, or gapless consecutive WRTR commands

t<sub>RTW</sub> is not a device limit but determined by the system bus turnaround time. The difference between t<sub>WCK2DQO</sub> and t<sub>WCK2DQI</sub> shall be considered in the calculation of the bus turnaround time.

# 5.5 WRITE TRAINING (cont'd)

#### **WRTR Command**

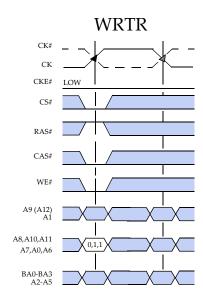

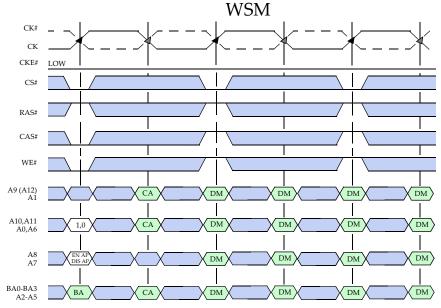

A WRTR burst is initiated with a WRTR command as shown in Figure 22. No bank or column addresses are used as the data is written to the internal READ FIFO, not the array. The length of the burst initiated with a WRTR command is eight. There is no interruption nor truncation of WRTR bursts.

Figure 22 — WRTR Command

A WRTR command may only be issued when a bank is open or a refresh is in progress and bit A2 in MR5 is set to 0 to allow training during refresh.

WDBI and WRCRC must be enabled to write the DBI and EDC bits, respectively, with the WRTR command. If WDBI is not set, a '1' will be written to the DBI FIFO, and a '1' will be assumed for the DBI# input in the CRC calculation. In contrast to a normal WRITE, no CRC is returned by the WRTR command and the EDC pins will drive the EDC hold pattern.

In case of the RDQS mode, the EDC pin functions like with a normal READ in this mode. Please note that RDCRC must be enabled to read the calculated CRC data with the RDTR command.

An amount of WRTR commands equal to the FIFO depth is required to fully load the FIFO; any number of WRTR commands greater than the FIFO depth is allowed and shall result in a looping of the FIFO's data input. The FIFO depth to which the WRTR data is written must be a number between 4-6 and must be specified by the DRAM vendor. The FIFO depth is read via the Vendor ID function.

During WRTR bursts, the first valid data-in element must be available at the input latch after the Write Latency (WL). The Write Latency is the same as for WRITE.

Upon completion of a burst, assuming no other WRTR data is expected on the bus the GDDR5 SGRAM DQ and DBI# pins will be driven according to the ODT state. Any additional input data will be ignored.

# 5.5 WRITE TRAINING (cont'd)

Data from any WRTR burst may be concatenated with data from a subsequent WRTR command. A continuous flow of data can be maintained. The first data element from the new burst follows the last element of a completed burst. The new WRTR command should be issued after the previous WRTR command according to the  $t_{\text{CCDS}}$  timing.

A RDTR can be issued any time after a WRTR command as long as the internal bus turn around time  $t_{RTWTR}$  is met.

The total number of WRTR commands modulo FIFO depth must equal the total number of RDTR commands modulo FIFO depth when used in conjunction with RDTR. No READ or WRITE commands are allowed between WRTR and RDTR.

<sup>1.</sup> WLmrs, CLmrs and CRCRL set to 1 for ease of illustration; check Mode Register definition for supported settings

Figure 23 — Write Training using WRTR and RDTR Commands

<sup>2.</sup> WCK and CK are shown aligned ( $t_{WCK2CKPIN}$ =0,  $t_{WCK2CK}$ =0) for illustration purposes. WCK2CK training determines the needed offset between WCK and CK.

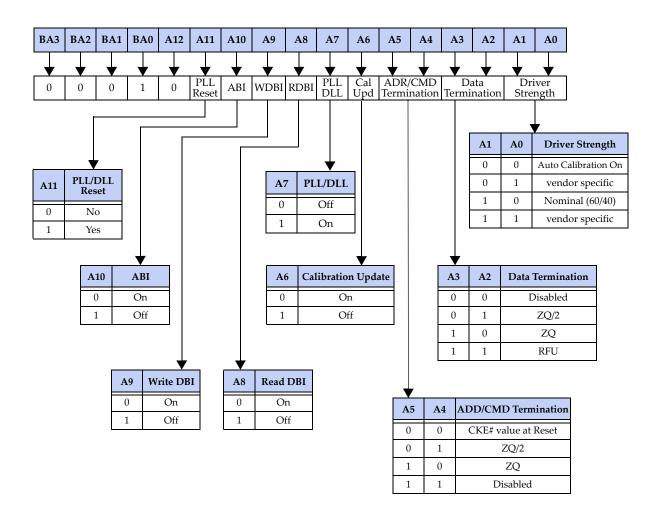

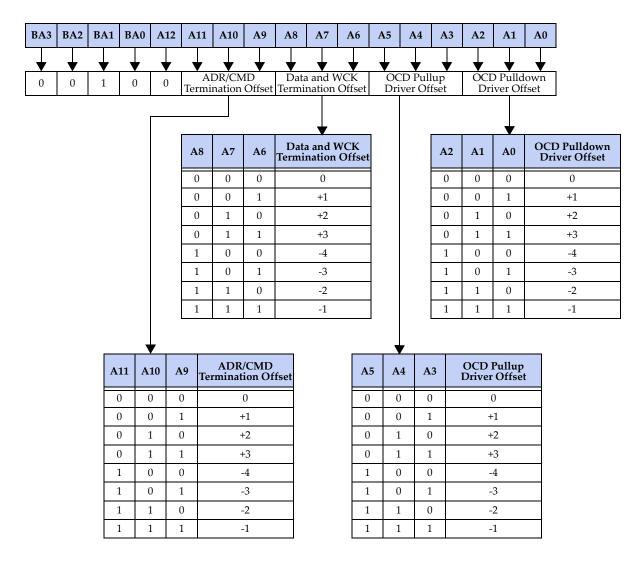

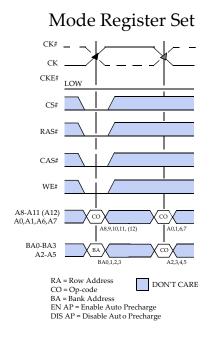

#### 6 MODE REGISTERS

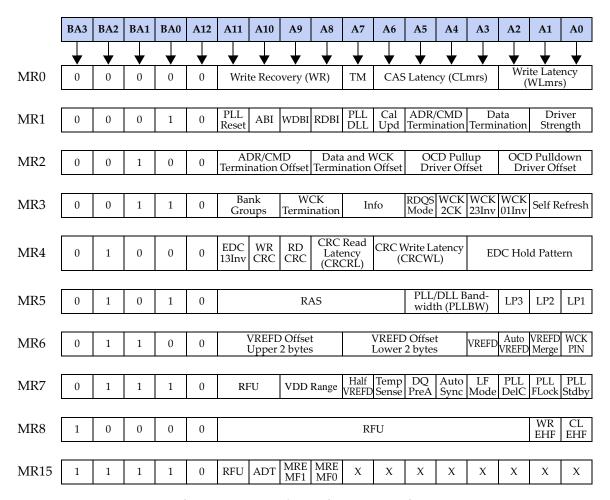

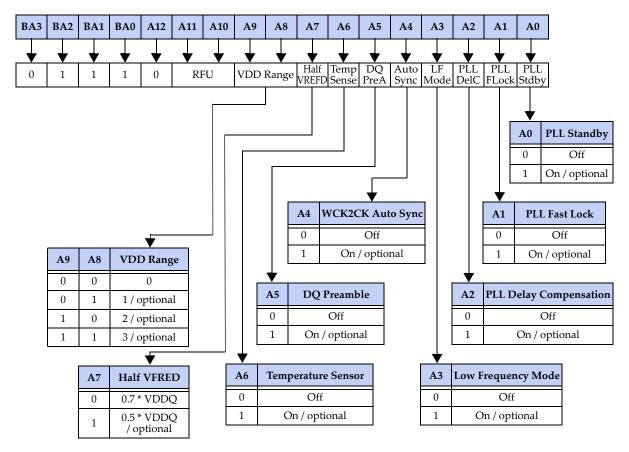

GDDR5 specifies 10 Mode Registers to define the specific mode of operation. MR0 to MR8 and MR15 are defined as shown in the overview in Figure 24. MR9 to MR14 are not defined and may be used by DRAM vendors for vendor specific features. Reprogramming the Mode Registers will not alter the contents of the memory array.

All Mode Registers are programmed via the MODE REGISTER SET (MRS) command and will retain the stored information until they are reprogrammed or the device loses power. Mode Registers must be loaded when all banks are idle and no bursts are in progress, and the controller must wait the specified time  $t_{MRD}$  before initiating any subsequent operation. Violating either of these requirements will result in unspecified operation.

No default states are defined for Mode Registers except when otherwise noted. Users therefore must fully initialize all Mode Registers to the desired values e.g. upon power-up.

Reserved states should not be used, as unknown operation or incompatibility with future versions may result. RFU bits are reserved for future use and must be programmed to 0. Bit A12 is not used for any mode register programming as this address input is not defined for 512M and 1G densities.

If the user activates bits in an optional field, either the optional field is activated (if option is implemented in the device) or no action is taken by the device (if option is not implemented).

# 6 MODE REGISTERS (cont'd)

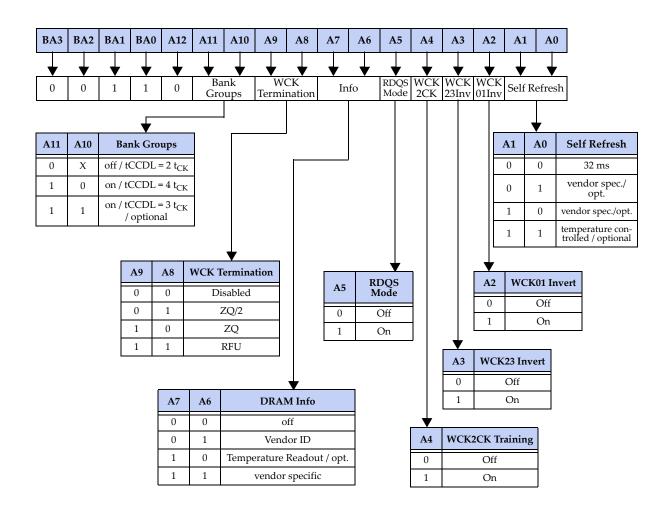

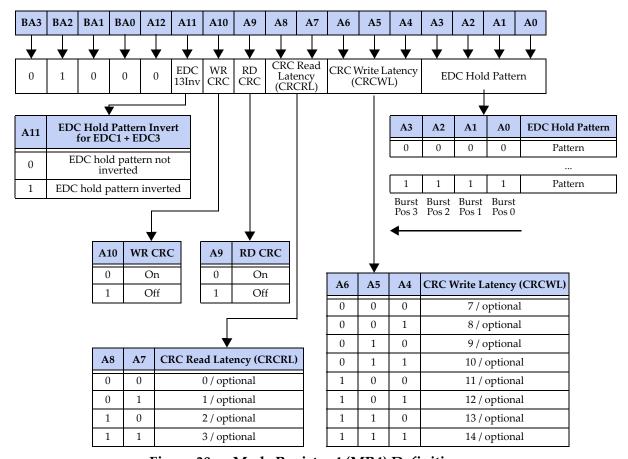

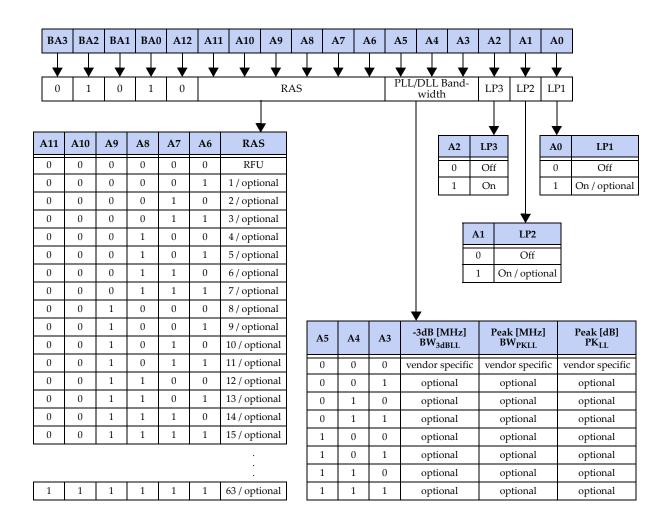

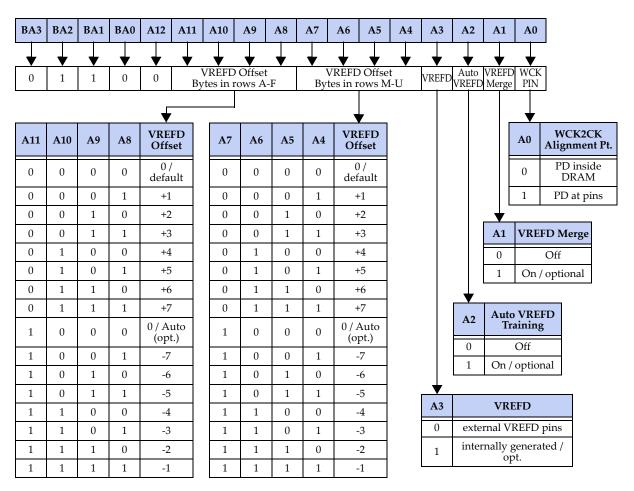

Figure 24 — Mode Registers Overview

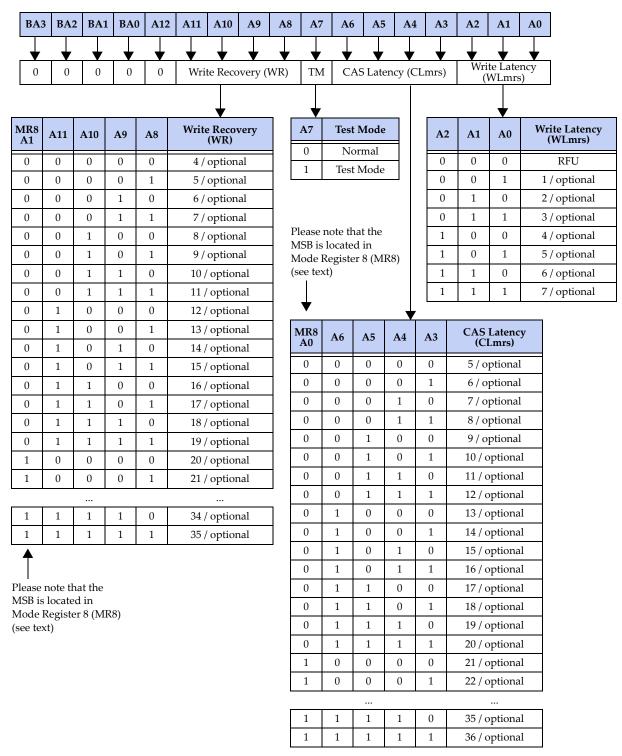

# 6.1 MODE REGISTER 0 (MR0)

Mode Register 0 controls operating modes such as Write Latency, CAS latency, Write Recovery and Test Mode as shown in Figure 25. The register is programmed via the MODE REGISTER SET (MRS) command with BA0=0, BA1=0, BA2=0 and BA3=0.

Figure 25 — Mode Register 0 (MR0) Definition

#### 6.1 MODE REGISTER 0 (MR0) (cont'd)

### WRITE Latency (WLmrs)

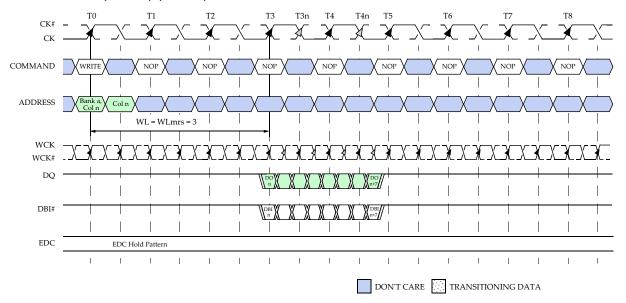

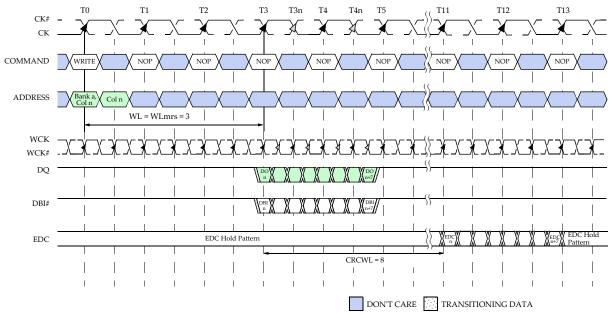

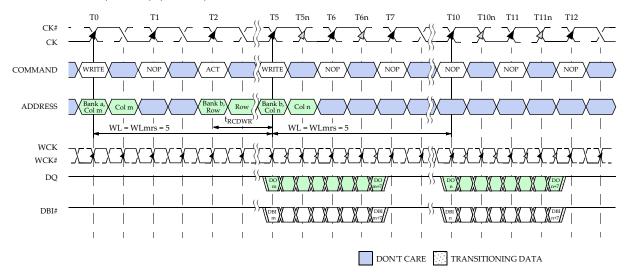

The WRITE latency (WLmrs) is the delay in clock cycles used in the calculation of the total WRITE latency (WL) between the registration of a WRITE command and the availability of the first piece of input data. DRAM vendor specifications should be checked for value(s) of WLmrs supported. The full WRITE latency definition can be found in the section entitled OPERATION.

When the WRITE latencies are set to small values (i.e. 1,2,... clocks), the input receivers never turn off, in turn, raising the operating power. When the WRITE latency is set to higher values (i.e. .. 6, 7 clocks) the input receivers turn on when the WRITE command is registered. Refer to vendor datasheets for value(s) of WLmrs where the input receivers are always on or only turn on when the WRITE command is registered.

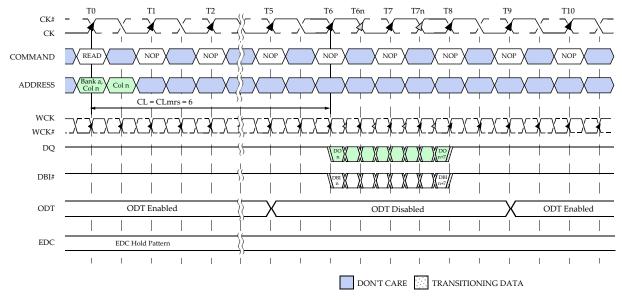

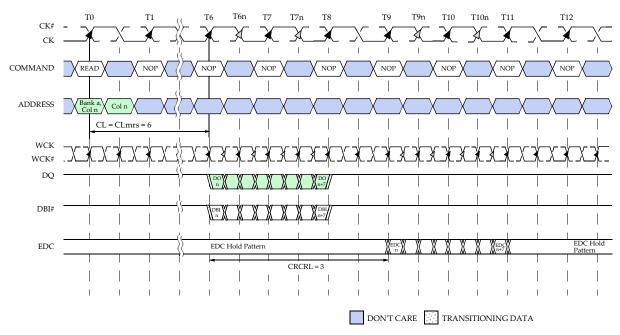

# CAS Latency (CLmrs)

The CAS latency (CLmrs) is the delay in clock cycles used in the calculation of the total READ latency (CL) between the registration of a READ command and the availability of the first piece of output data.

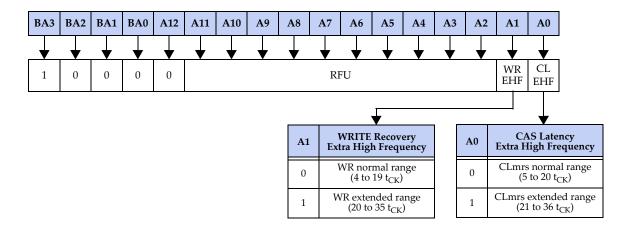

By default CLmrs is specified by bits A3-A6, defining a CLmrs range of 5 to 20 t<sub>CK</sub>.

For higher frequencies, the CLmrs range may optionally be expanded by the CLEHF bit located in Mode Register 8 (MR8). With the addition of the CLEHF bit a CLmrs range of 5 to 36  $t_{CK}$  is defined. Please note that with the presence of the CLEHF bit a change of the CAS latency may require two MRS commands.

DRAM vendor specifications should be checked for value(s) of CLmrs supported. The full READ latency definition can be found in the section entitled OPERATION.

#### WRITE Recovery (WR)

The programmed WR value is used for the auto precharge feature along with  $t_{RP}$  to determine  $t_{DAL}$ . The WR register bits are not a required function and may be implemented at the discretion of the DRAM manufacturer.

WR must be programmed with a value greater than or equal to  $RU\{t_{WR}/t_{CK}\}$ , where RU stands for round up,  $t_{WR}$  is the analog value from the vendor datasheet and  $t_{CK}$  is the operating clock cycle time.

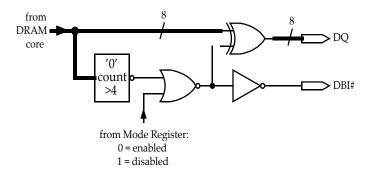

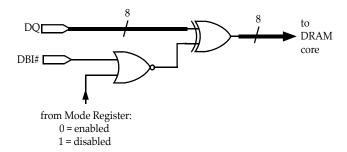

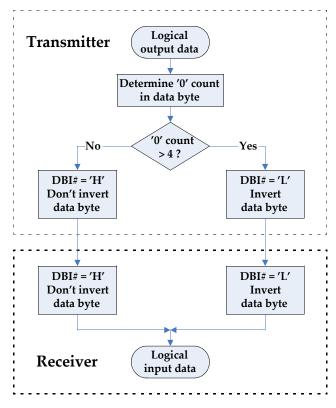

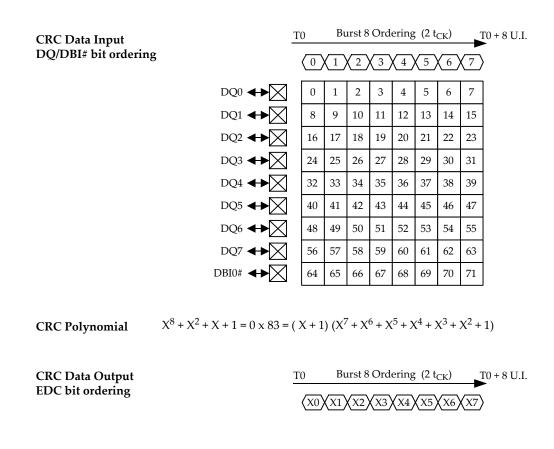

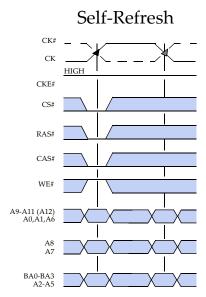

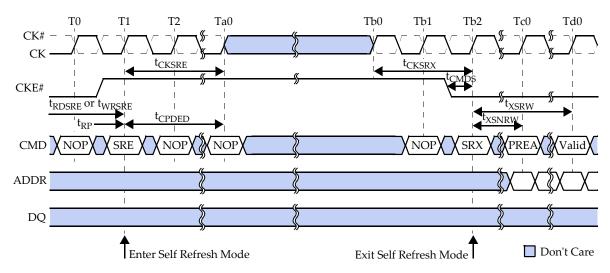

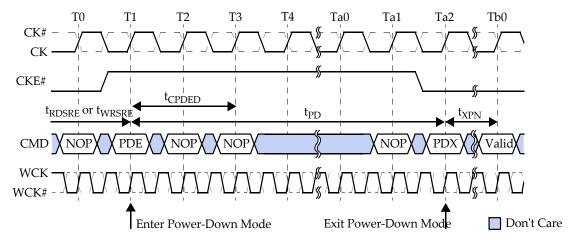

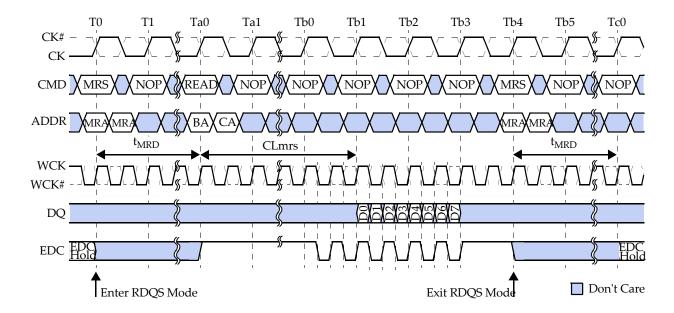

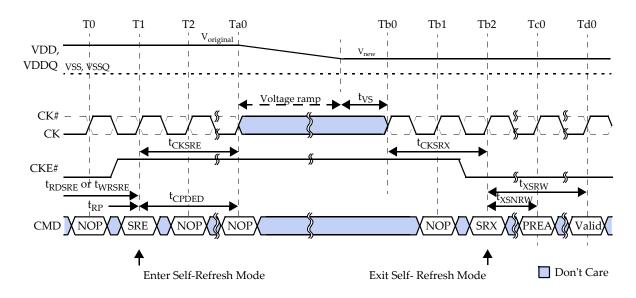

By default WR is specified by bits A8-A11, defining a WR range of 4 to 19 t<sub>CK</sub>.