# 128-Bit SSE5 Instruction Set

| Publication No. | Revision | Date        |

|-----------------|----------|-------------|

| 43479           | 3.00     | August 2007 |

Advanced Micro Devices 🛛 🛃

© 2007 Advanced Micro Devices, Inc. All rights reserved.

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. The information contained herein may be of a preliminary or advance nature and is subject to change without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

#### Trademarks

AMD, the AMD Arrow logo, and combinations thereof are trademarks of Advanced Micro Devices, Inc. MMX is a trademark of Intel Corporation.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

# Contents

| Revisio | on Hist | ory                                                 | xi  |

|---------|---------|-----------------------------------------------------|-----|

| Prefac  | e       |                                                     | iii |

| 1       | New 1   | 28-Bit Instructions                                 | .1  |

| 1       | 1.1     | New 128-Bit Media Instruction Format                |     |

|         | 1.1     | Four-Operand 128-Bit Media Instructions             |     |

|         | 1.2     | Three-Operand 128-Bit Media Instructions            |     |

|         | 1.3     | Other 128-Bit Media Instructions                    |     |

|         | 1.4     | 16-Bit Floating-Point Data Type                     |     |

|         | 1.6     | Floating Point Multiply and Add/Subtract            |     |

|         | 1.7     | Integer Multiply (Add) and Accumulate Instructions  |     |

|         | 1.8     | Packed Integer Horizontal Add and Subtract          |     |

|         | 1.9     | Vector Conditional Moves.                           |     |

|         | 1.10    | Packed Integer Rotates and Shifts                   |     |

|         | 1.11    | Floating Point Comparison and Predicate Generation. |     |

|         | 1.12    | Test Instruction                                    |     |

|         | 1.12    | Precision Control and Rounding                      |     |

|         | 1.14    | Convert                                             |     |

| 2       | SSE5 1  | 128-Bit Media Instructions                          | 17  |

|         | 2.1     | Notation                                            |     |

|         | 2.2     | Instruction Reference.                              |     |

|         | 2.2     | COMPD.                                              |     |

|         |         | COMPS                                               |     |

|         |         | COMSD                                               |     |

|         |         | COMSS                                               |     |

|         |         | CVTPH2PS                                            |     |

|         |         | CVTPS2PH                                            |     |

|         |         | FMADDPD                                             |     |

|         |         | FMADDPS                                             |     |

|         |         | FMADDSD                                             | 42  |

|         |         | FMADDSS                                             | 45  |

|         |         | FMSUBPD.                                            |     |

|         |         | FMSUBPS                                             | 51  |

|         |         | FMSUBSD                                             |     |

|         |         | FMSUBSS                                             | 57  |

|         |         | FNMADDPD                                            | 60  |

|         |         | FNMADDPS                                            | 63  |

|         |         | FNMADDSD.                                           |     |

|         |         | FNMADDSS                                            | 69  |

|         |         | FNMSUBPD                                            | 72  |

|         |         | FNMSUBPS                                            |     |

|         |         | FNMSUBSD                                            | 78  |

|         |         | FNMSUBSS                                            | 81  |

| FRCZPD    | 84    |

|-----------|-------|

| FRCZPS    | 86    |

| FRCZSD    | 88    |

| FRCZSS    |       |

| PCMOV     |       |

| РСОМВ     | 95    |

| PCOMD     | 98    |

| PCOMQ     |       |

| РСОМИВ    |       |

| PCOMUD    |       |

| PCOMUQ    |       |

| PCOMUW    |       |

| PCOMW     |       |

| PERMPD    |       |

| PERMPS    |       |

| PHADDBD   |       |

| PHADDBQ   |       |

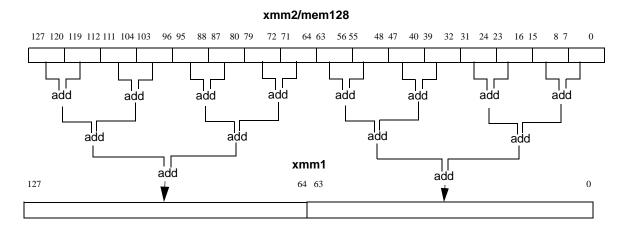

| PHADDBW   |       |

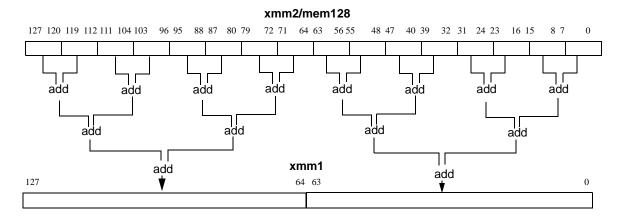

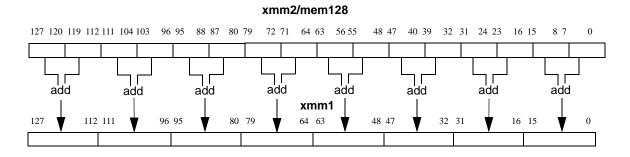

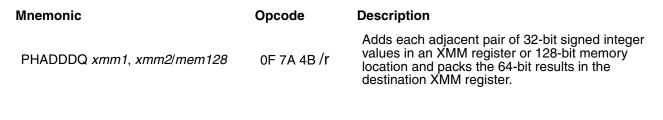

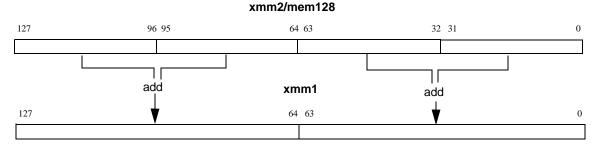

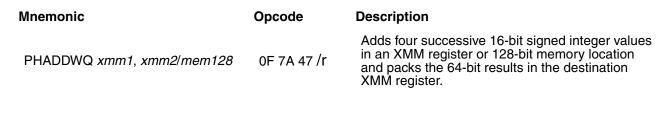

| PHADDDQ   |       |

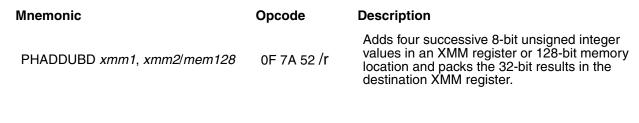

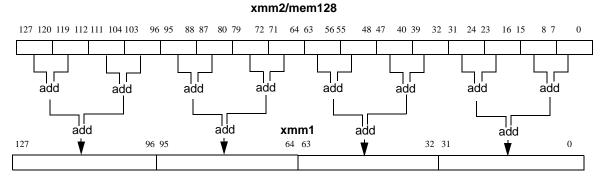

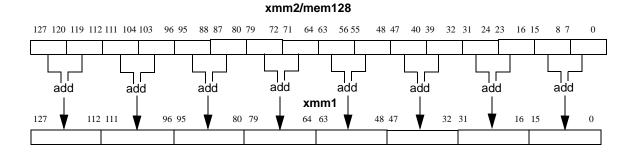

| PHADDUBD  |       |

| PHADDUBQ  |       |

| PHADDUBW  |       |

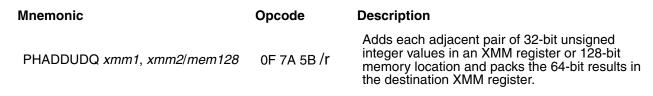

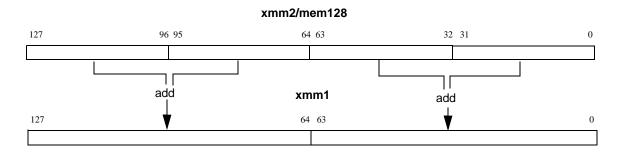

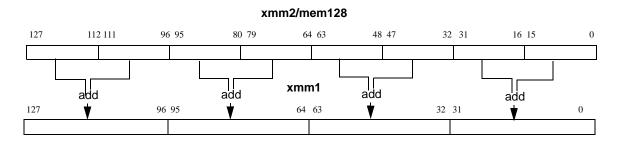

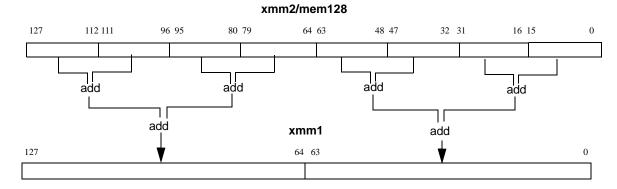

| PHADDUDQ  |       |

| PHADDUWD  |       |

| PHADDUWQ  | . 145 |

| PHADDWD   | . 147 |

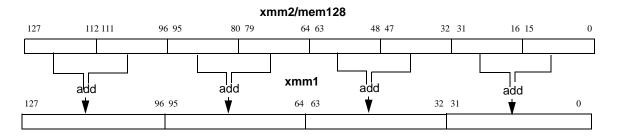

| PHADDWQ   | . 149 |

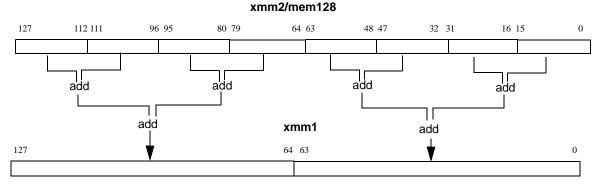

| PHSUBBW   | . 151 |

| PHSUBDQ   |       |

| PHSUBWD   | . 155 |

| PMACSDD   |       |

| PMACSDQH  |       |

| PMACSDQL  |       |

| PMACSSDD  |       |

| PMACSSDQH | . 169 |

| PMACSSDQL |       |

| PMACSSWD  |       |

| PMACSSWW  |       |

| PMACSWD   |       |

| PMACSWW   |       |

| PMADCSSWD |       |

| PMADCSWD  |       |

| PPERM     |       |

| PROTB     |       |

| PROTD     |       |

| PROTQ     |       |

| PROTW     | . 206 |

| PSHAB   |  |

|---------|--|

| PSHAD   |  |

| PSHAQ   |  |

| PSHAW   |  |

| PSHLB   |  |

| PSHLD.  |  |

| PSHLQ.  |  |

| PSHLW   |  |

| PTEST   |  |

| ROUNDPD |  |

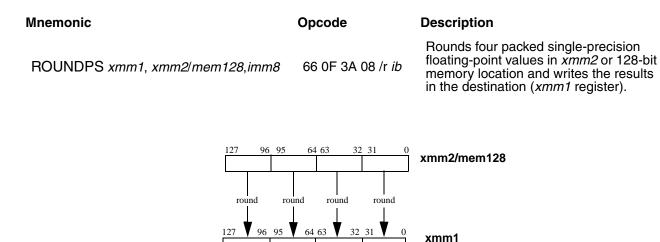

| ROUNDPS |  |

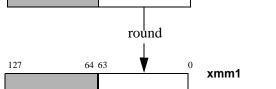

| ROUNDSD |  |

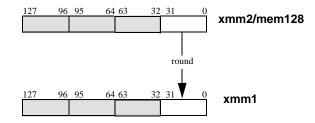

| ROUNDSS |  |

|         |  |

# Figures

| Figure 1-1. | Instruction Byte-Order                                             | . 2 |

|-------------|--------------------------------------------------------------------|-----|

| Figure 1-2. | Opcode3 Byte Format                                                | . 2 |

| Figure 1-3. | DREX Byte Format                                                   | . 3 |

| Figure 1-4. | 16-Bit Floating-Point Data Type                                    | . 8 |

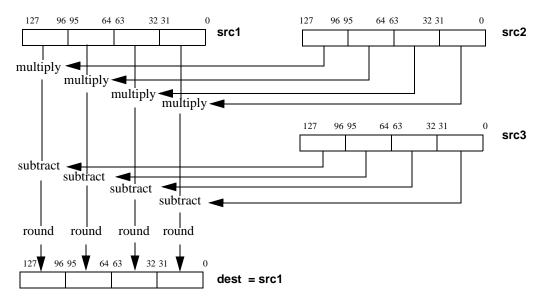

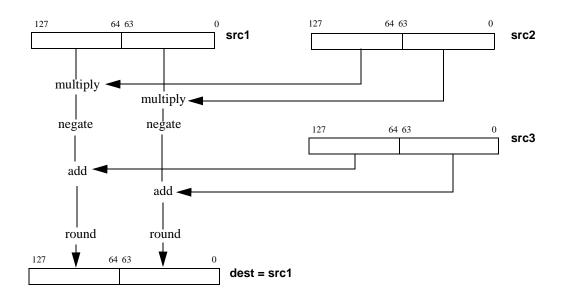

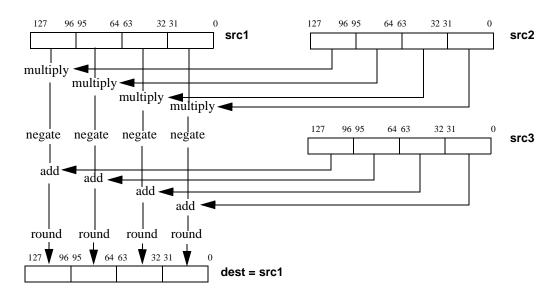

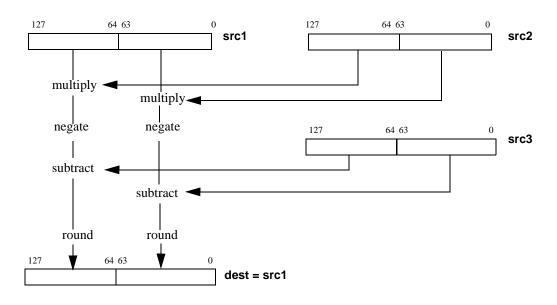

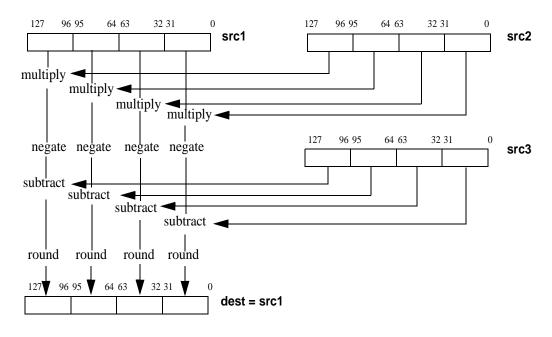

| Figure 1-5. | Operation of Multiplication with Addition/Subtraction Instructions | . 9 |

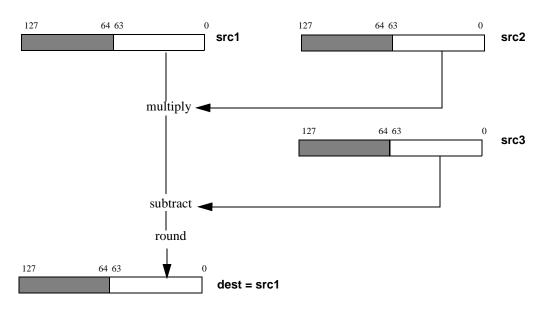

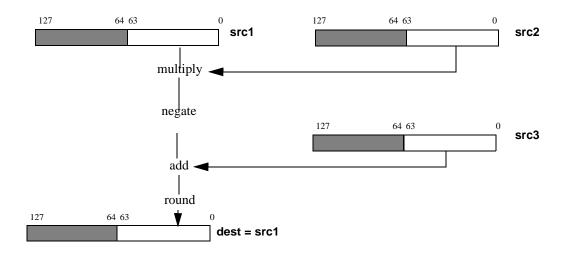

| Figure 1-6. | Operation of Multiply and Accumulate Instructions                  | 11  |

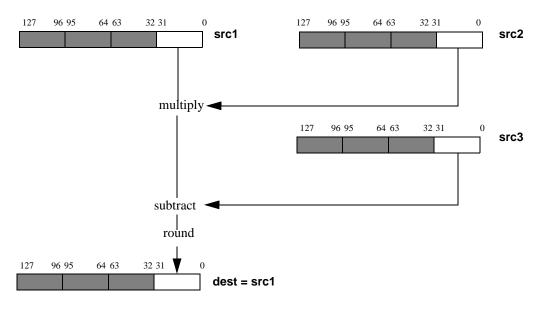

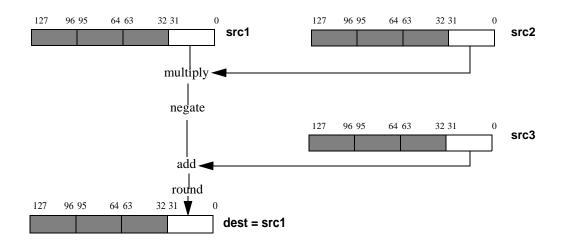

| Figure 1-7. | Operation of Multiply, Add and Accumulate Instructions             | 12  |

# **Tables**

| Table 1-1.  | Opcode3 Byte Fields                                        | 2 |

|-------------|------------------------------------------------------------|---|

| Table 1-2.  | Operation Size – OPS                                       | 2 |

| Table 1-3.  | DREX Byte Fields                                           |   |

| Table 1-4.  | Operand Configurations for Four-Operand Instructions       | 4 |

| Table 1-5.  | Four Operand Instruction Opcode Map                        | 4 |

| Table 1-6.  | NaN Results for SRC1 * SRC2 + SRC3                         | 5 |

| Table 1-7.  | Operand Configurations for Three Operand Instructions      | 6 |

| Table 1-8.  | Three Operand Instruction Opcode Map                       | 6 |

| Table 1-9.  | One/Two Operand Instruction Opcode Map                     | 7 |

| Table 1-10. | Supported 16-Bit Floating-Point Encodings                  | 8 |

| Table 2-1.  | PERMPD Control Byte                                        |   |

| Table 2-2.  | PERMPS Control Byte                                        |   |

| Table 2-3.  | PPERM Control Byte                                         |   |

| Table 2-4.  | Rounding Modes and Encoding of Rounding Control (RC) Field |   |

| Table 2-5.  | Rounding Modes and Encoding of Rounding Control (RC) Field |   |

| Table 2-6.  | Rounding Modes and Encoding of Rounding Control (RC) Field |   |

| Table 2-7.  | Rounding Modes and Encoding of Rounding Control (RC) Field |   |

# **Revision History**

| Date        | Revision | Description             |

|-------------|----------|-------------------------|

| August 2007 | 3.00     | Initial public release. |

# Preface

# **About This Book**

This book consists of documentation changes and additions to the multivolume AMD64 Architecture *Programmer's Manual*. The following table lists each volume and its order number.

| Title                                                      | Order No. |

|------------------------------------------------------------|-----------|

| Volume 1, Application Programming                          | 24592     |

| Volume 2, System Programming                               | 24593     |

| Volume 3, General-Purpose and System Instructions          | 24594     |

| Volume 4, 128-Bit Media Instructions                       | 26568     |

| Volume 5, 64-Bit Media and x87 Floating-Point Instructions | 26569     |

# Audience

This document is intended for all programmers writing application or system software for a processor that implements the AMD64 architecture.

# 1 New 128-Bit Instructions

This release of the AMD64 architecture introduces many new 128-bit instructions. The AMD64 128bit media instructions are discussed in detail in the AMD64 Architecture Programmer's Manual Volume 4: 128-Bit Media Instructions, order# 26568. This document describes new instructions, including new three-operand instructions. Included are 23 base instructions, expanding to more than 100 total instructions, are designed to:

- Improve performance by increasing the work per instruction and

- Remove loads by reducing saving or reloading of register operands

New instructions include:

- Fused multiply accumulate (FMACxx) instructions

- Integer multiply accumulate (IMAC, IMADC) instructions

- Permutation and conditional move instructions

- Vector compare and test instructions

- Precision control, rounding, and conversion instructions

Support for these instructions is provided by a new instruction encoding, which adds a third opcode byte (Opcode3). For the three- and four-operand instructions, a new *DREX* byte defines the destination register and provides the register extension information normally contained in a REX prefix. The REX prefix is not allowed with those instructions.

Support for the new instructions is indicated by ECX bit 11 (SSE5) as returned by CPUID function 8000\_0001h. Attempting to execute these instructions causes a #UD exception if they are not present in the hardware.

### 1.1 New 128-Bit Media Instruction Format

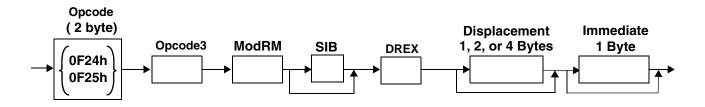

This release introduces a new 128-bit media instruction format, which adds a third opcode byte, *Opcode3*. These instructions use opcodes 0F 24 00–FFh and 0F 25 00–FFh. Another new byte, the *DREX* byte, specifies the destination register and the REX extensions on the source operands. Instruction group 0F 25h is assigned to instructions that require a one-byte immediate operand, 0F 24h is assigned to instructions that do not. Prefixes 66h, F2h, and F3h can be used with opcode groups 0F 24h and 0F 25h to create new instruction maps. An invalid opcode exception results if a REX prefix is used with these opcodes.

Figure 1-1 on page 2 shows the byte order of the instruction format. The Opcode3 byte appears immediately after the two-byte Opcode, and the DREX byte appears immediately after the SIB byte (or ModRM byte, if there is no SIB byte).

#### 43479—Rev. 3.00—August 2007

#### Figure 1-1. Instruction Byte-Order

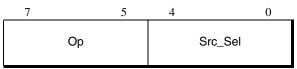

#### 1.1.1 Opcode3 Byte

The format of the Opcode3 byte is shown in Figure 1-2. A description of the fields is provided in Table 1-1.

| 7      | 3 | 2   | 1 | 0  |

|--------|---|-----|---|----|

| Opcode |   | OC1 | 0 | PS |

#### Table 1-1. Opcode3 Byte Fields

| Field  | Bit<br>Position | Definition                                                                                                                                                                                                                                                                                                                                                                                              |

|--------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Opcode | 7-3             | Provides additional opcode bits for the instructions                                                                                                                                                                                                                                                                                                                                                    |

| OC1    | 2               | Operand Configuration Bit 1—Together with OC0, defines the order of the operands in the three and four operand instruction formats. For the four operand instruction format, see Table 1-4, "Operand Configurations for Four-Operand Instructions", on page 4 for details. For the three operand instruction format, see Table 1-7, "Operand Configurations for Three Operand Instructions", on page 6. |

| OPS    | 1-0             | Operation Size - provides the size of the operation for both integer and floating-point. See Table 1-2 for details.                                                                                                                                                                                                                                                                                     |

| Table 1-2. | Operation | Size – OPS |

|------------|-----------|------------|

|------------|-----------|------------|

| Opcode3.OPS | Integer Operation | Floating-Point<br>Operation |

|-------------|-------------------|-----------------------------|

| 00          | Byte              | PS                          |

| 01          | Word              | PD                          |

| 10          | Doubleword        | SS                          |

| 11          | Quadword          | SD                          |

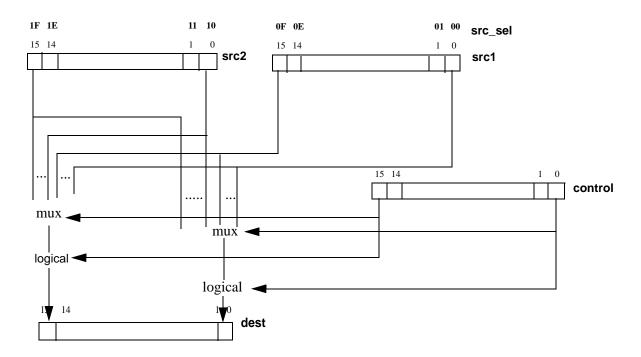

#### 1.1.2 DREX Byte

The format of the DREX byte is shown in Figure 1-3. A description of the fields is provided in Table 1-3 below.

| 7    | 4 | 3   | 2 | 1 | 0 |

|------|---|-----|---|---|---|

| dest |   | OC0 | R | Х | В |

#### Table 1-3. DREX Byte Fields

|           | Bit      |                                                                                                                                                                                                                          |

|-----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonic  | Position | Definition                                                                                                                                                                                                               |

| DREX.dest | 7-4      | XMM destination register                                                                                                                                                                                                 |

| DREX.OC0  | 3        | Operand Configuration Bit 0 - Together with OC1, defines the order of the operands in the four operand instruction format. See Table 1-4, "Operand Configurations for Four-Operand Instructions", on page 4 for details. |

| DREX.R    | 2        | 1-bit (high) extension of the ModRM <i>reg</i> field, thus permitting access to 16 XMM registers.                                                                                                                        |

| DREX.X    | 1        | 1-bit (high) extension of the SIB <i>index</i> field, thus permitting access to 16 registers.                                                                                                                            |

| DREX.B    | 0        | 1-bit (high) extension of the ModRM <i>r/m</i> field, SIB <i>base</i> field, or opcode <i>reg</i> field, thus permitting access to 16 registers.                                                                         |

Bits 7 and 2:0 are ignored in modes other than 64-bit.

# 1.2 Four-Operand 128-Bit Media Instructions

Some 128-bit media instructions have been derived from four-operand operations that require three input operands and one destination register. This is accomplished by mapping one of the three source operands to the destination operand by means of the DREX.dest field.

FMADDPS is an example of a four operand instruction:

FMADDPS dest, src1, src2, src3; dest = src1 \* src2 + src3

The first operand is the destination operand and is an XMM register addressed by the 4-bit DREX.dest field. The second, third and fourth operands are source operands. One source operand is an XMM register addressed by the ModRM.reg field, another source operand is an XMM register or a memory operand addressed by the ModRM.r/m field, and another source operand is the same register as the destination register.

The OC1 and OC0 bits combine to determine which source operand is specified by which operand field in the opcode, as shown in Table 1-4 on page 4.

Instructions beginning with opcode bytes 0F 24h or 0F 25h take a DREX byte and do not use a REX prefix. The DREX.B, DREX.R and DREX.X bits are used to allow access to the REX registers.

| OC[1:0] | dest      | src1      | src2      | src3      |

|---------|-----------|-----------|-----------|-----------|

| 00b     | DREX.dest | DREX.dest | modrm.reg | modrm.r/m |

| 01b     | DREX.dest | DREX.dest | modrm.r/m | modrm.reg |

| 10b     | DREX.dest | modrm.reg | modrm.r/m | DREX.dest |

| 11b     | DREX.dest | modrm.r/m | modrm.reg | DREX.dest |

Table 1-4.

Operand Configurations for Four-Operand Instructions

The four operand instructions have opcodes in the 0F 24h and 0F 25h opcode pages. See Table 1-5.

|                     |              |                  | - 1-                  |                         |                    |

|---------------------|--------------|------------------|-----------------------|-------------------------|--------------------|

| Operation           | Opcode       | Opcode3<br>[7:3] | Opcode3<br>[2]<br>OC1 | Opcode3<br>[1:0]<br>OPS | DREX<br>[3]<br>OC0 |

| COM <sup>a</sup>    | 0F 25 2C-2Fh | 00101b           | 1b                    | OPS                     | 0b                 |

| FMADD <sup>a</sup>  | 0F 24 00-07h | 00000b           | OC1                   | OPS                     | OC0                |

| FMSUB <sup>a</sup>  | 0F 24 08-0Fh | 00001b           | OC1                   | OPS                     | OC0                |

| FNMADD <sup>a</sup> | 0F 24 10-17h | 00010b           | OC1                   | OPS                     | OC0                |

| FNMSUB <sup>a</sup> | 0F 24 18-1Fh | 00011b           | OC1                   | OPS                     | OC0                |

| PCOM <sup>a</sup>   | 0F 25 4C-4Fh | 01001b           | 1b                    | OPS                     | 0b                 |

| PCOMU <sup>a</sup>  | 0F 25 6C-6Fh | 01101b           | 1b                    | OPS                     | 0b                 |

| PERMPS              | 0F 24 20,24h | 00100b           | OC1                   | 00b                     | OC0                |

| PERMPD              | 0F 24 21,25h | 00100b           | OC1                   | 01b                     | OC0                |

| PCMOV               | 0F 24 22,26h | 00100b           | OC1                   | 10b                     | OC0                |

| PPERM               | 0F 24 23,27h | 00100b           | OC1                   | 11b                     | OC0                |

| PMACSSWW            | 0F 24 85h    | 10000b           | 1b                    | 01b                     | 0b                 |

| PMACSWW             | 0F 24 95h    | 10010b           | 1b                    | 01b                     | 0b                 |

| PMACSSWD            | 0F 24 86h    | 10000b           | 1b                    | 10b                     | 0b                 |

| PMACSWD             | 0F 24 96h    | 10010b           | 1b                    | 10b                     | 0b                 |

| PMACSSDD            | 0F 24 8Eh    | 10001b           | 1b                    | 10b                     | 0b                 |

| PMACSDD             | 0F 24 9Eh    | 10011b           | 1b                    | 10b                     | 0b                 |

| PMACSSDQL           | 0F 24 87h    | 10000b           | 1b                    | 11b                     | 0b                 |

| PMACSDQL            | 0F 24 97h    | 10010b           | 1b                    | 11b                     | 0b                 |

| PMACSSDQH           | 0F 24 8Fh    | 10001b           | 1b                    | 11b                     | 0b                 |

| PMACSDQH            | 0F 24 9Fh    | 10011b           | 1b                    | 11b                     | 0b                 |

Table 1-5.

Four Operand Instruction Opcode Map

| Operation | Opcode    | Opcode3<br>[7:3] | Opcode3<br>[2]<br>OC1 | Opcode3<br>[1:0]<br>OPS | DREX<br>[3]<br>OC0 |

|-----------|-----------|------------------|-----------------------|-------------------------|--------------------|

| PMADCSSWD | 0F 24 A6h | 10100b           | 1b                    | 10b                     | 0b                 |

| PMADCSWD  | 0F 24 B6h | 10110b           | 1b                    | 10b                     | 0b                 |

| Table 1-5. | Four Operand Instruction | <b>Opcode Map (continued)</b> |

|------------|--------------------------|-------------------------------|

|------------|--------------------------|-------------------------------|

a. Indicates four instruction variants (\_PS, \_PD, \_SS and \_SD) specified by the OPS field.

#### 1.2.1 NaN Results on FMAC Instructions

When a three source operand floating-point operation such as FMADDPS produces a QNaN result, its value is determined by the rules in Table 1-6.

SRC1 SRC2 SRC3 Result QNaN1. IE SNaN1 any any QNaN1 SNaN2 QNaN1, IE any QNaN1 SNaN3 QNaN1, IE any !NaN SNaN2 QNaN2, IE any !NaN QNaN2 SNaN3 QNaN2, IE !NaN !NaN SNaN3 QNaN3, IE !SNaN2 !SNaN3 QNaN1 QNaN1 !NaN QNaN2 !SNaN3 QNaN2 !NaN !NaN QNaN3 QNaN3 infinity QNaN(indefinite), IE zero !NaN infinity !NaN QNaN(indefinite), IE zero product=+infinity<sup>a</sup> QNaN(indefinite), IE -infinity product=-infinity<sup>a</sup> QNaN(indefinite), IE +infinity

Table 1-6. NaN Results for SRC1 \* SRC2 + SRC3

a. The +infinity or -infinity product requires one source operand to be infinity and the other source operand to be a valid non-zero value.

QNaN—quiet NaN

SNaN-signaling NaN

!SNaN—a number that does not represent a signaling NaN.

!NaN-either normal, denormal (including zero) or infinity

IE—Invalid-operation exception

### 1.3 Three-Operand 128-Bit Media Instructions

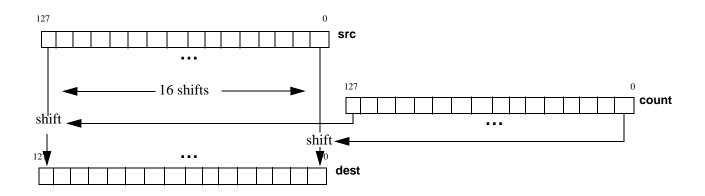

Some instructions have two source operands and a destination operand.

PROTB is an example of a three operand instruction:

PROTB dest, src, count dest = src <</>> count

The first operand is the destination operand, and is an XMM register addressed by the 4-bit DREX.dest field. The second and third operands are source operands. One source operand is an XMM register addressed by the ModRM.reg field, the other source operand is an XMM register or memory operand addressed by the ModRM.r/m field.

In the three-operand format the OC1 bit is used as an extension to the opcode. The OC0 bit determines which source operand is specified by which operand field, as shown in Table 1-7.

The instructions with a DREX byte do not use the REX prefix. The DREX.R, DREX.B and DREX.X bits are used to allow access to the REX registers.

Table 1-7.

Operand Configurations for Three Operand Instructions

| OC0 | dest      | src       | count     |

|-----|-----------|-----------|-----------|

| 0b  | drex.dest | modrm.reg | modrm.r/m |

| 1b  | drex.dest | modrm.r/m | modrm.reg |

The three operand instructions have opcodes in the 0F 24h page. See Table 1-8.

Table 1-8.

Three Operand Instruction Opcode Map

| Operation         | Opcode       | Opcode3[7:3] | Opcode3[2]<br>OC1 | Opcode3[1:0]<br>OPS | DREX[3]<br>OC0 |

|-------------------|--------------|--------------|-------------------|---------------------|----------------|

| PROT <sup>a</sup> | 0F 24 40-43h | 01000b       | 0b                | OPS                 | OC0            |

| PSHL <sup>a</sup> | 0F 24 44-47h | 01000b       | 1b                | OPS                 | OC0            |

| PSHA <sup>a</sup> | 0F 24 48-4Bh | 01001b       | 0b                | OPS                 | OC0            |

a. Indicates four instruction variants (\_B, \_W, \_D and \_Q) specified by the OPS field.

Note that there is only one operand configuration for the COM, PCOM and PCOMU instructions. The OC0 bit is zero.

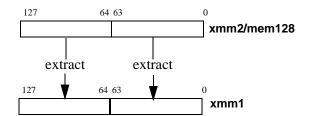

### 1.4 Other 128-Bit Media Instructions

Other instructions use the normal two byte operand assignment. The first instruction operand (xmm1) is the destination, addressed by the ModRM.reg field. The second operand (xmm2/mem128) is either an XMM register or memory operand, as determined by the ModRM and SIB.

CVTPH2PS is an example of a two operand instruction.

CVTPH2PS xmm1, xmm2/mem64

The new instructions with one or two operands are assigned to two-byte opcodes 0F 3Ah (ROUND), 0F 7Ah, 0F 7Bh (PROT*x*) and 0F 38h (PTEST). See Table 1-9 on page 7.

| Operation          | Opcode         | Opcode3[7:3] | Opcode3[2]<br>OC1 | Opcode3[1:0]<br>OPS |

|--------------------|----------------|--------------|-------------------|---------------------|

| FRCZ <sup>b</sup>  | 0F 7A 10-13h   | 00010b       | 0b                | OPS                 |

| CVTPH2PS           | 0F 7A 30h      | 00110b       | 0b                | 00b                 |

| CVTPS2PH           | 0F 7A 31h      | 00110b       | 0b                | 01b                 |

| PHADDBW            | 0F 7A 41h      | 01000b       | 0b                | 01b                 |

| PHADDBD            | 0F 7A 42h      | 01000b       | 0b                | 10b                 |

| PHADDBQ            | 0F 7A 43h      | 01000b       | 0b                | 11b                 |

| PHADDWD            | 0F 7A 46h      | 01000b       | 1b                | 10b                 |

| PHADDWQ            | 0F 7A 47h      | 01000b       | 1b                | 11b                 |

| PHADDDQ            | 0F 7A 4Bh      | 01001b       | 0b                | 11b                 |

| PHADDUBW           | 0F 7A 51h      | 01010b       | 0b                | 01b                 |

| PHADDUBD           | 0F 7A 52h      | 01010b       | 0b                | 10b                 |

| PHADDUBQ           | 0F 7A 53h      | 01010b       | 0b                | 11b                 |

| PHADDUWD           | 0F 7A 56h      | 01010b       | 1b                | 10b                 |

| PHADDUWQ           | 0F 7A 57h      | 01010b       | 1b                | 11b                 |

| PHADDUDQ           | 0F 7A 5Bh      | 01011b       | 0b                | 11b                 |

| PHSUBBW            | 0F 7A 61h      | 01100b       | 0b                | 01b                 |

| PHSUBWD            | 0F 7A 62h      | 01100b       | 0b                | 10b                 |

| PHSUBDQ            | 0F 7A 63h      | 01100b       | 0b                | 11b                 |

| PROT <sup>a</sup>  | 0F 7B 40-43h   | 01000b       | 0b                | OPS                 |

| PTEST              | 66 0F 38 17    | 00010b       | 1b                | 11b                 |

| ROUND <sup>b</sup> | 66 0F 3A 08-0B | 00001b       | 0b                | OPS                 |

Table 1-9. One/Two Operand Instruction Opcode Map

a. Indicates four instruction variants (\_B, \_W, \_D and \_Q) specified by the OPS field.

b. Indicates four instruction variants (\_PS, \_PD, \_SS and \_SD) specified by the OPS field.

# 1.5 16-Bit Floating-Point Data Type

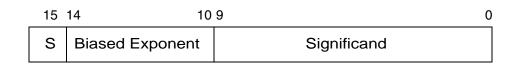

SSE5 introduces a new 16-bit floating-point data type and two instructions (CVTPS2PH and CVTPH2PS) to convert 16-bit floating-point values to and from single-precision format.

The 16-bit floating-point data type, shown in Figure 1-4 on page 8, includes a 1-bit sign, a 5-bit exponent with a bias of 15 and a 10-bit significand. The integer bit is implied, making a total of 11 bits in the significand. The value of the integer bit can be inferred from the number encoding. Table 1-10 on page 8 shows the floating-point encodings of supported numbers and non-numbers.

#### Figure 1-4. 16-Bit Floating-Point Data Type

Table 1-10.

Supported 16-Bit Floating-Point Encodings

| Sign | Bias<br>Exponent       | Significand <sup>a</sup>               | Classification                          |                   |

|------|------------------------|----------------------------------------|-----------------------------------------|-------------------|

| 0    | 1 1111                 | 1.01 1111 1111<br>to<br>1.00 0000 0001 | Positive Non-Number                     | SNaN              |

| 0    | 1 1111                 | 1.11 1111 1111<br>to<br>1.10 0000 0001 | T USILIVE NUT-NUTIDET                   | QNaN              |

| 0    | 1 1111                 | 1.00 0000 0000                         |                                         | Positive Infinity |

| 0    | 1 1110<br>to<br>0 0001 | 1.11 1111 1111<br>to<br>1.00 0000 0000 | Positive Floating-Point                 | Positive Normal   |

| 0    | 0 0000                 | 0.11 1111 1111<br>to<br>0.00 0000 0001 | Numbers                                 | Positive Denormal |

| 0    | 0 0000                 | 0.00 0000 0000                         |                                         | Positive Zero     |

| 1    | 0 0000                 | 0.00 0000 0000                         |                                         | Negative Zero     |

| 1    | 0 0000                 | 0.00 0000 0001<br>to<br>0.11 1111 1111 | Positive Floating-Point                 | Negative Denormal |

| 1    | 0 0001<br>to<br>1 1110 | 1.00 0000 0000<br>to<br>1.11 1111 1111 | Numbers                                 | Negative Normal   |

| 1    | 1 1111                 | 1.00 0000 0000                         |                                         | Negative Infinity |

| 1    | 1 1111                 | 1.00 0000 0001<br>to<br>1.01 1111 1111 | Nogotivo Non Number                     | SNaN              |

| 1    | 1 1111                 | 1.10 0000 0001<br>to<br>1.11 1111 1111 | <ul> <li>Negative Non-Number</li> </ul> | QNaN              |

a. The "1." and "0." prefixes represent the implicit integer bit.

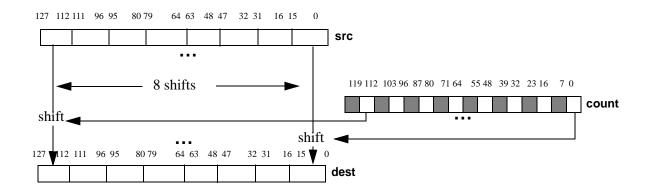

# 1.6 Floating Point Multiply and Add/Subtract

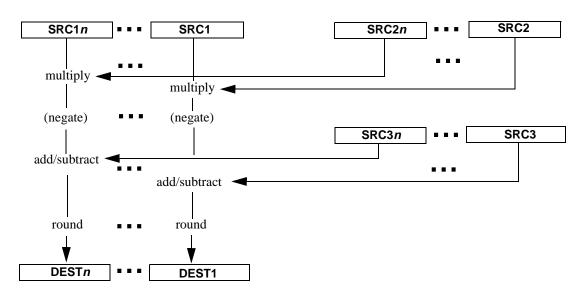

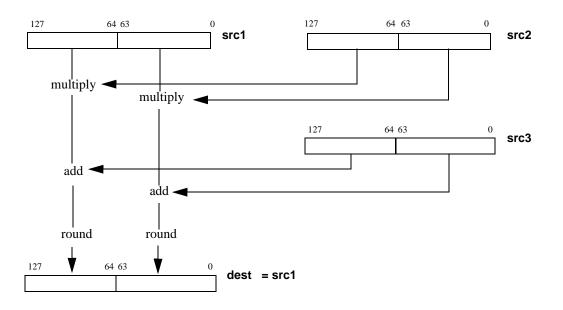

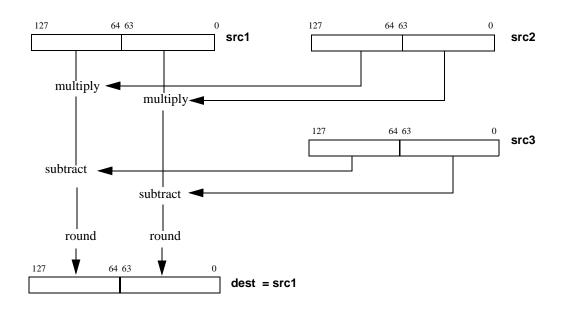

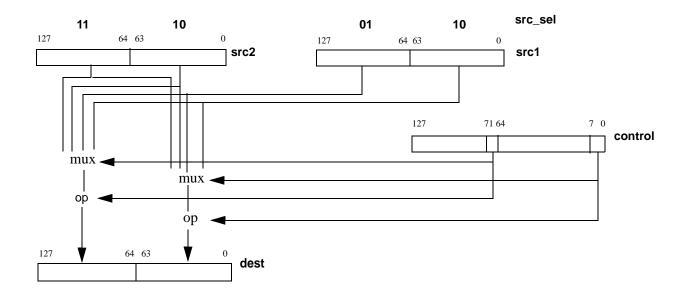

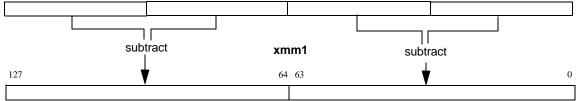

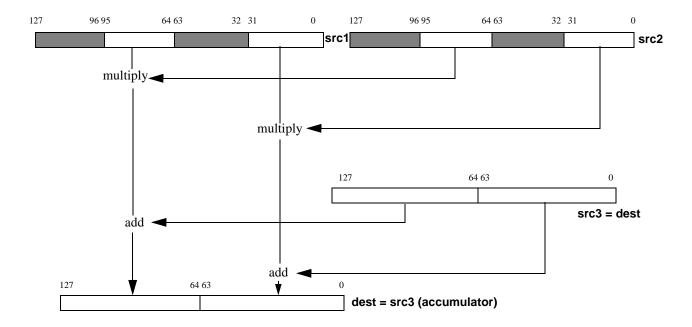

The combined operation of the floating-point (negative) multiplication and addition/subtraction operations is shown in Figure 1-5. The negative multiply instructions apply the negation to the results of the multiplication before applying the addition or subtraction operation.

#### (Negative) Multiply with Add/Subtract Instructions

#### Figure 1-5. Operation of Multiplication with Addition/Subtraction Instructions

The SSE5 instructions set includes the following combined multiply with add/subtract instructions. Note that scalar instructions only operate on the lowest element of the specified size in the source and destination registers; the contents of the upper elements of the source and destination registers are unaffected by the operation.

- FMADDPS—Multiply and Add Packed Single-Precision Floating Point

- FMADDPD—Multiply and Add Packed Double-Precision Floating Point

- FMADDSS—Multiply and Add Scalar Single-Precision Floating Point

- FMADDSD—Multiply and Accumulate Scalar Double-Precision Floating Point

- FMSUBPS—Multiply and Subtract Packed Single-Precision Floating-Point

- FMSUBPD—Multiply and Subtract Packed Double-Precision Floating-Point

- FMSUBSS—Multiply and Subtract Scalar Single-Precision Floating-Point

- FMSUBSD—Multiply and Subtract Scalar Double-Precision Floating-Point

- FNMADDPS—Negative Multiply and Add Packed Single-Precision Floating-Point

- FNMADDPD—Negative Multiply and Add Packed Double-Precision Floating-Point

- FNMADDSS—Negative Multiply and Add Scalar Single-Precision Floating-Point

- FNMADDSD—Negative Multiply and Add Scalar Double-Precision Floating-Point

- FNMSUBPS—Negative Multiply and Subtract Packed Single-Precision Floating-Point

- FNMSUBPD—Negative Multiply and Subtract Packed Double-Precision Floating-Point

- FNMSUBSS—Negative Multiply and Subtract Scalar Single-Precision Floating-Point

- FNMSUBSD—Negative Multiply and Subtract Scalar Double-Precision Floating-Point

# 1.7 Integer Multiply (Add) and Accumulate Instructions

The multiply and accumulate and multiply, add and accumulate instructions operate on and produce packed signed integer values. These instructions allow the accumulation of results from (possibly) many iterations of similar operations without a separate intermediate addition operation to update the accumulator register. The accumulator is both a source (*src3*) and a destination register (*dest*)—it is an XMM register addressed by the DREX.dest field.

#### 1.7.1 Saturation

Some instructions limit the result of an operation to the maximum or minimum value representable by the data type of the destination—an operation known as *saturation*. Many of the integer multiply and accumulate instructions saturate the cumulative results of the multiplication and addition (accumulation) operations before writing the final results to the destination (accumulator) register.

Note, however, that not all multiply and accumulate instructions saturate results. (For further discussion of saturation, see the AMD64 Architecture Programmer's Manual Volume 1: Application Programming, order# 24592.)

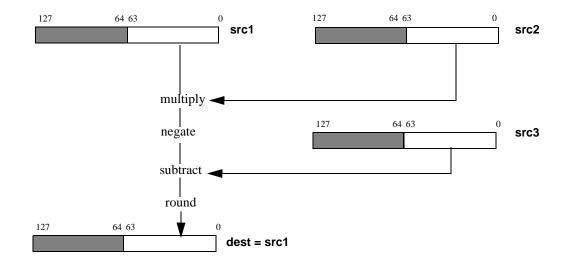

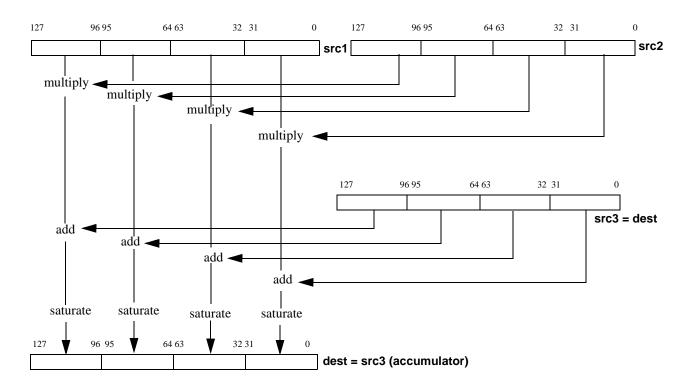

#### 1.7.2 Multiply and Accumulate Instructions

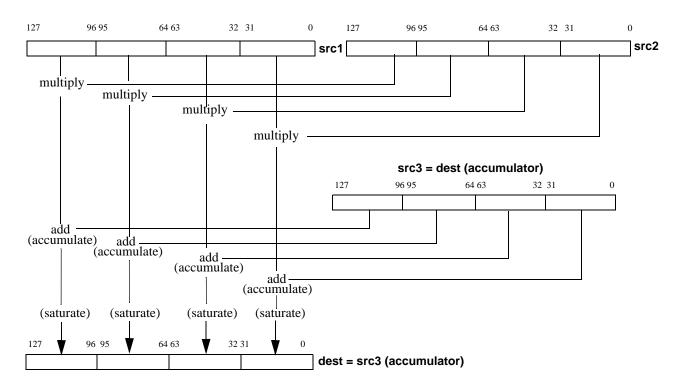

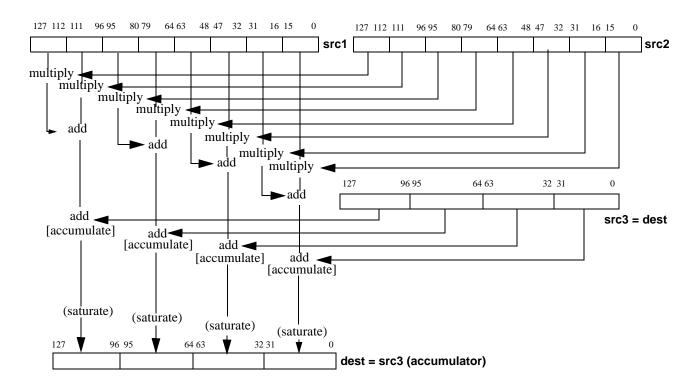

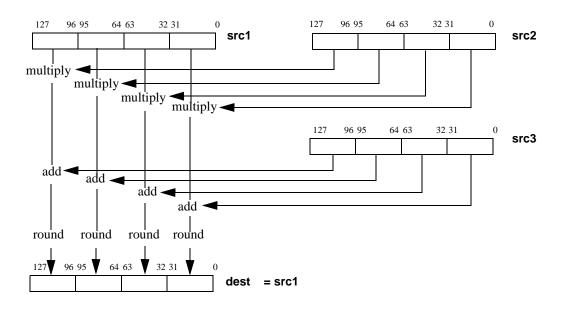

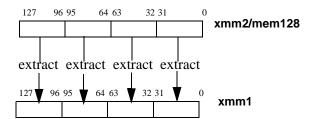

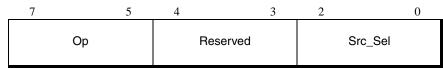

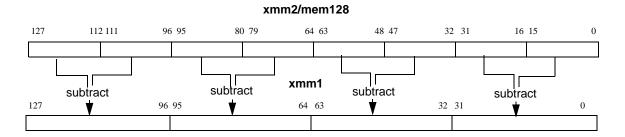

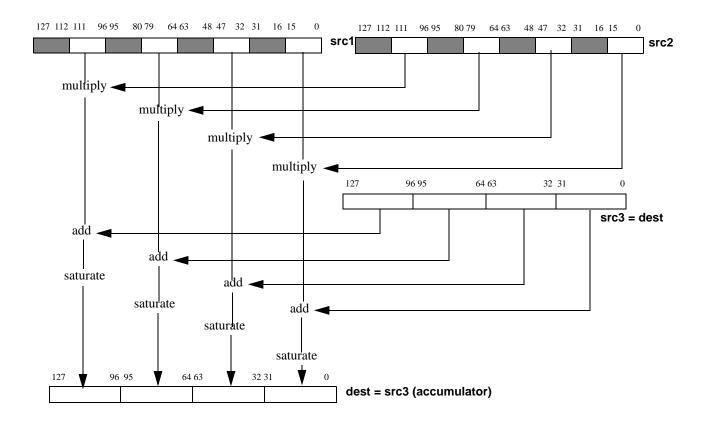

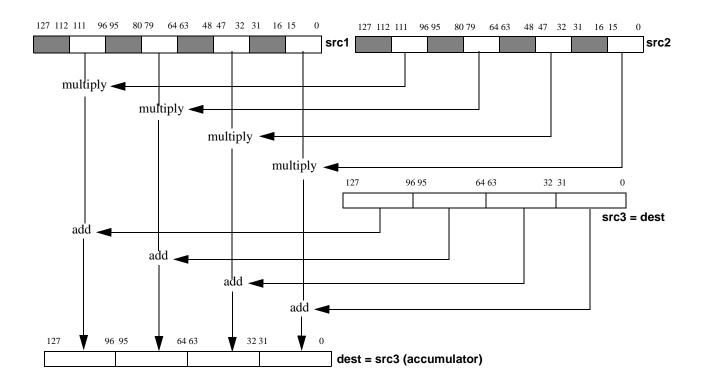

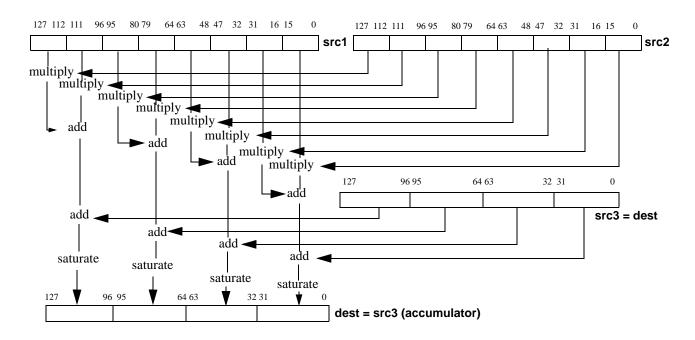

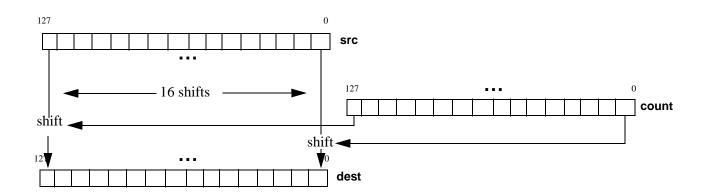

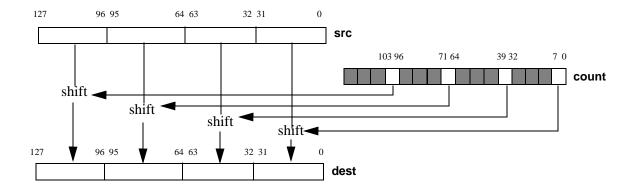

The operation of a typical SSE5 integer multiply and accumulate instruction is shown in Figure 1-6 on page 11.

The multiply and accumulate instructions operate on and produce packed signed integer values. These instructions first multiply the value in the first source operand by the corresponding value in the second source operand. Each signed integer product is then added to the corresponding value in the third source operand, which is the accumulator and is identical to the destination operand. The results may or may not be saturated prior to being written to the destination register, depending on the instruction.

#### 43479—Rev. 3.00—August 2007

#### Figure 1-6. Operation of Multiply and Accumulate Instructions

The SSE5 instruction set provides the following integer multiply and accumulate instructions.

- PMACSSWW—Packed Multiply Accumulate Signed Word to Signed Word with Saturation

- PMACSWW—Packed Multiply Accumulate Signed Word to Signed Word

- PMACSSWD—Packed Multiply Accumulate Signed Word to Signed Doubleword with Saturation

- PMACSWD—Packed Multiply Accumulate Signed Word to Signed Doubleword

- PMACSSDD—Packed Multiply Accumulate Signed Doubleword to Signed Doubleword with Saturation

- PMACSDD—Packed Multiply Accumulate Signed Doubleword to Signed Doubleword

- PMACSSDQL—Packed Multiply Accumulate Signed Low Doubleword to Signed Quadword with Saturation

- PMACSSDQH—Packed Multiply Accumulate Signed High Doubleword to Signed Quadword with Saturation

- PMACSDQL—Packed Multiply Accumulate Signed Low Doubleword to Signed Quadword

- PMACSDQH—Packed Multiply Accumulate Signed High Doubleword to Signed Quadword

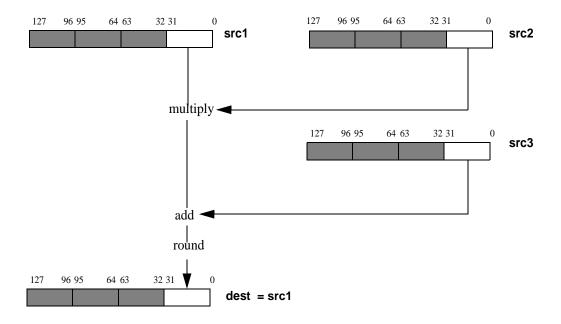

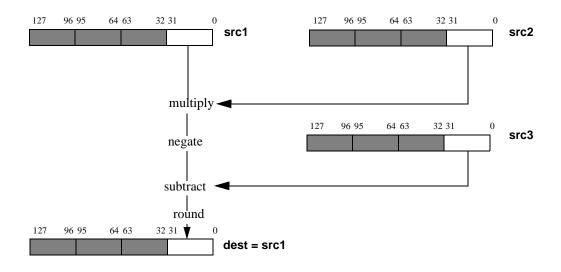

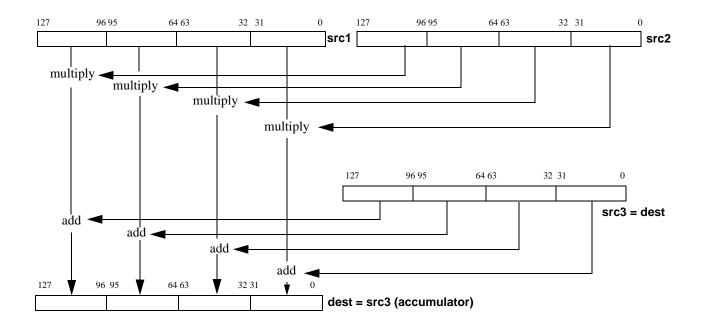

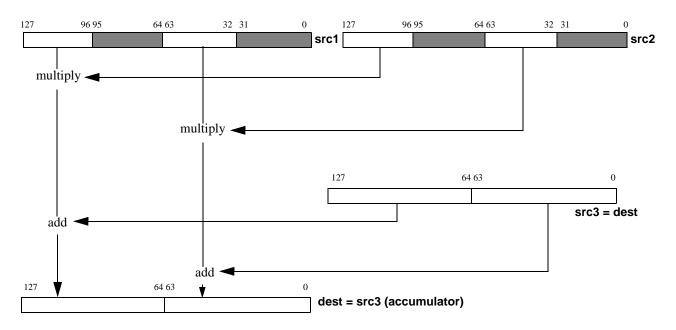

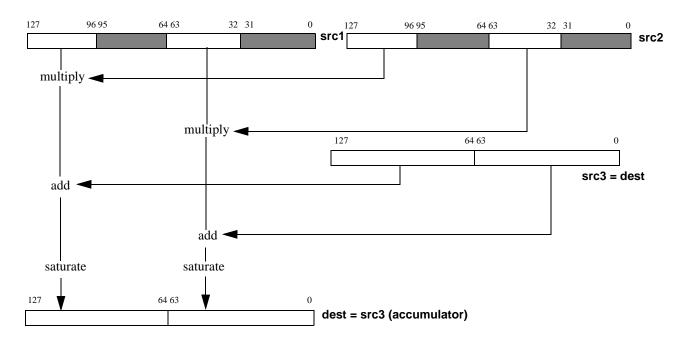

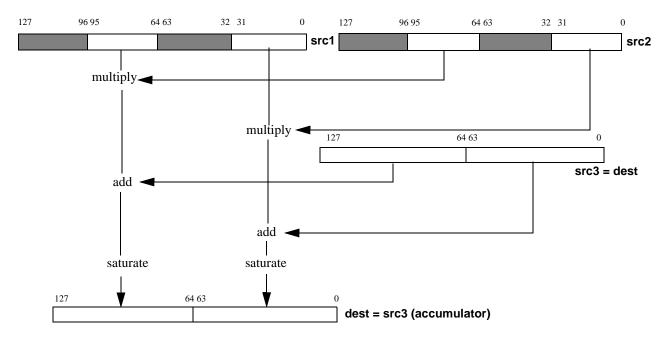

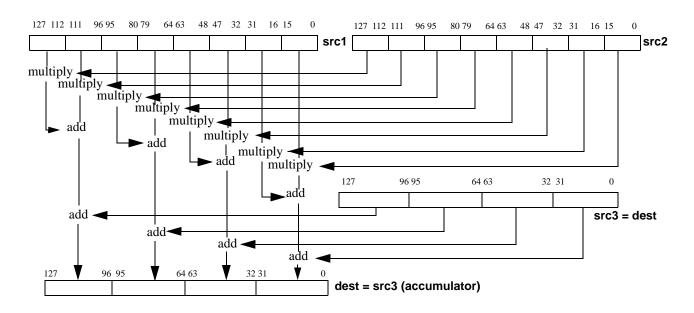

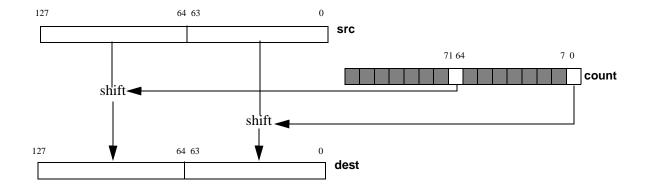

#### 1.7.3 SSE5 Integer Multiply, Add and Accumulate Instructions

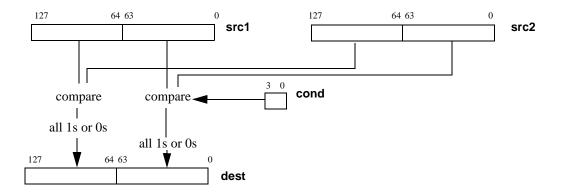

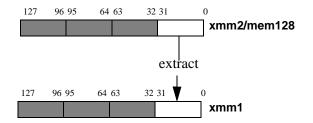

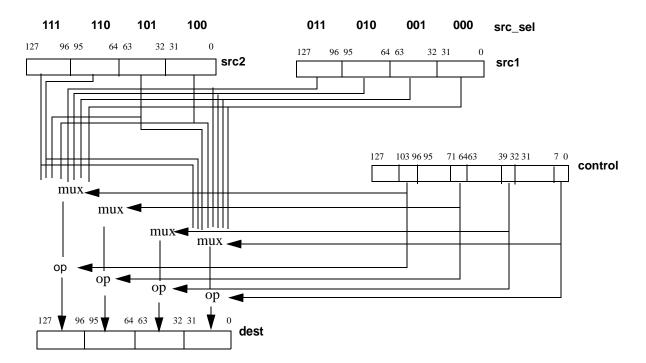

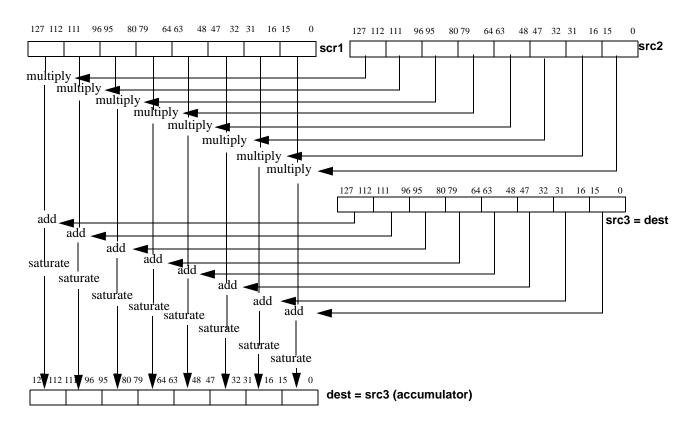

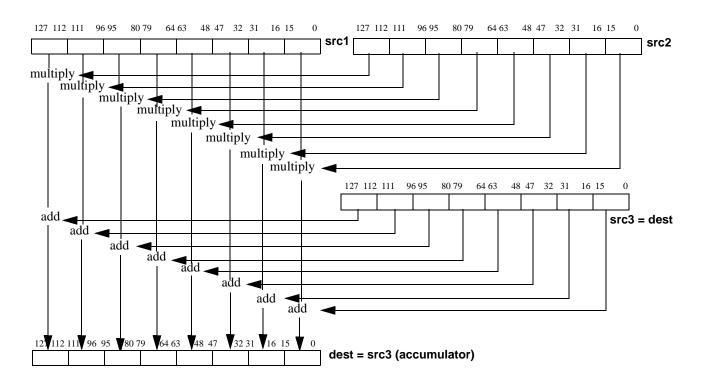

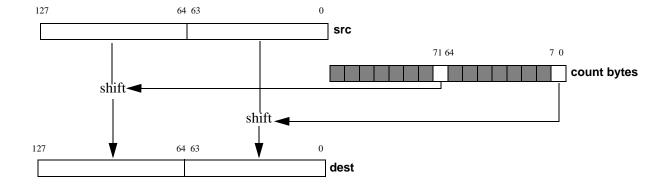

The operation of the multiply, add and accumulate instructions is illustrated in Figure 1-7.

The multiply, add and accumulate instructions first multiply each packed signed integer value in the first source operand by the corresponding packed signed integer value in the second source operand. The odd and even adjacent resulting products are then added. Each resulting sum is then added to the corresponding packed signed integer value in the third source operand, which is the accumulator and is identical to the destination XMM register addressed by the DREX.dest field.

Figure 1-7. Operation of Multiply, Add and Accumulate Instructions

The SSE5 instruction set provides the following integer multiply, add and accumulate instructions.

- PMADCSSWD—Packed Multiply Add and Accumulate Signed Word to Signed Doubleword with Saturation

- PMADCSWD—Packed Multiply Add and Accumulate Signed Word to Signed Doubleword

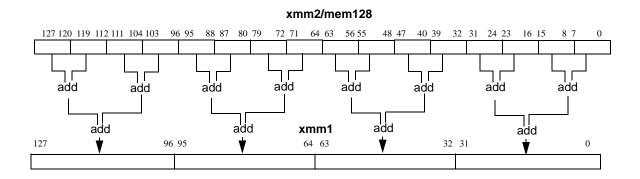

# 1.8 Packed Integer Horizontal Add and Subtract

The packed horizontal add and subtract signed byte instructions successively add adjacent pairs of signed integer values from the second source XMM register or 128-bit memory operand and pack the (sign-extended) integer result of each addition in the destination (first source).

43479—Rev. 3.00—August 2007

- PHADDBW—Packed Horizontal Add Signed Byte to Signed Word

- PHADDBD—Packed Horizontal Add Signed Byte to Signed Doubleword

- PHADDBQ—Packed Horizontal Add Signed Byte to Signed Quadword

- PHADDDQ—Packed Horizontal Add Signed Doubleword to Signed Quadword

- PHADDUBW—Packed Horizontal Add Unsigned Byte to Word

- PHADDUBD—Packed Horizontal Add Unsigned Byte to Doubleword

- PHADDUBQ—Packed Horizontal Add Unsigned Byte to Quadword

- PHADDUWD—Packed Horizontal Add Unsigned Word to Doubleword

- PHADDUWQ—Packed Horizontal Add Unsigned Word to Quadword

- PHADDUDQ—Packed Horizontal Add Unsigned Doubleword to Quadword

- PHADDWD—Packed Horizontal Add Signed Word to Signed Doubleword

- PHADDWQ—Packed Horizontal Add Signed Word to Signed Quadword

- PHSUBBW—Packed Horizontal Subtract Signed Byte to Signed Word

- PHSUBWD—Packed Horizontal Subtract Signed Word to Signed Doubleword

- PHSUBDQ—Packed Horizontal Subtract Signed Doubleword to Signed Quadword

# 1.9 Vector Conditional Moves

SSE5 instructions include four vector conditional moves instructions:

- PCMOV—Vector Conditional Moves

- PPERM—Packed Permute Bytes

- PERMPS—Permute and Modify Single-Precision Floating Point

- PERMPD—Permute Double-Precision Floating Point

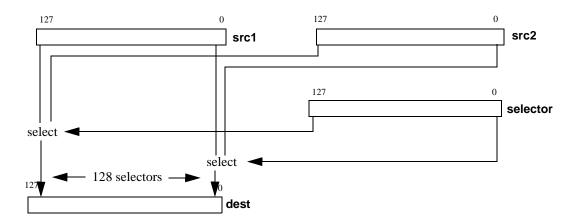

The PCMOV instruction implements the C/C++ language ternary '?' operator. This instruction operates on individual bits and requires a bitwise predicate in one XMM register and the two source operands in two more XMM registers.

The PPERM instruction performs vector permutation on a packed array of 32 bytes. The PPERM instruction replaces some or all of its destination bytes with 0x00, 0xFF, or one of the 32 bytes of the packed array. A byte selected from the array may have an additional operation such as NOT or bit reversal applied to it, before it is written to the destination. The action for each destination byte is determined by a corresponding control byte.

PERMP*x* instructions provides a superset of the SHUFPS instruction. This instruction performs a permutation operation on an array of eight single-precision or four double-precision floating-point values, optionally followed by an additional operation (ABS, NEG, NEGABS, set-to-constant (0.0, -1.0, 1.0, PI)).

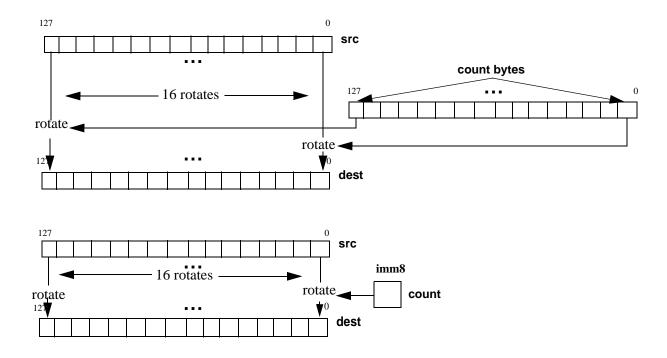

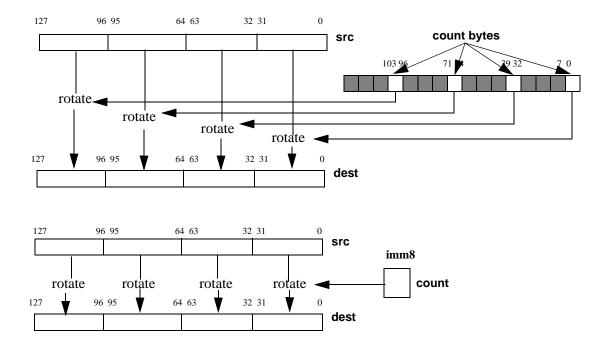

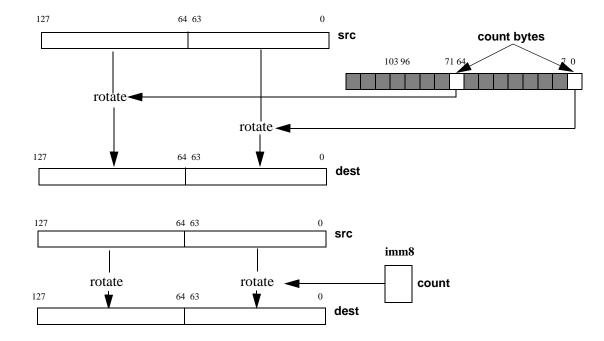

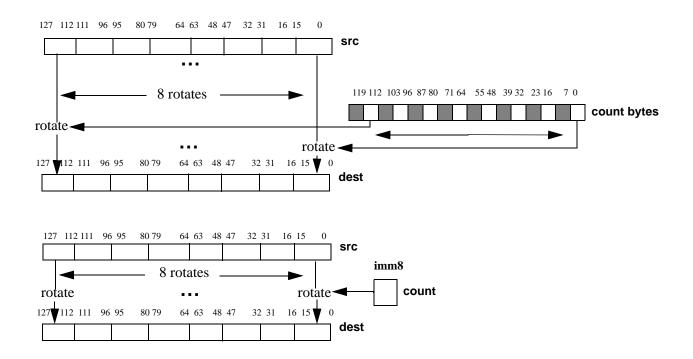

## 1.10 Packed Integer Rotates and Shifts

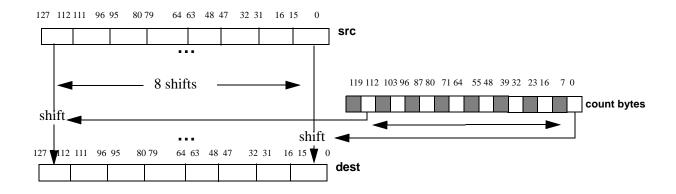

These instructions rotate/shift the elements of the vector in the first source XMM or 128-bit memory operand by the amount specified by a control byte. The rotates and shifts differ in the way they handle the control byte.

#### 1.10.1 Packed Integer Shifts

The packed integer shift instructions shift each element of the vector in the first source XMM or 128bit memory operand by the amount specified by a control byte contained in the least significant byte of the corresponding element of the second source operand. The result of each shift operation is returned in the destination XMM register. This allows load-and-rotate from memory operations. The SSE5 instruction set provides the following packed integer shift instructions:

- PSHLB—Packed Shift Logical Bytes

- PSHLW—Packed Shift Logical Words

- PSHLD—Packed Shift Logical Doublewords

- PSHLQ—Packed Shift Logical Quadwords

- PSHAB—Packed Shift Arithmetic Bytes

- PSHAW—Packed Shift Arithmetic Words

- PSHAD—Packed Shift Arithmetic Doublewords

- PSHAQ—Packed Shift Arithmetic Quadwords

#### 1.10.2 Packed Integer Rotate

There are two variants of the packed integer rotate instructions. The first is identical to that described above (see "Packed Integer Shifts"). In the second variant, the control byte is supplied by an immediate operand that determines the identical amount to rotate for every element in the first source operand. The SSE5 instruction set provides the following packed integer rotate instructions:

- PROTB—Packed Rotate Bytes

- PROTW—Packed Rotate Words

- PROTD—Packed Rotate Doublewords

- PROTQ—Packed Rotate Quadwords

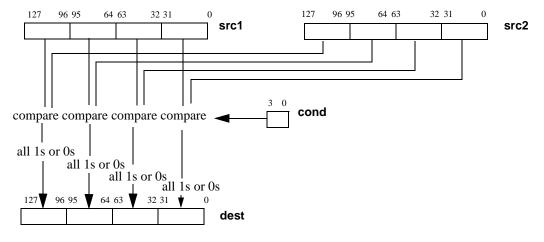

### **1.11** Floating Point Comparison and Predicate Generation

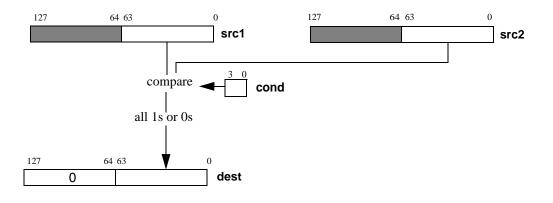

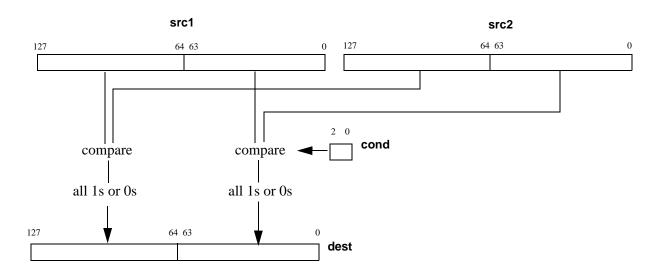

The SSE5 comparison instructions compare floating-point or integer values in the first source XMM register with corresponding floating point or integer values in the second source XMM register or 128bit memory. The type of comparison is specified by the immediate-byte operand. The resulting predicate is placed in the destination XMM register. If the condition is true, all bits in the corresponding field in the destination register are set to 1s; otherwise all bits in the field are set to 0s.

#### 1.11.1 Floating-Point Comparison Operations

The type of comparison of the floating-point comparison operation is specified by the *four* low-order bits of the immediate-byte operand. If the condition is true, all corresponding field in the destination will be set to all 1s; otherwise it will be set to all 0s.

Comparisons can be ordered or unordered. Ordered comparisons return TRUE only if both operands are valid numbers and the numbers have the relation specified by the type of comparison; they are FALSE otherwise.

Unordered comparisons return TRUE if one of the operands is a NaN or the numbers have the relation specified by the type of comparison; otherwise, they are FALSE.

- COMPS—Compare Vector Single-Precision Floating Point

- COMPD—Compare Vector Double-Precision Floating Point

- COMSS—Compare Scalar Single-Precision Floating Point

- COMSD—Compare Scalar Double-Precision Floating Point

#### 1.11.2 Integer Comparison and Predicate Generation

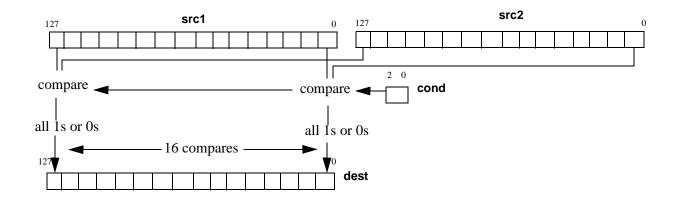

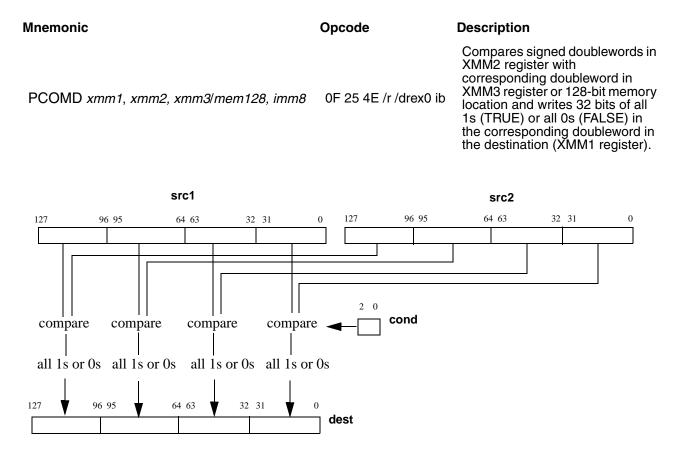

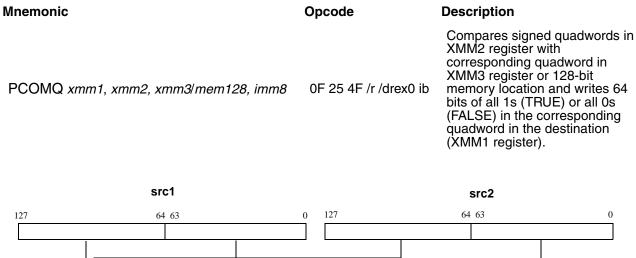

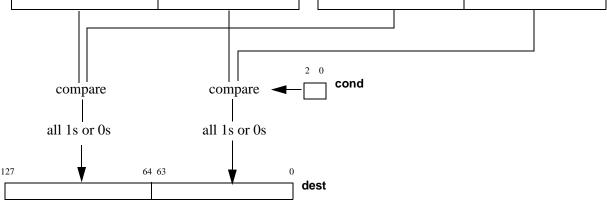

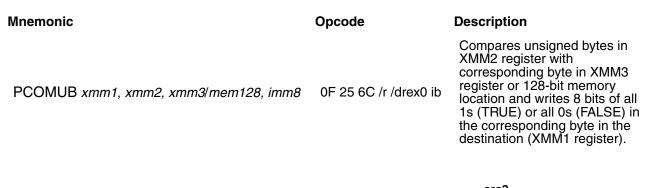

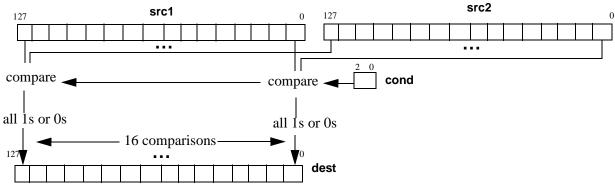

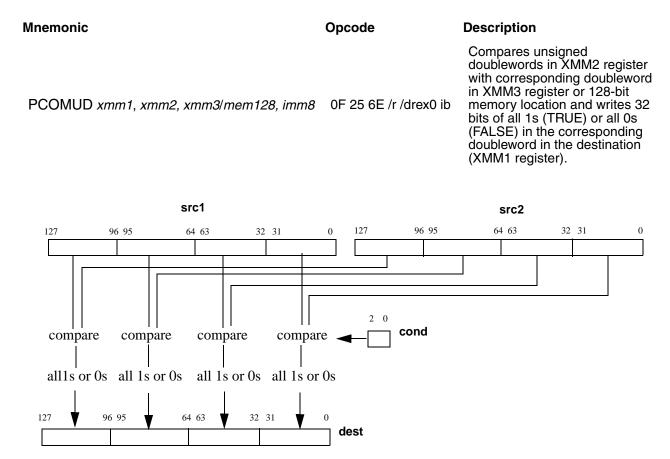

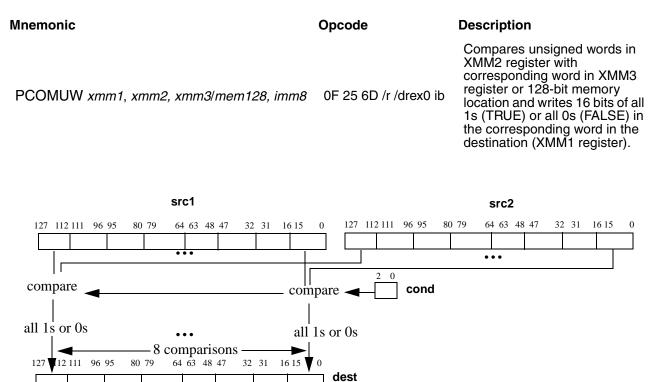

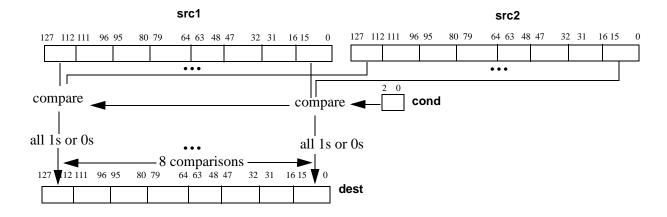

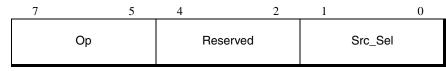

The integer comparison and predicate generation instructions compare corresponding packed unsigned bytes in the first and second source operands and write the result of each comparison in the corresponding byte of the destination. The result of each comparison is a value of all 1s (TRUE) or all 0s (FALSE). The type of comparison is specified by the three low-order bits of the immediate-byte operand. The SSE5 instruction set provides the following integer comparison instructions.

- PCOMUB—Compare Vector Unsigned Bytes

- PCOMUW—Compare Vector Unsigned Words

- PCOMUD—Compare Vector Unsigned Doublewords

- PCOMUQ—Compare Vector Unsigned Quadwords

- PCOMB—Compare Vector Signed Bytes

- PCOMW—Compare Vector Signed Words

- PCOMD—Compare Vector Signed Doublewords

- PCOMQ—Compare Vector Signed Quadwords

### 1.12 Test Instruction

The PTEST instruction performs a bitwise logical AND between the source XMM register or 128-bit memory location and destination XMM register. The ZF flag is set to 1 if all bit positions that are set to 1 in the mask operand are set to 0 in the source operand; otherwise, ZF is cleared. The CF flag is set to 1 if all bit positions specified in the mask operand are set to 1 in the source operand; otherwise, CF is cleared.

• PTEST—Predicate Test Register

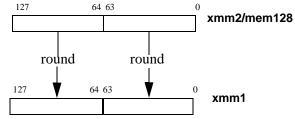

# 1.13 Precision Control and Rounding

The precision control and rounding instructions can move (from memory) and round data with a single instruction. The result of \_PD and \_PS instructions is a vector of floating-point numbers. The result of \_SD and \_SS instructions is always a scalar floating-point number. SSE5 provides the following precision control and rounding instructions:

- FRCZPD—Extract Fraction Packed Double-Precision Floating-Point

- FRCZPS—Extract Fraction Packed Single-Precision Floating-Point

- FRCZSD— Extract Fraction Scalar Double-Precision Floating-Point

- FRCZSS— Extract Fraction Scalar Single-Precision Floating Point

- ROUNDPD—Round Packed Double-Precision Floating-Point

- ROUNDPS—Round Packed Single-Precision Floating-Point

- ROUNDSD— Round Scalar Double-Precision Floating-Point

- ROUNDSS—Round Scalar Single-Precision Floating-Point Convert

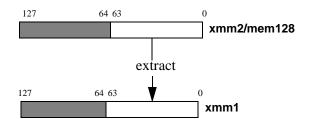

The FRCZPD and FRCZPS instructions extract the fractional portions of a vector of double-/singleprecision floating-point values in an XMM register or a 128-bit memory location and write the results in the corresponding field in the destination register.

The FRCZSS and FRCZSD instructions extract the fractional portion of the single-/double-precision scalar floating-point value in and XMM register or 128-bit memory location and writes the results in the corresponding field in the destination register. The upper fields of the destination register are unaffected by the operation.

The ROUNDPD and ROUNDPD instructions round the double-/single-precision floating-point values in an XMM register or a 128-bit memory location to the nearest integer, as determined by the rounding mode specified by the 8-bit immediate control byte and write the floating-point results in the corresponding fields in a destination XMM register.

The ROUNDSD and ROUNDSS instructions round the double-/single-precision scalar floating-point value in the low position of an XMM register or a 64-bit memory location to the nearest integer, as determined by the rounding mode specified by the 8-bit immediate control byte and writes the results as a double-precision floating-point value in the low 64 bits of the destination XMM register. The upper fields of the destination register are unaffected by the operation.

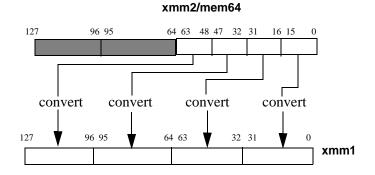

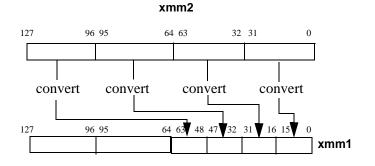

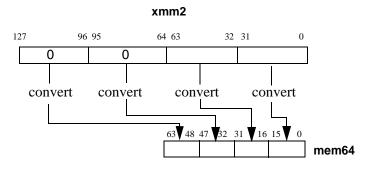

# 1.14 Convert

Two SSE5 instructions are provided to move data from/to memory and convert a single-precision floating point to 16-Bit floating-point or vice versa in one instruction. (See Section 1.5, "16-Bit Floating-Point Data Type," on page 7.)

- CVTPH2PS—Convert 16-Bit Floating-Point to Single-Precision Floating Point

- CVTPS2PH—Convert Single-Precision Floating-Point to 16-Bit Floating Point

# 2 SSE5 128-Bit Media Instructions

The following section describes the complete set of SSE5 128-media instructions. Instructions are listed alphabetically by mnemonic.

# 2.1 Notation

The notation used to denote the size and type of source and destination operands in both mnemonics and opcodes is discussed in detail in Section 2.5, "Notation," on page 37 in the AMD64 Architecture Programmer's Manual Volume 3: General Purpose and System Instructions. Mnemonic conventions that are idiosyncratic to the SSE5 instruction set have been included in Chapter 1, "New 128-Bit Instructions", in this document.

#### 2.1.1 Opcode Syntax

In addition to the opcode notational conventions specified in Section 2.5.2, "Opcode Syntax," on page 39 in the *AMD64 Architecture Programmer's Manual Volume 3: General Purpose and System Instructions*, the SSE5 instruction set requires the following notation to indicates the value of the DREX.OC0 bit:

/drex0—Indicates a DREX byte, with the OC0 bit cleared to zero.

/drex1—Indicates a DREX byte, with the OC0 bit set to one.

# 2.2 Instruction Reference

# COMPD Compare Vector Double-Precision Floating-Point

Compares each of the two double-precision floating-point values in the first source operand with the corresponding two double-precision floating-point values in the second source operand and writes the result of each comparison in the corresponding 64 bits of the destination. The result of each comparison is a 64-bit value of all 1s (TRUE) or all 0s (FALSE).

The type of comparison is specified by the four low-order bits of the immediate-byte operand, as shown in the following table.

| Imm  | ediate       | Operand Byte                                                               |                          |                                                       |  |  |  |  |  |

|------|--------------|----------------------------------------------------------------------------|--------------------------|-------------------------------------------------------|--|--|--|--|--|

| Bits | Descriptions |                                                                            |                          |                                                       |  |  |  |  |  |

| 7:4  | 0000b        | 0000b                                                                      |                          |                                                       |  |  |  |  |  |

| 3:0  | cond -       | cond – Defines the comparison operation performed on the selected operand. |                          |                                                       |  |  |  |  |  |

|      | cond         | Comparison Operation                                                       | Result if NaN<br>Operand | QNaN Operand<br>Causes Invalid<br>Operation Exception |  |  |  |  |  |

|      | 0000         | Ordered and Equal                                                          | FALSE                    | No                                                    |  |  |  |  |  |

|      | 0001         | Ordered and Less Than                                                      | FALSE                    | Yes                                                   |  |  |  |  |  |

|      | 0010         | Ordered and Not Greater Than                                               | FALSE                    | Yes                                                   |  |  |  |  |  |

|      | 0011         | Unordered                                                                  | TRUE                     | No                                                    |  |  |  |  |  |

|      | 0100         | Unordered or Not Equal                                                     | TRUE                     | No                                                    |  |  |  |  |  |

|      | 0101         | Unordered or Not Less Than                                                 | TRUE                     | Yes                                                   |  |  |  |  |  |

|      | 0110         | Unordered or Greater Than                                                  | TRUE                     | Yes                                                   |  |  |  |  |  |

|      | 0111         | Ordered                                                                    | FALSE                    | No                                                    |  |  |  |  |  |

|      | 1000         | Unordered or Equal                                                         | TRUE                     | No                                                    |  |  |  |  |  |

|      | 1001         | Unordered or Less Than                                                     | TRUE                     | No                                                    |  |  |  |  |  |

|      | 1010         | Unordered or Not Greater Than                                              | TRUE                     | No                                                    |  |  |  |  |  |

|      | 1011         | False                                                                      | FALSE                    | No                                                    |  |  |  |  |  |

|      | 1100         | Ordered and Not Equal                                                      | FALSE                    | No                                                    |  |  |  |  |  |

|      | 1101         | Ordered and Not Less Than                                                  | FALSE                    | No                                                    |  |  |  |  |  |

|      | 1110         | Ordered and Greater Than                                                   | FALSE                    | No                                                    |  |  |  |  |  |

|      | 1111         | True                                                                       | TRUE                     | No                                                    |  |  |  |  |  |

#### **COM Immediate Operand**

There are two types of comparisons, ordered and unordered. Ordered comparison operations return TRUE only if both operands are valid numbers and the numbers have the relation specified by the type of comparison and FALSE otherwise. Unordered comparison operations return TRUE if one of the operands is a NaN, or the numbers have the relation specified by the type of comparison; and FALSE

#### 43479—Rev. 3.00—August 2007

otherwise. The "True" and "False" operations return all 1s and all 0s, respectively, regardless of whether any of the source operands is a NaN.

QNaN operands generate an Invalid Operation Exception only if the comparison type is "Less than (or Equal)" and "Greater than (or Equal)". SNaN operands generate an Invalid Operation (IE) exception for all operations, including "True" and "False".

The COMPD instruction requires four operands:

#### COMPD dest, src1, src2, cond

The first instruction operand is the destination register and is an XMM register addressed by the DREX.dest field.

The COMPD instruction is an SSE5 instruction. The presence of this instruction set is indicated by a CPUID feature bit. (See the *CPUID Specification*, order# 25481.)

| Mnemonic                            | Opcode                | Description                                                                                                                                                                                                                          |

|-------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COMPD xmm1, xmm2, xmm3/mem128, imm8 | 0F 25 2D /r /drex0 ib | Compares two packed double-<br>precision floating-point values in<br>XMM2 register by XMM3 register<br>or 128-bit memory location and<br>writes 64 bits of all 1s (TRUE) or<br>all 0s (FALSE) in the destination<br>(XMM1 register). |

#### **Related Instructions**

COMPS, COMSS, COMSD, CMPPD, CMPPS, CMPSS, CMPSD, COMISD, COMISS, UCOMISD, UCOMISS

#### rFLAGS Affected

None

#### **MXCSR Flags Affected**

| ММ  | FZ                                                                                                  | R  | С  | PM | UM | ОМ | ZM | DM | IM | DAZ | PE | UE | OE | ZE | DE | IE |

|-----|-----------------------------------------------------------------------------------------------------|----|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|

|     |                                                                                                     |    |    |    |    |    |    |    |    |     |    |    |    |    | М  | М  |

| 17  | 15                                                                                                  | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6   | 5  | 4  | 3  | 2  | 1  | 0  |

| Not | Note: A flag that may be set to one or cleared to zero is M (modified). Unaffected flags are blank. |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |

#### Exceptions

| Exception                             | Real | Virtual<br>8086 | Protected | Cause of Exception                                                                                                                                     |  |  |  |  |

|---------------------------------------|------|-----------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                       | х    | х               | х         | The SSE5 instructions are not supported, as indicated by ECX bit 11 of CPUID function 8000_0001h.                                                      |  |  |  |  |

|                                       | Х    | Х               | Х         | The emulate bit (EM) of CR0 was set to 1.                                                                                                              |  |  |  |  |

| Invalid opcode, #UD                   | Х    | х               | х         | The operating-system FXSAVE/FXRSTOR support bit (OSFXSR) of CR4 was cleared to 0.                                                                      |  |  |  |  |

|                                       | х    | х               | х         | There was an unmasked SIMD floating-point<br>exception while CR4.OSXMMEXCPT = 0.<br>See <i>SIMD Floating-Point Exceptions</i> , below, for<br>details. |  |  |  |  |

| Device not available,<br>#NM          | х    | Х               | Х         | The task-switch bit (TS) of CR0 was set to 1.                                                                                                          |  |  |  |  |

| Stack, #SS                            | х    | х               | Х         | A memory address exceeded the stack segment limit or was non-canonical.                                                                                |  |  |  |  |

|                                       | Х    | х               | х         | A memory address exceeded a data segment limit or was non-canonical.                                                                                   |  |  |  |  |

| General protection, #GP               |      |                 | Х         | A null data segment was used to reference memory.                                                                                                      |  |  |  |  |

|                                       | Х    | х               | х         | The memory operand was not aligned on a 16-byte boundary while MXCSR.MM=0.                                                                             |  |  |  |  |

| Page fault, #PF                       |      | Х               | Х         | A page fault resulted from the execution of the instruction.                                                                                           |  |  |  |  |

| Alignment Check, #AC                  |      | х               | х         | An unaligned memory reference was performed while<br>alignment checking was enabled while<br>MXCSR.MM=1.                                               |  |  |  |  |

| SIMD Floating-Point<br>Exception, #XF | х    | х               | х         | There was an unmasked SIMD floating-point exception while CR4.OSXMMEXCPT=1. See <i>SIMD Floating-Point Exceptions</i> , below, for details.            |  |  |  |  |

| SIMD Floating-Point Exceptions        |      |                 |           |                                                                                                                                                        |  |  |  |  |

|                                       | Х    | Х               | Х         | A source operand was an SNaN value.                                                                                                                    |  |  |  |  |

| Invalid-operation<br>exception (IE)   | х    | х               | х         | A source operand was a QNaN value and the comparison does not allow QNaN values (refer to Table on page 18).                                           |  |  |  |  |

| Denormalized-operand x                |      | Х               | Х         | A source operand was a denormal value.                                                                                                                 |  |  |  |  |

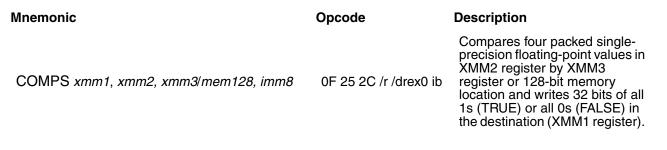

# COMPS Compare Vector Single-Precision Floating-Point

Compares each of the four single-precision floating-point values in the first source operand with the corresponding four single-precision floating-point values in the second source operand and writes the result of each comparison in the corresponding 32 bits of the destination. The result of each comparison is a 32-bit value of all 1s (TRUE) or all 0s (FALSE).

The type of comparison is specified by the four low-order bits of the immediate-byte operand, as shown in the following table.

| lmm  | mmediate Operand Byte                                                      |                               |                          |                                                       |  |  |  |  |  |  |

|------|----------------------------------------------------------------------------|-------------------------------|--------------------------|-------------------------------------------------------|--|--|--|--|--|--|

| Bits | Descriptions                                                               |                               |                          |                                                       |  |  |  |  |  |  |

| 7:4  | 0000b                                                                      |                               |                          |                                                       |  |  |  |  |  |  |

| 3:0  | cond – Defines the comparison operation performed on the selected operand. |                               |                          |                                                       |  |  |  |  |  |  |

|      | cond                                                                       | Comparison Operation          | Result if NaN<br>Operand | QNaN Operand<br>Causes Invalid<br>Operation Exception |  |  |  |  |  |  |

|      | 0000                                                                       | Ordered and Equal             | FALSE                    | No                                                    |  |  |  |  |  |  |

|      | 0001                                                                       | Ordered and Less Than         | FALSE                    | Yes                                                   |  |  |  |  |  |  |

|      | 0010                                                                       | Ordered and Not Greater Than  | FALSE                    | Yes                                                   |  |  |  |  |  |  |

|      | 0011                                                                       | Unordered                     | TRUE                     | No                                                    |  |  |  |  |  |  |

|      | 0100                                                                       | Unordered or Not Equal        | TRUE                     | No                                                    |  |  |  |  |  |  |

|      | 0101                                                                       | Unordered or Not Less Than    | TRUE                     | Yes                                                   |  |  |  |  |  |  |

|      | 0110                                                                       | Unordered or Greater Than     | TRUE                     | Yes                                                   |  |  |  |  |  |  |

|      | 0111 Ordered                                                               |                               | FALSE                    | No                                                    |  |  |  |  |  |  |

|      | 1000                                                                       | Unordered or Equal            | TRUE                     | No                                                    |  |  |  |  |  |  |

|      | 1001                                                                       | Unordered or Less Than        | TRUE                     | No                                                    |  |  |  |  |  |  |

|      | 1010                                                                       | Unordered or Not Greater Than | TRUE                     | No                                                    |  |  |  |  |  |  |

|      | 1011                                                                       | False                         | FALSE                    | No                                                    |  |  |  |  |  |  |

|      | 1100                                                                       | Ordered and Not Equal         | FALSE                    | No                                                    |  |  |  |  |  |  |

|      | 1101                                                                       | Ordered and Not Less Than     | FALSE                    | No                                                    |  |  |  |  |  |  |

|      | 1110                                                                       | Ordered and Greater Than      | FALSE                    | No                                                    |  |  |  |  |  |  |

|      | 1111                                                                       | True                          | TRUE                     | No                                                    |  |  |  |  |  |  |

#### **COM Immediate Operand**

Ordered comparison operations return TRUE only if both operands are valid numbers and the numbers have the relation specified by the type of comparison and FALSE otherwise. Unordered comparison operations return TRUE if one of the operands is a NaN, or the numbers have the relation specified by the type of comparison; and FALSE otherwise. The "True" and "False" operations return all 1s and all 0s, respectively, regardless of whether any of the source operands is a NaN.

QNaN operands generate an Invalid Operation Exception only if the comparison type is "(Not) Less than (or Equal)". SNaN operands generate an Invalid Operation (IE) exception for all operations, including "True" and "False".

The COMPS instruction requires four operands:

COMPS dest, src1, src2, cond

The first instruction operand is the destination register and is an XMM register addressed by the DREX.dest field.

The COMPS instruction is an SSE5 instruction. The presence of this instruction set is indicated by a CPUID feature bit. (See the *CPUID Specification*, order# 25481.)

#### **Related Instructions**

COMPD, COMSS, COMSD, CMPPD, CMPPS, CMPSS, CMPSD, COMISD, COMISS, UCOMISD, UCOMISS

#### rFLAGS Affected

None

### **MXCSR Flags Affected**

| ММ  | FZ                                                                                                  | R  | С  | PM | UM | ОМ | ZM | DM | IM | DAZ | PE | UE | OE | ZE | DE | IE |

|-----|-----------------------------------------------------------------------------------------------------|----|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|

|     |                                                                                                     |    |    |    |    |    |    |    |    |     |    |    |    |    | М  | М  |

| 17  | 15                                                                                                  | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6   | 5  | 4  | 3  | 2  | 1  | 0  |

| Not | Note: A flag that may be set to one or cleared to zero is M (modified). Unaffected flags are blank. |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |

| Exception                              | Real | Virtual<br>8086 | Protected    | Cause of Exception                                                                                                                                     |

|----------------------------------------|------|-----------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                        | х    | х               | х            | The SSE5 instructions are not supported, as indicated by ECX bit 11 of CPUID function 8000_0001h.                                                      |

|                                        | Х    | Х               | Х            | The emulate bit (EM) of CR0 was set to 1.                                                                                                              |

| Invalid opcode, #UD                    | Х    | Х               | Х            | The operating-system FXSAVE/FXRSTOR support bit (OSFXSR) of CR4 was cleared to 0.                                                                      |

|                                        | х    | х               | х            | There was an unmasked SIMD floating-point<br>exception while CR4.OSXMMEXCPT = 0.<br>See <i>SIMD Floating-Point Exceptions</i> , below, for<br>details. |

| Device not available,<br>#NM           | Х    | Х               | Х            | The task-switch bit (TS) of CR0 was set to 1.                                                                                                          |

| Stack, #SS                             | Х    | Х               | Х            | A memory address exceeded the stack segment limit or was non-canonical.                                                                                |

|                                        | Х    | Х               | х            | A memory address exceeded a data segment limit or was non-canonical.                                                                                   |

| General protection, #GP                |      |                 | Х            | A null data segment was used to reference memory.                                                                                                      |

|                                        | Х    | х               | х            | The memory operand was not aligned on a 16-byte boundary while MXCSR.MM=0.                                                                             |

| Page fault, #PF                        |      | Х               | Х            | A page fault resulted from the execution of the instruction.                                                                                           |

| Alignment Check, #AC                   |      | х               | х            | An unaligned memory reference was performed while<br>alignment checking was enabled while<br>MXCSR.MM=1.                                               |

| SIMD Floating-Point<br>Exception, #XF  | х    | х               | х            | There was an unmasked SIMD floating-point<br>exception while CR4.OSXMMEXCPT=1.<br>See <i>SIMD Floating-Point Exceptions</i> , below, for<br>details.   |

|                                        |      | SIM             | D Floating-F | Point Exceptions                                                                                                                                       |

|                                        | Х    | Х               | Х            | A source operand was an SNaN value.                                                                                                                    |

| Invalid-operation<br>exception (IE)    | х    | х               | х            | A source operand was a QNaN value and the comparison does not allow QNaN values (refer to Table on page 18).                                           |

| Denormalized-operand<br>exception (DE) | х    | Х               | Х            | A source operand was a denormal value.                                                                                                                 |

# COMSD Compare Scalar Double-Precision Floating-Point

Compares the double-precision floating-point value in the low-order 64 bits of the first source operand with the double-precision floating-point value in the low-order 64 bits of the second source operand and writes the result of the comparison in the low-order 64 bits of the destination. The high-order quadword of the destination is cleared to 0s. The result of the comparison is a 64-bit value of all 1s (TRUE) or all 0s (FALSE).

The type of comparison is specified by the four low-order bits of the immediate-byte operand, as shown in the following table.

| Bits | Descri | Operand Byte                       |                          |                                                       |  |  |

|------|--------|------------------------------------|--------------------------|-------------------------------------------------------|--|--|

| 7:4  | 0000b  |                                    |                          |                                                       |  |  |

| 3:0  |        | - Defines the comparison operation | performed on the         | e selected operand.                                   |  |  |

|      | cond   | Comparison Operation               | Result if NaN<br>Operand | QNaN Operand<br>Causes Invalid<br>Operation Exception |  |  |

|      | 0000   | Ordered and Equal                  | FALSE                    | No                                                    |  |  |

|      | 0001   | Ordered and Less Than              | FALSE                    | Yes                                                   |  |  |

|      | 0010   | Ordered and Not Greater Than       | FALSE                    | Yes                                                   |  |  |

|      | 0011   | Unordered                          | TRUE                     | No                                                    |  |  |

|      | 0100   | Unordered or Not Equal             | TRUE                     | No                                                    |  |  |

|      | 0101   | Unordered or Not Less Than         | TRUE                     | Yes                                                   |  |  |

|      | 0110   | Unordered or Greater Than          | TRUE                     | Yes                                                   |  |  |

|      | 0111   | Ordered                            | FALSE                    | No                                                    |  |  |

|      | 1000   | Unordered or Equal                 | TRUE                     | No                                                    |  |  |

|      | 1001   | Unordered or Less Than             | TRUE                     | No                                                    |  |  |

|      | 1010   | Unordered or Not Greater Than      | TRUE                     | No                                                    |  |  |

|      | 1011   | False                              | FALSE                    | No                                                    |  |  |

|      | 1100   | Ordered and Not Equal              | FALSE                    | No                                                    |  |  |

|      | 1101   | Ordered and Not Less Than          | FALSE                    | No                                                    |  |  |