# UPI-452 CHMOS PROGRAMMABLE I/O PROCESSOR

## 83C452 - 8K imes 8 Mask Programmable Internal ROM

## 80C452 - External ROM/EPROM

- 83C452/80C452:3.5 to 14 MHz Clock Rate

- Software Compatible with the MCS-51 Family

- 128-Byte Bi-Directional FIFO Slave Interface

- Two DMA Channels

- 256 × 8-Bit Internal RAM

- 34 Additional Special Function Registers

- 40 Programmable I/O Lines

- Two 16-Bit Timer/Counters

- Boolean Processor

- Bit Addressable RAM

- 8 Interrupt Sources

- Programmable Full Duplex Serial Channel

- 64K Program Memory Space

- 64K Data Memory Space

- 68-Pin PGA and PLCC

(See Packaging Spec., Order: #231369)

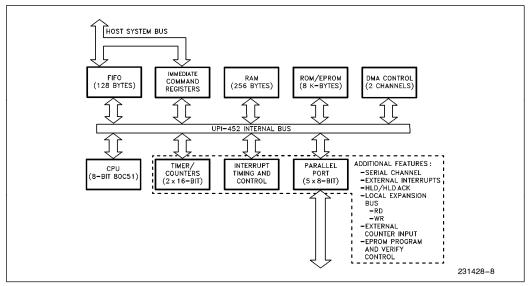

The Intel UPI-452 (Universal Peripheral Interface) is a 68 pin CHMOS Slave I/O Processor with a sophisticated bi-directional FIFO buffer interface on the slave bus and a two channel DMA processor on-chip. The UPI-452 is the newest member of Intel's UPI family of products. It is a general-purpose slave I/O Processor that allows the designer to grow a customized interface solution.

The UPI-452 contains a complete 80C51 with twice the on-chip data and program memory. The sophisticated slave FIFO module acts as a buffer between the UPI-452 internal CPU and the external host CPU. To both the external host and the internal CPU, the FIFO module looks like a bi-directional bottomless buffer that can both read and write data. The FIFO manages the transfer of data independent of the UPI-452 core CPU and generates an interrupt or DMA request to either CPU, host or internal, as a FIFO service request.

The FIFO consists of two channels:the Input FIFO and the Output FIFO. The division of the FIFO module array, 128 bytes, between Input channel and Output channel is programmable by the user. Each FIFO byte has an additional logical ninth bit to distinguish between a data byte and a Data Stream Command byte. Additionally, Immediate Commands allow direct, interrupt driven, bi-directional communication between the UPI-452 internal CPU and external host CPU, bypassing the FIFO.

The on-chip DMA processor allows high speed data transfers from one writeable memory space to another. As many as 64K bytes can be transferred in a single DMA operation. Three distinct memory spaces may be used in DMA operations; Internal Data Memory, External Data Memory, and the Special Function Registers (including the FIFO IN, FIFO OUT, and Serial Channel Special Functions Registers).

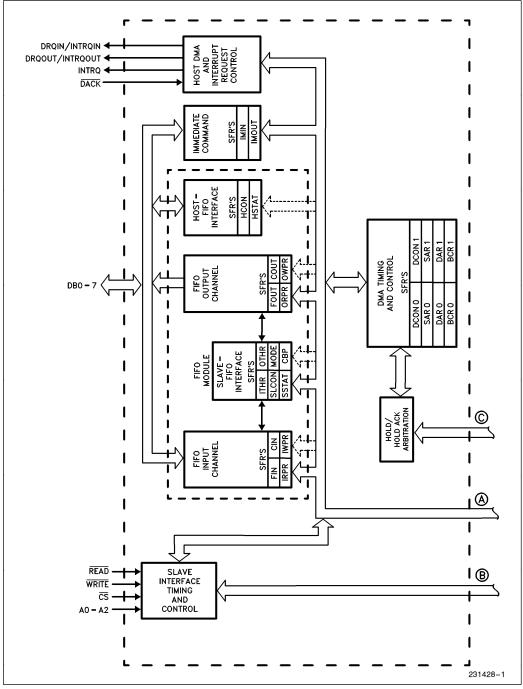

Figure 1. Architectural Block Diagram

Figure 1. Architectural Block Diagram (Continued)

# TABLE OF CONTENTS

| CONTENTS                                                                     | PAGE |

|------------------------------------------------------------------------------|------|

| Introduction                                                                 | 1    |

| Table of Contents                                                            | 4    |

| List of Tables and Figures                                                   |      |

| Pin Description                                                              |      |

| Architectural Overview                                                       |      |

| Introduction                                                                 | 10   |

| FIFO Buffer Interface                                                        | 10   |

| FIFO Programmable Features                                                   | 11   |

| Immediate Commands                                                           | 12   |

| DMA                                                                          |      |

| FIFO/Slave Interface Functional Description                                  | 12   |

| Overview                                                                     | 12   |

| Input FIFO Channel                                                           |      |

| Output FIFO Channel                                                          |      |

| Immediate Commands                                                           | 16   |

| Host & Slave Interface Special Function Registers                            | 18   |

| Slave Interface Special Function Registers                                   | 18   |

| External Host Interface Special Function Registers                           |      |

| FIFO Module—External Host Interface                                          |      |

| Overview                                                                     |      |

| Slave Interface Address Decoding                                             |      |

| Interrupts to the Host                                                       | 22   |

| DMA Requests to the Host                                                     | 24   |

| FIFO Module—Internal CPU Interface                                           |      |

| Overview                                                                     |      |

| Internal CPU Access to FIFO via Software Instructions                        |      |

| General Purpose DMA Channels                                                 |      |

| Overview                                                                     |      |

| Architecture                                                                 |      |

| DMA Special Function Registers                                               |      |

| DMA Transfer Modes External Memory DMA                                       |      |

| Latency                                                                      |      |

| DMA Interrupt Vectors                                                        |      |

| Interrupts When DMA is Active                                                |      |

| DMA Arbitration                                                              | 30   |

| Interrupts                                                                   |      |

| Overview                                                                     |      |

| FIFO Module Interrupts to Internal CPU                                       |      |

| Interrupt Enabling and Priority                                              |      |

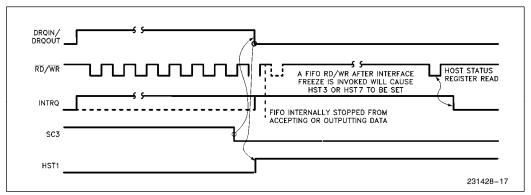

| FIFO—External Host Interface FIFO DMA Freeze Mode                            | 35   |

| Overview                                                                     |      |

| Initialization                                                               |      |

| Invoking FIFO DMA Freeze Mode During Normal Operation                        |      |

| FIFO Module Special Function Register Operation During FIFO DMA Freeze Mode. | 37   |

| Internal CPU Read & Write of the FIFO During FIFO DMA Freeze Mode            | 41   |

| Memory Organization                                                          |      |

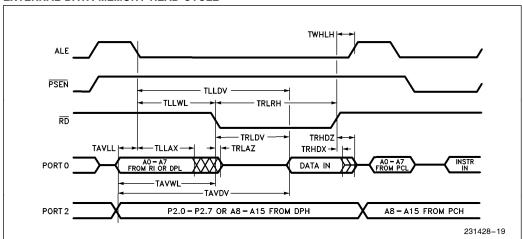

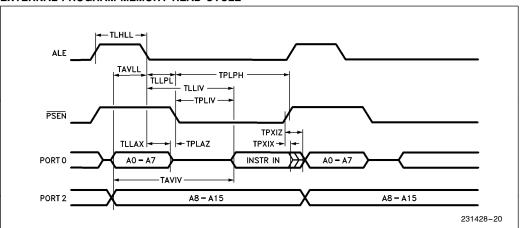

| Accessing External Memory                                                    | 41   |

| Miscellaneous Special Function Register Descriptions                         |      |

# LIST OF TABLES AND FIGURES

| Figures:                                         |                                                                                                                                                                                                                                                                                                                                                                        |                            |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 1.                                               | Architectural Block Diagram                                                                                                                                                                                                                                                                                                                                            | 2                          |

| 2.                                               | UPI 452 68-Pin PLCC Pinout Diagram                                                                                                                                                                                                                                                                                                                                     | 6                          |

| 3.                                               | UPI-452 Conceptual Block Diagram                                                                                                                                                                                                                                                                                                                                       |                            |

| 4.                                               | UPI-452 Functional Block Diagram                                                                                                                                                                                                                                                                                                                                       |                            |

| 5.                                               | Input FIFO Channel Functional Block Diagram                                                                                                                                                                                                                                                                                                                            | 13                         |

| 6.                                               | Output FIFO Channel Functional Block Diagram                                                                                                                                                                                                                                                                                                                           |                            |

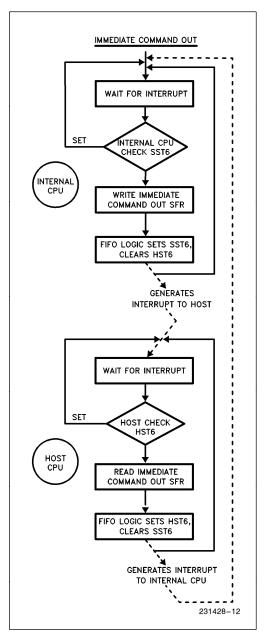

| 7a                                               | Handshake Mechanisms for Handling Immediate Command IN Flowchart                                                                                                                                                                                                                                                                                                       |                            |

|                                                  | Handshake Mechanisms for Handling Immediate Command OUT Flowchart                                                                                                                                                                                                                                                                                                      |                            |

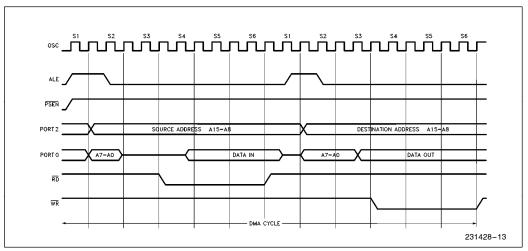

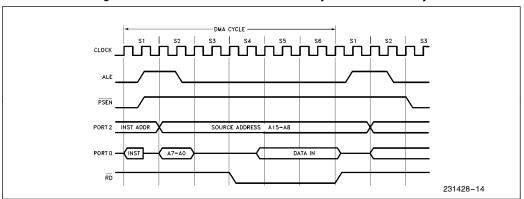

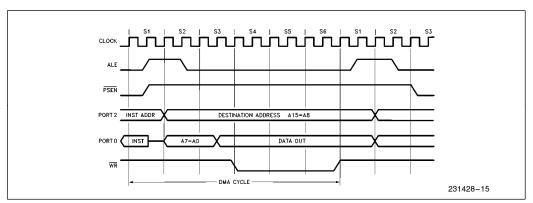

| 8.                                               | DMA Transfer from: External to External Memory                                                                                                                                                                                                                                                                                                                         |                            |

| 9.                                               | DMA Transfer from: External to Internal Memory                                                                                                                                                                                                                                                                                                                         |                            |

| 10.                                              | DMA Transfer from: Internal to External Memory                                                                                                                                                                                                                                                                                                                         |                            |

| 11.                                              | DMA Transfer Waveform: Internal to Internal Memory                                                                                                                                                                                                                                                                                                                     | 32                         |

| 12.                                              | Disabling FIFO to Host Slave Interface Timing Diagram                                                                                                                                                                                                                                                                                                                  |                            |

|                                                  |                                                                                                                                                                                                                                                                                                                                                                        |                            |

| Tables:                                          |                                                                                                                                                                                                                                                                                                                                                                        |                            |

| 1.                                               | Input FIFO Channel Registers                                                                                                                                                                                                                                                                                                                                           | 12                         |

| 2.                                               | Output FIFO Channel Registers                                                                                                                                                                                                                                                                                                                                          |                            |

| 3.                                               | UPI-452 Address Decoding                                                                                                                                                                                                                                                                                                                                               |                            |

| 4.                                               | of 1-402 /tddicos becoung                                                                                                                                                                                                                                                                                                                                              | 20                         |

|                                                  | DMA Accessible Special Function Registers                                                                                                                                                                                                                                                                                                                              | 26                         |

| 5                                                | DMA Accessible Special Function Registers                                                                                                                                                                                                                                                                                                                              | 26                         |

| 5.<br>6                                          | DMA Mode Control - PCON SFR                                                                                                                                                                                                                                                                                                                                            | 29                         |

| 6.                                               | DMA Mode Control - PCON SFR                                                                                                                                                                                                                                                                                                                                            | 29<br>32                   |

| 6.<br>7.                                         | DMA Mode Control - PCON SFR Interrupt Priority Interrupt Vector Addresses                                                                                                                                                                                                                                                                                              | 29<br>32<br>32             |

| 6.<br>7.<br>8.                                   | DMA Mode Control - PCON SFR Interrupt Priority Interrupt Vector Addresses Slave Bus Interface Status During FIFO DMA Freeze Mode                                                                                                                                                                                                                                       | 29<br>32<br>32             |

| 6.<br>7.<br>8.<br>9.                             | DMA Mode Control - PCON SFR Interrupt Priority Interrupt Vector Addresses Slave Bus Interface Status During FIFO DMA Freeze Mode FIFO SFR's Characteristics During FIFO DMA Freeze Mode                                                                                                                                                                                | 29<br>32<br>35<br>38       |

| 6.<br>7.<br>8.<br>9.<br>10.                      | DMA Mode Control - PCON SFR Interrupt Priority Interrupt Vector Addresses Slave Bus Interface Status During FIFO DMA Freeze Mode FIFO SFR's Characteristics During FIFO DMA Freeze Mode Threshold SFRs Range of Values and Number of Bytes to be Transferred                                                                                                           |                            |

| 6.<br>7.<br>8.<br>9.<br>10.                      | DMA Mode Control - PCON SFR Interrupt Priority Interrupt Vector Addresses Slave Bus Interface Status During FIFO DMA Freeze Mode FIFO SFR's Characteristics During FIFO DMA Freeze Mode Threshold SFRs Range of Values and Number of Bytes to be Transferred Internal Memory Addressing                                                                                | 29<br>32<br>35<br>38<br>39 |

| 6.<br>7.<br>8.<br>9.<br>10.<br>11a               | DMA Mode Control - PCON SFR Interrupt Priority Interrupt Vector Addresses Slave Bus Interface Status During FIFO DMA Freeze Mode FIFO SFR's Characteristics During FIFO DMA Freeze Mode Threshold SFRs Range of Values and Number of Bytes to be Transferred Internal Memory Addressing 80C51 Special Function Registers                                               |                            |

| 6.<br>7.<br>8.<br>9.<br>10.<br>11a<br>11b        | DMA Mode Control - PCON SFR Interrupt Priority Interrupt Vector Addresses Slave Bus Interface Status During FIFO DMA Freeze Mode FIFO SFR's Characteristics During FIFO DMA Freeze Mode Threshold SFRs Range of Values and Number of Bytes to be Transferred Internal Memory Addressing 80C51 Special Function Registers UPI-452 Additional Special Function Registers |                            |

| 6.<br>7.<br>8.<br>9.<br>10.<br>11a<br>11b<br>11c | DMA Mode Control - PCON SFR Interrupt Priority Interrupt Vector Addresses Slave Bus Interface Status During FIFO DMA Freeze Mode FIFO SFR's Characteristics During FIFO DMA Freeze Mode Threshold SFRs Range of Values and Number of Bytes to be Transferred Internal Memory Addressing 80C51 Special Function Registers                                               |                            |

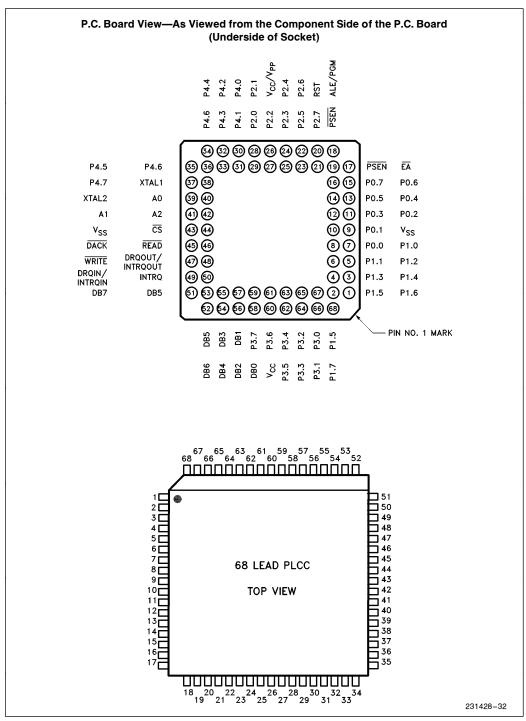

Figure 2. UPI 452 68-Pin PLCC Pinout Diagram

## **UPI MICROCONTROLLER FAMILY**

The UPI-452 joins the current members of the UPI microcontroller family. UPI's are derivatives of the MCS<sup>TM</sup> family of microcontrollers. Because of their on-chip system bus interface, UPI's are designed to be system bus "slaves", while their microcontroller counterparts are intended as system bus "masters".

These UPI Microcontrollers are fully supported by Intel's development tools (ICE, ASM and PLM).

## **Packaging**

The 80C452/83C452 is available in a 68-pin PLCC package.

| UPI Family<br>(Slave<br>Configuration) | MCS Family<br>(Master<br>Configuration) | Speed  | RAM<br>(Bytes) | ROM<br>(Bytes) |

|----------------------------------------|-----------------------------------------|--------|----------------|----------------|

| 80C452                                 | 80C51                                   | 12 MHz | 256            | _              |

| 83C452                                 | 80C51                                   | 12 MHz | 256            | 8K             |

| 80C452-1                               | 80C51                                   | 14 MHz | 256            | _              |

| 83C452-1                               | 80C51                                   | 14 MHz | 256            | 8K             |

## **UPI-452 PIN DESCRIPTIONS**

| Symbol                                                                  | Pin #                                       | Type | Name and Function                                                                                                                                                                                         |

|-------------------------------------------------------------------------|---------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>SS</sub>                                                         | 9/43                                        | I    | Circuit Ground.                                                                                                                                                                                           |

| V <sub>CC</sub>                                                         | 60                                          | I    | +5V power supply during normal and idle mode operation. It is also the standby power pin for power down mode.                                                                                             |

| XTAL1                                                                   | 38                                          | I    | Input to the oscillator's high gain amplifier. A crystal or external source can be used.                                                                                                                  |

| XTAL2                                                                   | 39                                          | 0    | Output from the high gain amplifier.                                                                                                                                                                      |

| Port 0<br>(AD0-AD7)<br>P0.0<br>.1<br>.2<br>.3<br>.4<br>.5<br>.6<br>P0.7 | 8<br>10<br>11<br>12<br>13<br>14<br>15<br>16 | I/O  | Port 0 is an 8-bit open drain bi-directional I/O port. Port 0 can sink eight LS TTL inputs. It is also the multiplexed low-order address and data local expansion bus during accesses to external memory. |

7

## **UPI-452 PIN DESCRIPTIONS** (Continued)

| Overhal Bin / Type News and Function                                                 |                                              |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|--------------------------------------------------------------------------------------|----------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol                                                                               | Pin #                                        | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| Port 1<br>(A0-A7)<br>(HLD, HLDA)<br>P1.0<br>.1<br>.2<br>.3<br>.4<br>.5<br>.6<br>P1.7 | 7<br>6<br>5<br>4<br>3<br>2<br>1<br>68        | 1/0  | Port 1 is an 8-bit quasi-bi-directional I/O port. Port 1 can sink four LS TTL inputs. The alternate functions can only be activated if the corresponding bit latch in the port SFR contains a 1. Otherwise, the port pin is stuck at 0. Pins P1.5 and P1.6 are multiplexed with HLD and HLDA respectively whose functions are defined as below:  Port Pin Alternate Function P1.5 HLD —Local bus hold input/output signal P1.6 HLDA —Local bus hold acknowledge input                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| Port 2<br>(A8-A15)<br>P2.0<br>.1<br>.2<br>.3<br>.4<br>.5<br>.6                       | 29<br>28<br>27<br>25<br>24<br>23<br>22<br>21 | I/O  | Port 2 is an 8-bit quasi-bi-directional I/O port. It also emits the high-<br>order 8 bits of address when accessing local expansion bus<br>external memory. Port 2 can sink four LS TTL inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| Port 3<br>P3.0<br>.1<br>.2<br>.3<br>.4<br>.5<br>.6<br>P3.7                           | 67<br>66<br>65<br>64<br>63<br>62<br>61<br>59 | 1/0  | Port 3 is an 8-bit quasi-bi-directional I/O port. It is also multiplexed with the interrupt, timer, local serial channel, RD/ and WR/ functions that are used by various options. The alternate functions can only be activated if the corresponding bit latch in the port SFR contains a 1. Otherwise, the port pin is stuck at 0. Port 3 can sink four LS TTL inputs. The alternate functions assigned to the pins of Port 3 are as follows:  Port Pin Alternate Function P3.0 RxD — Serial input port P3.1 TxD — Serial output port P3.2 INT0 — Interrupt 0 Input P3.3 INT1 — Interrupt 1 Input P3.4 T0 — Input to counter 0 P3.5 T1 — Input to counter 1 P3.6 WR/ — The write control signal latches the data from Port 0 outputs into the External Data Memory on the local bus.  P3.7 RD/ — The read control signal latches the data from Port 0 outputs on the local bus. |  |  |  |

## **UPI-452 PIN DESCRIPTIONS** (Continued)

| Symbol                           | Pin #                                        | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------|----------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Port 4<br>P4.0                   | 30                                           | 1/0  | Port 4 is an 8-bit quasi-bi-directional I/O port. Port 4 can sink/<br>source four TTL inputs.                                                                                                                                                                                                                                                                          |

| .1<br>.2<br>.3<br>.4<br>.5<br>.6 | 32<br>33<br>34<br>35<br>36<br>37             |      |                                                                                                                                                                                                                                                                                                                                                                        |

| RST                              | 20                                           | I    | A high level on this pin for two machine cycles while the oscillator is running resets the device. An internal pulldown resistor permits Power-on reset using only a capacitor connected to $V_{\rm CC}$ . This pin does not receive the power down voltage as is the case for HMOS MCS-51 family members. This function has been transferred to the $V_{\rm CC}$ pin. |

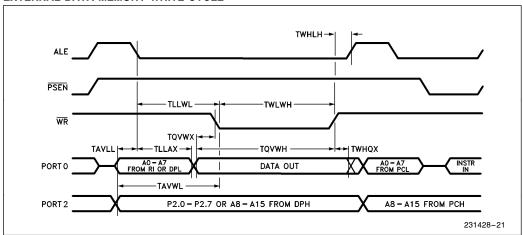

| ALE                              | 18                                           | 0    | Provides Address Latch Enable output used for latching the address into external memory during normal operation. ALE can sink/source eight LS TTL inputs.                                                                                                                                                                                                              |

| PSEN                             | 19                                           | 0    | The Program Store Enable output is a control signal that enables the external Program Memory to the bus during normal fetch operation. PSEN can sink/source eight LS TTL inputs.                                                                                                                                                                                       |

| EA                               | 17                                           | I    | When held at TTL high level, the UPI-452 executes instructions from the internal ROM when the PC is less than 8192 (8K, 2000H). When held at a TTL low level, the UPI-452 fetches all instructions from external Program Memory.                                                                                                                                       |

| DB0 DB1 DB2 DB3 DB4 DB5 DB6 DB7  | 58<br>57<br>56<br>55<br>54<br>53<br>52<br>51 | 1/0  | Host Bus Interface is an 8-bit bi-directional bus. It is used to transfer data and commands between the UPI-452 and the host processor. This bus can sink/source eight LS TTL inputs.                                                                                                                                                                                  |

| CS                               | 44                                           | I    | This pin is the Chip Select of the UPI-452.                                                                                                                                                                                                                                                                                                                            |

| A0<br>A1<br>A2                   | 40<br>41<br>42                               | I    | These three address lines are used to interface with the host system. They define the UPI-452 operations. The interface is compatible with the Intel microprocessors and the MULTIBUS.                                                                                                                                                                                 |

| READ                             | 46                                           | l    | This pin is the read strobe from the host CPU. Activating this pin causes the UPI-452 to place the contents of the Output FIFO (either a command or data) or the Host Status/Control Special Function Register on the Slave Data Bus.                                                                                                                                  |

| WRITE                            | 47                                           | I    | This pin is the write strobe from the host. Activating this pin will cause the value on the Slave Data Bus to be written into the register specified by A0–A2.                                                                                                                                                                                                         |

| DRQIN/<br>INTRQIN                | 49                                           | 0    | This pin requests an input transfer from the host system whenever the Input Channel requires data.                                                                                                                                                                                                                                                                     |

| DRQOUT/<br>INTRQOUT              | 48                                           | 0    | This output pin requests an output transfer whenever the Output Channel requires service. If the external host to UPI-452 DMA is enabled, and a Data Stream Command is at the Output FIFO, DRQOUT is deactivated and INTRQ is activated (see 'GENERAL PURPOSE DMA CHANNELS' section).                                                                                  |

## **UPI-452 PIN DESCRIPTIONS (Continued)**

| Symbol          | Pin # | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTRQ           | 50    | 0    | This output pin is used to interrupt the host processor when an Immediate Command Out or an error condition is encountered. It is also used to interrupt the host processor when the FIFO requests service if the DMA is disabled and INTRQIN and INTRQOUT are not used.                                                                                                                                                                                |

| DACK            | 45    | l    | This pin is the DMA acknowledge for the host bus interface Input and Output Channels. When activated, a write command will cause the data on the Slave Data Bus to be written as data to the Input Channel (to the Input FIFO). A read command will cause the Output Channel to output data (from the Output FIFO) on to the Slave Data Bus. This pin should be driven high (+5V) in systems which do not have a DMA controller (see Address Decoding). |

| V <sub>CC</sub> | 26    | I    | +5V power supply during operation.                                                                                                                                                                                                                                                                                                                                                                                                                      |

## **ARCHITECTURAL OVERVIEW**

## Introduction

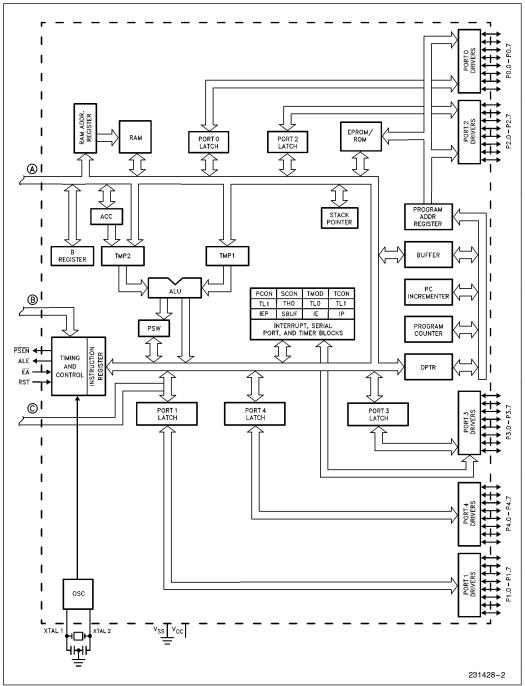

The UPI-452 slave microcontroller incorporates an 80C51 with double the program and data memory, a slave interface which allows it to be connected directly to the host system bus as a peripheral, a FIFO buffer module, a two channel DMA processor, and a fifth I/O port (Figure 3). The UPI-452 retains all of the 80C51 architecture, and is fully compatible with the MCS-51 instruction set.

The Special Function Register (SFR) interface concept introduced in the MCS-51 family of microcontrollers has been expanded in the UPI-452. To the 20 Special Function Registers of the MCS-51, the UPI-452 adds 34 more. These additional Special Function Registers, like those of the MCS-51, provide access to the UPI-452 functional elements including the FIFO, DMA and added interrupt capabilities. Several of the 80C51 core Special Function Registers have also been expanded to support added features of the UPI-452.

This data sheet describes the unique features of the UPI-452. Refer to the 80C51 data sheet for a de-

scription of the UPI-452's core CPU functional blocks including;

- Timers/Counters

- I/O Ports

- Interrupt timing and control (other than FIFO and DMA interrupts)

- Serial Channel

- Local Expansion Bus

- Program/Data Memory structure

- Power-Saving Modes of Operation

- CHMOS Features

- Instruction Set

Figure 3 contains a conceptual block diagram of the UPI-452. Figure 4 provides a functional block diagram.

## **FIFO Buffer Interface**

A unique feature of the UPI-452 is the incorporation of a 128 byte FIFO array at the host-slave interface. The FIFO allows asynchronous bi-directional transfers between the host CPU and the internal CPU.

Figure 3. UPI-452 Conceptual Block Diagram

Figure 4. UPI-452 Functional Block Diagram

The division of the 128 bytes between Input and Output channels is user programmable allowing maximum flexibility. If the entire 128 byte FIFO is allocated to the Input channel, a high performance Host can transfer up to 128 bytes at one time, then dedicate its resources to other functions while the internal CPU processes the data in the FIFO. Various handshake signals allow the external Host to operate independently and without frequent monitoring of the UPI-452 internal CPU. The FIFO Buffer insures that the slave processor receives data in the same order that it was sent by the host without the need to keep track of addresses. Three slave bus interface handshake methods are supported by the UPI-452: DMA, Interrupt and Polled.

The FIFO is nine bits wide. The ninth bit acts as a command/data flag. Commands written to the FIFO by either the host or internal CPU are called Data Stream Commands or DSCs. DSCs are written to the input FIFO by the Host via a unique external address. DSCs are written to the output FIFO by the internal CPU via the COMMAND OUT Special Function Register (SFR). When encountered by the host or internal CPU a Data Stream Command can be used as an address vector to user defined service routines. DSCs provide synchronization of data and commands between the Host and internal CPU.

## FIFO PROGRAMMABLE FEATURES

## Size of Input/Output Channels

The 128 bytes of FIFO space can be allocated between the Input and Output channels via the Chan-

nel Boundary Pointer (CBP) SFR. This register contains the number of address locations assigned to the Input channel. The remaining address locations are automatically assigned to the Output FIFO. The CBP SFR can only be programmed by the internal CPU during FIFO DMA Freeze Mode (See FIFO-External Host Interface FIFO DMA Freeze Mode description). The CBP is initialized to 40H (64 bytes) upon reset.

The number in the Channel Boundary Pointer SFR is actually the first address location of the Output FIFO. Writing to the CBP SFR reassigns the Input and Output FIFO address space. Whenever the CBP is written, the Input FIFO pointers are reset to zero and the Output FIFO pointers are set to the value in the CBP SFR.

All of the FIFO space may be assigned to one channel. In such a situation the other channel's data path consists of a single SFR (FIFO IN/COMMAND IN or FIFO OUT/COMMAND OUT SFR) location.

| CBP<br>Register | Input FIFO<br>Size | Output FIFO<br>Size |

|-----------------|--------------------|---------------------|

| 0               | 1                  | 128                 |

| 1               | 1                  | 128                 |

| 2               | 2                  | 126                 |

| 3               | 3                  | 125                 |

| 4               | 4                  | 124                 |

| •               | •                  | •                   |

| 7B              | 123                | 5                   |

| 7C              | 124                | 4                   |

| 7D              | 125                | 3                   |

| 7E              | 128                | 1                   |

| 7F              | 128                | 1                   |

#### FIFO Read/Write Pointers

These normally operate in auto-increment (and auto-rollover) mode, but can be reassigned by the internal CPU during FIFO DMA Freeze Mode (See FIFO-External Host Interface FIFO DMA Freeze Mode description).

## **Threshold Register**

The Input FIFO Threshold SFR contains the number of empty bytes that must be available in the Input FIFO to generate a Host interrupt. The Output FIFO Threshold SFR contains the number of bytes, data and/or DSC(s), that must be in the FIFO before an interrupt is generated. The Threshold feature prevents the Host from being interrupted each time the FIFO needs to load or unload one byte of data. The thresholds, therefore, allow the FIFO's operation to be adjusted to the speed of the Host, optimizing the overall interface performance.

#### NOTE:

DSC's should be allowed to be written into the output FIFO by the UPI-452 code only when the service request is law. The service request can be monitored by b7 of OTHR. This guideline will elimate the possibility of a DSC being written to the output FIFO with the intention of setting the service request while having the number of bytes in the output FIFO below the threshold. This condition can occur if the FIFO contains at least two bytes, the service request is being asserted, and the host reads from the output FIFO until one byte remains.

## **Immediate Commands**

The UPI-452 provides, in addition to data and DSCs, a third direct means of communication between the external Host and internal CPU called Immediate Commands. As the name implies, an Immediate Command is available to the receiving CPU immediately, via an interrupt, without being entered into the FIFO as are Data Stream Commands. Like Data Stream Commands, Immediate Commands are written either via a unique external address by the host CPU, or via dedicated SFR by the internal CPU.

The DSC and/or Immediate Command interface may be defined as either Interrupt or Polled under user program control via the Interrupt Enable (IE), Slave Control Register (SLCON), and Interrupt Enable Priority (IEP) Special Function Registers, for the internal CPU and via the Host Control SFR for the external Host CPU.

#### **DMA**

The UPI-452 contains a two channel internal DMA controller which allows transfer of data between any of the three writeable memory spaces: Internal Data Memory, External Load Expansion Bus Data Memory and the Special Function Register array. The Special Function Register array appears as a set of unique dedicated memory addresses which may be used as either the source or destination address of a DMA transfer. Each DMA channel is independently programmable via dedicated Special Function Registers for mode, source and destination addresses, and byte count to be transferred. Each DMA channel has four programmable modes:

- Alternate Cycle Mode

- Burst Mode

- FIFO or Serial Channel Demand Mode

- External Demand Mode

A complete description of each mode and DMA operation may be found in the section titled "General Purpose DMA Channels".

# FIFO/SLAVE INTERFACE FUNCTIONAL DESCRIPTION

## Overview

The FIFO is a 128 Byte RAM array with recirculating pointers to manage the read and write accesses. The FIFO consists of an Input and an Output channel. Access cycles to the FIFO by the internal CPU and external Host are interleaved and appear to be occurring concurrently to both the internal CPU and external Host. Interleaving access cycles ensures efficient use of this shared resource. The internal CPU accesses the FIFO in the same way it would access any of the Special Function Registers e.g., direct and register indirect addressing as well as arithmetric and logical instructions.

## **Input FIFO Channel**

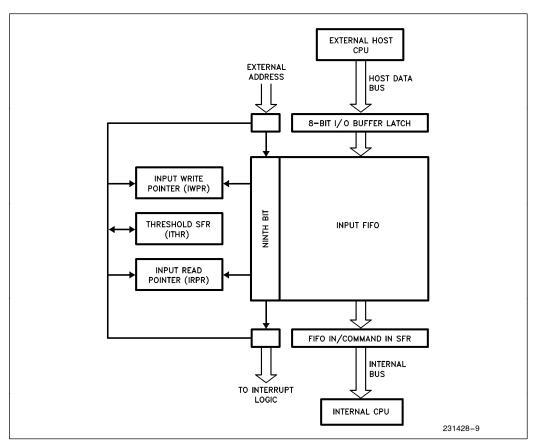

The Input FIFO Channel provides for data transfer from the external Host to the internal CPU (Figure 5). The registers associated with the Input Channel during normal operation are listed in Table 1\*.

Table 1. Input FIFO Channel Registers\*

|    | Register Name                | Description            |

|----|------------------------------|------------------------|

| 1) | Input Buffer Latch           | Host CPU Write only    |

| 2) | FIFO IN SFR                  | Internal CPU Read only |

| 3) | COMMAND IN SFR               | Internal CPU Read only |

| 4) | Input FIFO Read Pointer SFR  | Internal CPU Read only |

| 5) | Input FIFO Write Pointer SFR | Internal CPU Read only |

| 6) | Input FIFO Threshold SFR     | Internal CPU Read only |

<sup>\*</sup>See "FIFO-EXTERNAL HOST INTERFACE FIFO DMA FREEZE MODE" section for FIFO DMA Freeze Mode SFR characteristics description.

Figure 5. Input FIFO Channel Functional Block Diagram

The host CPU writes data and Data Stream Commands into the Input Buffer Latch on the rising edge of the external WR signal. External addressing determines whether the byte is a data byte or Data Stream Command and the FIFO logic sets the ninth bit of the FIFO accordingly as the byte is moved from the Input Buffer Latch into the FIFO. A "1" in the ninth bit indicates that the incoming byte is a Data Stream Command. The internal CPU reads data bytes via the FIFO IN SFR, and Data Stream Commands via the COMMAND IN SFR.

A Data Stream Command will generate an interrupt to the internal CPU prior to being read and after completion of the previous operation. The DSC can then be read via the COMMAND IN SFR. Data can only be read via the FIFO IN SFR and Data Stream Commands via the COMMAND IN SFR. Attempting to read Data Stream Commands as data by addressing the FIFO IN SFR will result in "0FFH" being read, and the Input FIFO Read Pointer will remain intact. (This prevents accidental misreading of Data Stream Commands.) Attempting to read data as Data Stream Commands will have the same consequence.

The Input FIFO Channel addressing is controlled by the Input FIFO Read and Write Pointer SFRs. These SFRs are read only registers during normal operation. However, during FIFO DMA Freeze Mode (See FIFO-External Host Interface FIFO DMA Freeze Mode description), the internal CPU has write access to them. Any write to these registers in normal mode will have no effect. The Input Write Pointer SFR contains the address location to which data/commands are written from the Input Buffer Latch. The write pointer is automatically incremented after each write and is reset to zero if equal to the CBP, as the Input FIFO operates as a circular buffer.

If a write is performed on an empty FIFO, the first byte is also written into the FIFO IN or COMMAND IN SFR. If the Host continues writing while the Input FIFO is full, an external interrupt, if enabled, is sent to the host to signal the overrun condition. The writes are ignored by the FIFO control logic. Similarly, an internal CPU read of an empty FIFO will cause an underrun error interrupt to be generated to the internal CPU and a value of "OFFH" will be read by the internal CPU.

The Read Pointer SFR holds the address of the next byte to be read from the Input FIFO. An Input FIFO read operation post-increments the Input Read Pointer SFR and loads a new data byte into the FIFO IN SFR or a Data Stream Command into the COMMAND IN SFR at the end of the read cycle.

An Input FIFO Request for Service (via DMA, Interrupt or a flag) is generated to the Host whenever more data can be written into the Input FIFO. For efficient utilization of the Host, a "threshold" value can be programmed into the Input FIFO Threshold SFR. The range of values of the Input FIFO Threshold SFR can be from 0 to (CBP-3). The Request for Service Interrupt is generated only after the Input FIFO has room to accommodate a threshold number of bytes or more. The threshold is equal to the total number of bytes assigned to the Input FIFO (CBP) minus the number of bytes programmed in the Input FIFO Threshold SFR. With this feature the Host is assured that it can write at least a threshold number of bytes to the Input FIFO channel without worrying about an overrun condition. Once the Request for Service is generated it remains active until the Input FIFO becomes full.

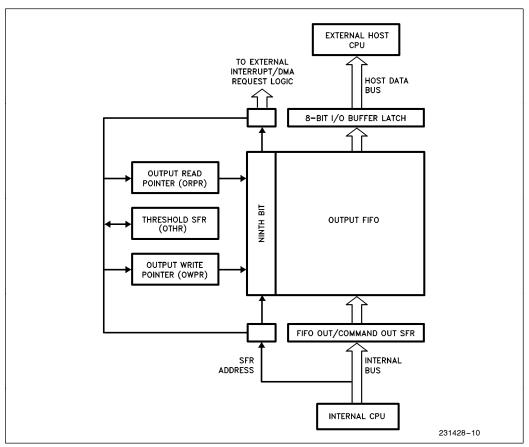

## **Output FIFO Channel**

The Output FIFO Channel provides data transfer from the UPI-452 internal CPU to the external Host (Figure 6).

The registers associated with the Output Channel during normal operation are listed in Table 2\*.

Figure 6. Output FIFO Channel Functional Block Diagram

**Table 2. Output FIFO Channel Registers**

|    | Register Name                 | Description                 |

|----|-------------------------------|-----------------------------|

| 1) | Output Buffer Latch           | Host CPU Read only          |

| 2) | FIFO OUT SFR                  | Internal CPU Read and Write |

| 3) | COMMAND OUT SFR               | Internal CPU Read and Write |

| 4) | Output FIFO Read Pointer SFR  | Internal CPU Read only      |

| 5) | Output FIFO Write Pointer SFR | Internal CPU Read only      |

| 6) | Output FIFO Threshold SFR     | Internal CPU Read only      |

<sup>\*</sup>See "FIFO-EXTERNAL HOST INTERFACE FIFO DMA FREEZE MODE" section for FIFO DMA Freeze Mode register characteristics description.

The UPI-452 internal CPU transfers data to the Output FIFO via the FIFO OUT SFR and commands via the COMMAND OUT SFR. If the byte is written to the COMMAND OUT SFR, the ninth bit is automatically set (=1) to indicate a Data Stream Command. If the byte is written to the FIFO OUT SFR the ninth bit is cleared (=0). Thus the FIFO OUT and COMMAND OUT SFRs are the same but the address determines whether the byte entered in the FIFO is a DSC or data byte.

The Output FIFO preloads a byte into the Output Buffer Latch. When the Host issues a RD/ signal, the data is immediately read from the Output Buffer Latch. The next data byte is then loaded into the Output Buffer Latch, a flag is set and an interrupt, if enabled, is generated if the byte is a DSC (ninth bit is set). The operation is carefully timed such that an interrupt can be generated in time for it to be recognized by the Host before its next read instruction. Internal CPU write and external Host read operations are interleaved at the FIFO so that they appear to be occurring concurrently.

The Output FIFO read and write pointer operation is the same as for the Input Channel. Writing to the FIFO OUT or COMMAND OUT SFRs will increment the Output Write Pointer SFR but reading from it will leave the write pointer unchanged. A rollover of the Output FIFO Write Pointer causes the pointer to be reset to the value in the Channel Boundary Pointer (CBP) SFR.

If the external host attempts to read a Data Stream Command as a data byte it will result in invalid data (0FFH) being read. The DSC is not lost because the invalid read does not increment the pointer. Similarly attempting to read a data byte as a Data Stream Command has the same result.

A Request for Service is generated to the external Host under the following two conditions:

1.) Whenever the internal CPU has written a threshold number of bytes or more into the Output FIFO (threshold = (OTHR) + 1). The threshold number should be chosen such that the bus latency time for the external Host does not result in a FIFO overrun error condition on the internal CPU side. The threshold limit should be large enough to make a bus request by the UPI-452 to the external host CPU worthwhile. Once a request for service is generated, the request remains active until the Output FIFO becomes empty. The range of values of the FIFO Output Threshold (OTHR) SFR is from 2 to {(80H-CBP)-1}. The threshold number can be programmed via the OTHR SFR.

2.) The second type of Request for Service is called "Flush Mode" and occurs when the internal CPU writes a Data Stream Command into the Output FIFO. Its purpose is to ensure that a data block entered into the Output FIFO, which is less than the programmed threshold, will generate a Request for Service interrupt, if enabled, and be read, or "Flushed" from the Output FIFO, by the external host CPU regardless of the status of the OTHR SER

#### NOTE:

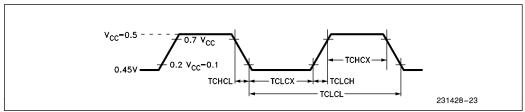

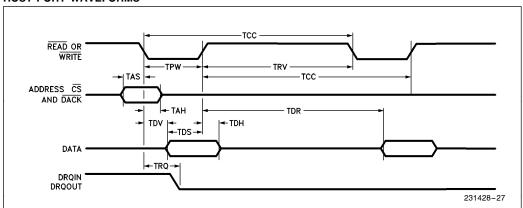

The host port read or write strobe (TPW) should be limited to a maximum of 4 TCLCL. This guideline will eliminate a potential output FIFO Request lock-up from occurring if the host reads the last byte from the output FIFO while the UPI-452 is beginning to write another byte to the output FIFO.

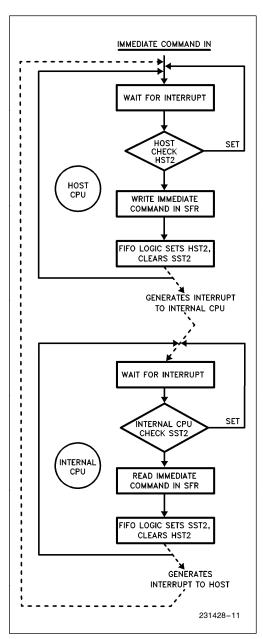

#### **Immediate Commands**

Immediate Commands provide direct communication between the external Host and UPI-452. Unlike Data Stream Commands which are entered into the FIFO, the Immediate Command is available to the receiving CPU directly, bypassing the FIFO. The Immediate Command can serve as a program vector pointing into a jump table in the recipients software. Immediate Command Interrupts are generated, if enabled, and a bit in the appropriate Status Register is set when an Immediate Command is input or output. A similar bit is provided to acknowledge when an Immediate Command has been read and whether the register is available to receive another command. The bits are reset when the Immediate Commands are read. Two Special Function Registers are dedicated to the Immediate Command interface. External addressing determines whether the Host is accessing the Input FIFO or the Immediate Command IN (IMIN) SFR. The internal CPU writes Immediate Commands to the Immediate Command OUT (IMOUT) SFR.

Both processors have the ability to enable or disable Immediate Command Interrupts. By disabling the interrupt, the recipient of the Immediate Command can poll the status SFR and read the Immediate Command at its convenience. Immediate Commands should only be written when the appropriate Immediate Command SFR is empty (as indicated in the appropriate status SFR:HSTAT/SSTAT). Similarly, the Immediate Command SFR should only be read when there is data in the Register.

The flowcharts in Figure 7a and 7b illustrate the proper handshake mechanisms between the external Host and internal CPU when handling Immediate Commands.

Figure 7a. Handshake Mechanisms for Handling Immediate Command IN Flowchart

Figure 7b. Handshake Mechanisms for Handling Immediate Command OUT Flowchart

## **HOST & SLAVE INTERFACE SPECIAL FUNCTION REGISTERS**

## **Slave Interface Special Function Registers**

The Internal CPU interfaces with the FIFO slave module via the following registers:

- 1) Mode Special Function Register (MODE)

- 2) Slave Control Special Function Register (SLCON)

- 3) Slave Status Special Function Register (SSTAT)

Each register resides in the SFR Array and is accessible via all direct addressing modes except bit. Only the Slave Control Register (SLCON) is bit addressable.

## 1) MODE Special Function Register (MODE)

The MODE SFR provides the primary control of the external host-FIFO interface. It is included in the SFR Array so that the internal CPU can configure the external host-FIFO interface should the user decide that the UPI-452 slave initialize itself independent of the external host CPU.

The MODE SFR can be directly modified by the internal CPU through direct address instructions. It can also be indirectly modified by the external host CPU by setting up a MODE SFR service routine in the UPI-452 program memory and having the host issue a Command, either Immediate or DSC, to vector to that routine.

| Symbolic<br>Address |                   |          |     |     |    |    |    |       | Physical<br>Address |

|---------------------|-------------------|----------|-----|-----|----|----|----|-------|---------------------|

| MODE                | _                 | MD6      | MD5 | MD4 | _  | _  | _  | _     | 0F9H                |

|                     | (MSB)<br>Status O | n Reset: |     |     |    |    |    | (LSB) |                     |

|                     | 1*                | 0        | 0   | 0   | 1* | 1* | 1* | 1*    |                     |

- MD7 (reserved)\*\*

- MD6 Request for Service to external CPU via;

- 1 = DMA (DRQIN/DRQOUT) request to external host when the Input or Output FIFO channel requests service

- 0 = Interrupt (INTRQIN/INTRQOUT or INTRQ) to external host when the Input or Output FIFO channel requests service or a DSC is encountered in the I/O Buffer Latch

- MD5 Configure DRQIN/INTRQIN and DRQOUT/INTRQOUT to be either;

- 1 = Enable (Actively driven)

- 0 = Disable (Tri-state)

- MD4 Configure INTRQ to be either;

- 1 = Enable (Actively driven)

- 0 = Disable (Tri-state)

- MD3 (reserved) \*\*

- MD2 (reserved) \*\*

- MD1 (reserved) \*\*

- MD0 (reserved) \*\*

## 2) Slave Control SFR (SLCON)

The Slave Control SFR is used to configure the FIFO-internal CPU interface. All interrupts are to the internal CPU.

| Symbolic<br>Address |                   |          |      |      |     |    |      |       | Physical<br>Address |

|---------------------|-------------------|----------|------|------|-----|----|------|-------|---------------------|

| SLCON               | IFI               | OFI      | ICII | ICOI | FRZ | _  | IFRS | OFRS  | 0E8H                |

|                     | (MSB)<br>Status O | n Reset: |      |      |     |    |      | (LSB) |                     |

|                     | 0                 | 0        | 0    | 0    | 0   | 1* | 0    | 0     |                     |

- IFI Enable Input FIFO Interrupt (due to Underrun Error Condition, Data Stream Command or Request Service)

- 1 = Enable

- 0 = Disable

- OFI Enable Output FIFO Interrupt (due to Overrun Error Condition or Request Service)

- 1 = Enable

- 0 = Disable

Note: If the DMA is configured to service a FIFO demand, then the Request for Service Interrupt is not generated.

- ICII Generate Interrupt when a command is written to the Immediate Command in Register

- 1 = Enable

- 0 = Disable

- ICOI Generate Interrupt when Immediate Command Out Register is Available

- 1 = Enable

- 0 = Disable

- FRZ Enable FIFO DMA Freeze Mode

- 1 = Normal operation

- 0 = FIFO DMA Freeze Mode

- SC2 (reserved) \*\*

- IFRS Input FIFO Channel Request for Service

- 1 = Request when Input FIFO not empty

- 0 = Request when Input FIFO full

- OFRS Output FIFO Channel Request for Service

- 1 = Request when Output FIFO not full

- 0 = Channel Request when Output FIFO empty

## NOTES:

## 3) Slave Status SFR (SSTAT)

The bits in the Slave Status SFR reflect the status of the FIFO-internal CPU interface. It can be read during an internal interrupt service routine to determine the nature of the interrupt or read during a polling sequence to determine a course of action.

| Symbolic<br>Address |                                         |      |      |      |                       |      |      |       | Physical<br>Address |

|---------------------|-----------------------------------------|------|------|------|-----------------------|------|------|-------|---------------------|

| SSTAT               | SST7                                    | SST6 | SST5 | SST4 | SST3                  | SST2 | SST1 | SST0  | 0E9H                |

|                     | ← Output FIFO Status → Status On Reset: |      |      |      | ← Input FIFO Status → |      |      |       |                     |

|                     | 1                                       | 0    | 0    | 0    | 1                     | 1    | 1    | 1     |                     |

|                     | (MSB)                                   |      |      |      |                       |      |      | (LSB) |                     |

<sup>\*</sup>A '1' will be read from all SFR reserved locations except HCON SFR, HC0 and HC2.

<sup>\*\*&#</sup>x27;reserved'—these locations are reserved for future use by Intel Corporation.

SST7 Output FIFO Overrun Error Condition

1 = No Error

0 = Error (latched until Slave Status SFR is read)

SST6 Immediate Command Out Register Status

1 = Full (i.e. Host CPU has not read previous Immediate Command Out sent by internal CPU)

0 = Available

SST5 FIFO DMA Freeze Mode Status

1 = Normal Operation

0 = FIFO DMA Freeze Mode in Progress

SST4 Output FIFO Request for Service Flag

1 = Output FIFO does not request service

0 = Output FIFO requests service

SST3 Input FIFO Underrun Error Condition Flag

1 = No Underrun Error

0 = Underrun Error (latched until Slave Status SFR is read)

SST2 Immediate Command In SFR Status

1 = Empty

0 = Immediate Command received from host CPU

SST1 Data Stream Command/Data at Input FIFO Flag

1 = Data (not DSC)

0 = DSC (at COMMAND IN SFR)

SST0 Input FIFO Request For Service Flag

1 = Input FIFO Does Not Request Service

0 = Input FIFO Request for Service

## **EXTERNAL HOST INTERFACE SPECIAL FUNCTION REGISTERS**

The external host CPU has direct access to the following SFRs:

1) Host Control Special Function Register

2) Host Status Special Function Register

It can also access other SFRs by commanding the internal CPU to change them accordingly via Data Stream Commands or Immediate Commands. The protocol for implementing this is entirely determined by the user.

## 1) Host Control SFR (HCON)

By writing to the Host Control SFR, the host can enable or disable FIFO interrupts and DMA requests and can reset the UPI-452.

| Symbolic<br>Address |                   |          |     |     |     |    |     |       | Physical<br>Address |

|---------------------|-------------------|----------|-----|-----|-----|----|-----|-------|---------------------|

| HCON                | HC7               | HC6      | HC5 | HC4 | HC3 | _  | HC1 | _     | 0E7H                |

|                     | (MSB)<br>Status O | n Reset: |     |     |     |    |     | (LSB) |                     |

|                     | 0                 | 0        | 0   | 0   | 0   | 0* | 0   | 0*    |                     |

- Enable Output FIFO Interrupt due to Underrun Error Condition, Data Stream Command or Service Request

- 1 = Enable

- 0 = Disable

- HC6 Enable Input FIFO Interrupt due to Overrun Error Condition, or Service Request

- 1 = Enable

- 0 = Disable

- HC5 Enable the generation of the Interrupt due to Immediate Command Out being present

- 1 = Enable

- 0 = Disable

- HC4 Enable the Interrupt due to the Immediate Command In Register being Available for a new Immediate Command byte

- 1 = Enable

- 0 = Disable

- HC3 Reset UPI-452

- 1 = Software RESET

- 0 = Normal Operation

- HC2 (reserved) \*\*

- HC1 Select between INTRQ and INTRQIN/INTRQOUT as Request for Service interrupt signal when DMA is disabled

- 1 = INTRQ

- 0 = INTRQIN or INTRQOUT

- HC0 (reserved) \*\*

#### NOTES:

## 2) Host Status SFR (HSTAT)

The Host Status SFR provides information on the FIFO-Host Interface and can be used to determine the source of an external interrupt during polling. Like the Slave Status SFR, the Host Status SFR reflects the current status of the FIFO-external host interface.

| Symbolic<br>Address |                                         |      |      |      |                       |      |      |       | Physical<br>Address |

|---------------------|-----------------------------------------|------|------|------|-----------------------|------|------|-------|---------------------|

| HSTAT               | HST7                                    | HST6 | HST5 | HST4 | HST3                  | HST2 | HST1 | HST0  | 0E6H                |

|                     | ← Output FIFO Status → Status On Reset: |      |      |      | ← Input FIFO Status → |      |      |       |                     |

|                     | 1                                       | 1    | 1    | 1    | 1                     | 1/0* | 1    | 1     |                     |

|                     | (MSB)                                   |      |      |      |                       |      |      | (LSB) |                     |

<sup>\*</sup>A '1' will be read from all SFR reserved locations except HCON SFR, HC0 and HC2.

<sup>\*\*&#</sup>x27;reserved'—these locations are reserved for future use by Intel Corporation.

HST7 Output FIFO Underrun Error Condition

1 = No Underrun Error

0 = Underrun Error (latched until Host Status Register is read)

HST6 Immediate Command Out SFR Status

1 = Empty

0 = Immediate Command Present

HST5 Data Stream Command/Data at Output FIFO Status

1 = Data (not DSC)

0 = DSC (present at Output FIFO COM-MAND OUT SFR)

(Note: Only if HST4 = 0, if HST4 = 1 then undetermined)

HST4 Output FIFO Request for Service Status

1 = No Request for Service

0 = Output FIFO Request for Service due to:

a. Output FIFO containing the threshold number of bytes or more

b. Internal CPU sending a block of data terminated by a DSC (DSC Flush Mode)

HST3 Input FIFO Overrun Error Condition

1 = No Overrun Error

0 = Overrun Error (latched until Host Status Register is read)

HST2 Immediate Command In SFR Status

1 = Full (i.e. Internal CPU has not read pre-

vious Immediate Command sent by Host)

0 = Empty

\* Reset value;

'1' - if read by the external Host

'0' — if read by internal CPU (reads shadow latch - see FIFO DMA Freeze Mode description)

HST1 FIFO DMA Freeze Mode Status

1 = Freeze Mode in progress.

(In Freeze Mode, the bits of the Host Status SFR are forced to a '1' initially to prevent the external Host from attempting to access the FIFO. The definition of the Host Status SFR bits during FIFO DMA Freeze Mode can be found in FIFO DMA Freeze Mode description)

0 = Normal Operation

HST0 Input FIFO Request Service Status

1 = Input FIFO does not request service

0 = Input FIFO request service due to the Input FIFO containing enough space for the host to write the threshold number of bytes or more

# FIFO MODULE - EXTERNAL HOST INTERFACE

#### Overview

The FIFO-external Host interface supports high speed asynchronous bi-directional 8-bit data transfers. The host interface is fully compatible with Intel microprocessor local busses and with MULTIBUS. The FIFO has two specialized DMA request pins for Input and Output FIFO channel DMA requests. These are multiplexed to provide a dedicated Request for Service interrupt (DRQIN/INTRQIN, DRQOUT/INTRQOUT).

The external Host can program, under user defined protocol, thresholds into the FIFO Input and Output Threshold SFRs which determine when the FIFO Request for Service interrupt is generated to the Host CPU. The FIFO module external Host interface is configured by the internal CPU via the MODE SFR. "The external Host can enable and disable Host interface interrupts via the Host Control SFR." Data Stream Commands in the Input FIFO channel allow the Host to influence the processing of data blocks and are sent with the data flow to maintain synchronization. Data Stream Commands in the Output FIFO Channel allow the internal CPU to perform the same function, and also to set the Output FIFO Request Service status logic to the host CPU regardless of the programmed value in the Threshold SFR

### Slave Interface Address Decoding

The UPI-452 determines the desired Host function through address decoding. The lower three bits of the address as well as the READ, WRITE, Chip Select ( $\overline{CS}$ ) and DMA Acknowledge ( $\overline{DACK}$ ) are used for decoding. Table 3 shows the pin states and the Read or Write operations associated with each configuration.

### Interrupts to the Host

The UPI-452 interrupts the external Host via the INTRQ pin. In addition, the DRQIN and DRQOUT pins can be multiplexed as interrupt request lines, INTRQIN and INTRQOUT respectively, when DMA is disabled. This provides two special FIFO "Request for Service" interrupts.

There are eight FIFO-related interrupt sources; two from The Input FIFO; three from The Output FIFO; one from the Immediate Command Out SFR; one from the Immediate Command IN SFR; and one due to FIFO DMA Freeze Mode.

INPUT FIFO: The Input FIFO interrupt is generated whenever:

a. The Input FIFO contains space for a threshold number of bytes.

| Table 3. UPI-452 Address Deco | ding |

|-------------------------------|------|

|-------------------------------|------|

| DACK | CS | <b>A2</b> | <b>A</b> 1 | A0 | Read                                         | Write                                     |

|------|----|-----------|------------|----|----------------------------------------------|-------------------------------------------|

| 1    | 1  | Χ         | Χ          | Х  | No Operation                                 | No Operation                              |

| 1    | 0  | 0         | 0          | 0  | Data or DMA from Output FIFO Channel         | Data or DMA to Input FIFO Channel         |

| 1    | 0  | 0         | 0          | 1  | Data Stream Command from Output FIFO Channel | Data Stream Command to Input FIFO Channel |

| 1    | 0  | 0         | 1          | 0  | Host Status SFR Read                         | Reserved                                  |

| 1    | 0  | 0         | 1          | 1  | Host Control SFR Read                        | Host Control SFR Write                    |

| 1    | 0  | 1         | 0          | 0  | Immediate Command SFR Read                   | Immediate Command to SFR Write            |

| 1    | 0  | 1         | 1          | Х  | Reserved                                     | Reserved                                  |

| 0    | Х  | Х         | Х          | Х  | DMA Data from Output FIFO Channel            | DMA Data to Input FIFO Channel            |

| 1    | 0  | 1         | 0          | 1  | Reserved                                     | Reserved                                  |

#### NOTES:

- 1. Attempting to read a DSC as a data byte will result in invalid data being read. The read pointers are not incremented so that the DSC is not lost. Attempting to read a data byte as a DSC has the same result.

- 2. If  $\overline{DACK}$  is active the UPI-452 will attempt a DMA operation when  $\overline{RD}$  or  $\overline{WR}$  becomes active regardless of the DMA enable bit (MD6) in the MODE SFR. Care should be taken when using  $\overline{DACK}$ . For proper operation,  $\overline{DACK}$  must be driven high (+5V) when not using DMA.

- When an Input FIFO overrun error condition exists. The appropriate bits in the Host Status SFR are set and the interrupt is generated only if enabled

OUTPUT FIFO: The Output FIFO Request for Service Interrupt operates in a similar manner as the Input FIFO interrupt:

- a. When the FIFO contains the threshold number of bytes or more.

- Output FIFO error condition interrupts are generated when the Output FIFO is underrun.

- c. Data Stream Command present in the Output Buffer Latch.

A Data Stream Command interrupt is used to halt normal processing, using the command as a vector to a service routine. When DMA is disabled, the user may program (through HC1) INTRQ to include FIFO Request for Service Interrupts or use INTRQIN and INTRQOUT as Request for Service Interrupts.

### IMMEDIATE COMMAND INTERRUPTS:

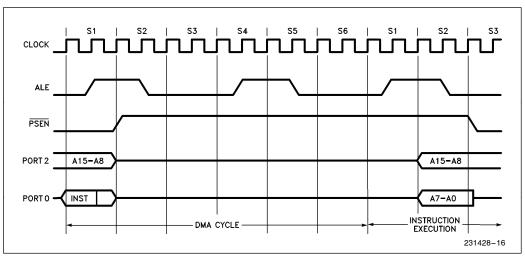

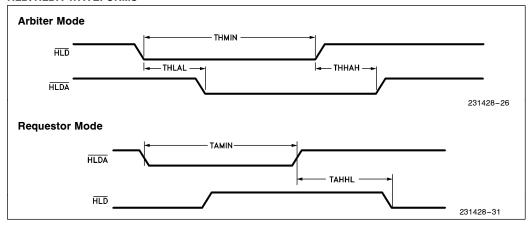

a. An Immediate Command Out Interrupt is generated, if enabled, to the Host and the corresponding Host Status SFR bit (HSTAT HST6) is cleared, when the internal CPU writes to the Immediate Command OUT (IMOUT) SFR. When the Host reads the Immediate Command OUT (IMOUT) SFR the corresponding bit in the Host Status (HSTAT) SFR is set. This causes the Slave Status Immediate Command OUT Status bit (SSTAT SST6) to be cleared indicating that the Immediate Command OUT (IMOUT) SFR is empty. If enabled, a FIFO-Slave Interface will also be generated to the internal CPU. (See Figure 7b, Immediate Command OUT Flowchart.)