# IA-32 Intel<sup>®</sup> Architecture Software Developer's Manual

Volume 1: Basic Architecture

**NOTE:** The IA-32 Intel Architecture Software Developer's Manual consists of five volumes: *Basic Architecture*, Order Number 253665; *Instruction Set Reference A-M*, Order Number 253666; *Instruction Set Reference N-Z*, Order Number 253667; *System Programming Guide*, *Part 1*, Order Number 253668; *System Programming Guide*, *Part 2*, Order Number 253669. Refer to all five volumes when evaluating your design needs.

Order Number: 253665-018 January 2006 INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EX-PRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RE-LATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FIT-NESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. INTEL PRODUCTS ARE NOT INTENDED FOR USE IN MEDICAL, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS.

Intel may make changes to specifications and product descriptions at any time, without notice.

Developers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Improper use of reserved or undefined features or instructions may cause unpredictable behavior or failure in developer's software code when running on an Intel processor. Intel reserves these features or instructions for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from their unauthorized use.

The Intel<sup>®</sup> IA-32 architecture processors (e.g., Pentium<sup>®</sup> 4 and Pentium III processors) may contain design defects or errors known as errata. Current characterized errata are available on request.

Hyper-Threading Technology requires a computer system with an Intel<sup>®</sup> Pentium<sup>®</sup> 4 processor supporting Hyper-Threading Technology and an HT Technology enabled chipset, BIOS and operating system. Performance will vary depending on the specific hardware and software you use. See <u>http://www.intel.com/techtrends/technologies/hyperthreading.htm</u> for more information including details on which processors support HT Technology.

Intel<sup>®</sup> Virtualization Technology requires a computer system with an enabled Intel<sup>®</sup> processor, BIOS, virtual machine monitor (VMM) and for some uses, certain platform software enabled for it. Functionality, performance or other benefits will\_vary depending on hardware and software configurations. Intel<sup>®</sup> Virtualization Technology-enabled BIOS and VMM applications are currently in development.

Intel<sup>®</sup> Extended Memory 64 Technology (Intel<sup>®</sup> EM64T) requires a computer system with a processor, chipset, BIOS, OS, device drivers and applications enabled for Intel EM64T. **Processor will not operate (including 32-bit operation) without an Intel EM64T-enabled BIOS.** Performance will vary depending on your hardware and software configurations. **Intel EM64T-enabled OS, BIOS, device drivers and applications may not be available.** Check with your vendor for more information.

Intel, Intel386, Intel486, Pentium, Intel Xeon, Intel NetBurst, Intel SpeedStep, MMX, Celeron, and Itanium are trademarks or registered trademarks of Intel Corporation and its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 5937 Denver, CO 80217-9808

or call 1-800-548-4725 or visit Intel's website at http://www.intel.com

Copyright © 1997-2006 Intel Corporation

# CONTENTS

#### PAGE

| СНАРТ    |                                                                        |        |

|----------|------------------------------------------------------------------------|--------|

| ABOUT    | THIS MANUAL                                                            |        |

| 1.1      | IA-32 PROCESSORS COVERED IN THIS MANUAL                                |        |

| 1.2      | OVERVIEW OF VOLUME 1: BASIC ARCHITECTURE                               |        |

| 1.3      | NOTATIONAL CONVENTIONS                                                 |        |

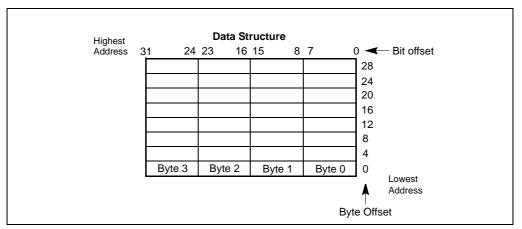

| 1.3.1    | Bit and Byte Order                                                     |        |

| 1.3.2    | Reserved Bits and Software Compatibility                               |        |

| 1.3.3    | Instruction Operands                                                   | 1-5    |

| 1.3.4    | Hexadecimal and Binary Numbers                                         |        |

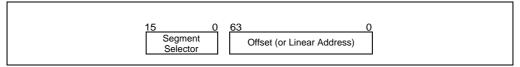

| 1.3.5    | Segmented Addressing                                                   | 1-5    |

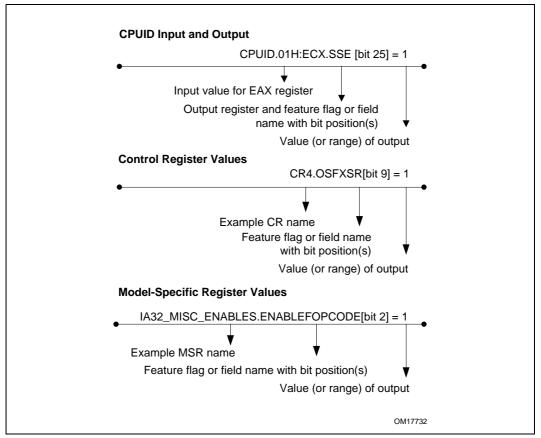

| 1.3.6    | A New Syntax for CPUID, CR, and MSR Values                             | 1-6    |

| 1.3.7    | Exceptions                                                             | 1-7    |

| 1.4      | RELATED LITERATURE                                                     | . 1-8  |

| СНАРТ    | ER 2                                                                   |        |

| IA-32 IN |                                                                        |        |

| 2.1      | BRIEF HISTORY OF THE IA-32 ARCHITECTURE                                | . 2-1  |

| 2.1.1    | 16-bit Processors and Segmentation (1978)                              | 2-1    |

| 2.1.2    | The Intel <sup>®</sup> 286 Processor (1982)                            | 2-2    |

| 2.1.3    | The Intel386™ Processor (1985)                                         | 2-2    |

| 2.1.4    | The Intel486 <sup>™</sup> Processor (1989)                             | 2-2    |

| 2.1.5    | The Intel <sup>®</sup> Pentium <sup>®</sup> Processor (1993)           | 2-3    |

| 2.1.6    | The P6 Family of Processors (1995-1999)                                | 2-3    |

| 2.1.7    | The Intel Pentium 4 Processor Family (2000-Current)                    | 2-4    |

| 2.1.8    | The Intel <sup>®</sup> Xeon <sup>®</sup> Processor (2001-Current)      | 2-4    |

| 2.1.9    | The Intel <sup>®</sup> Pentium <sup>®</sup> M Processor (2003-Current) | 2-5    |

| 2.1.10   | The Intel Pentium Processor Extreme Edition (2005-Current)             | 2-5    |

| 2.2      | MORE ON SPECIFIC ADVANCES                                              |        |

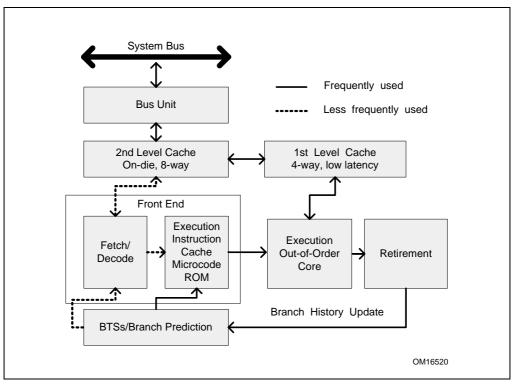

| 2.2.1    | P6 Family Microarchitecture                                            | 2-6    |

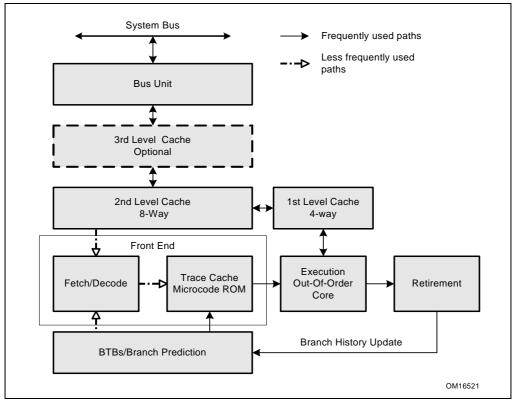

| 2.2.2    | Intel NetBurst <sup>®</sup> Microarchitecture                          | 2-7    |

| 2.2.2.1  | The Front End Pipeline                                                 | 2-9    |

| 2.2.2.2  | Out-Of-Order Execution Core                                            | 2-10   |

| 2.2.2.3  | Retirement Unit.                                                       | 2-10   |

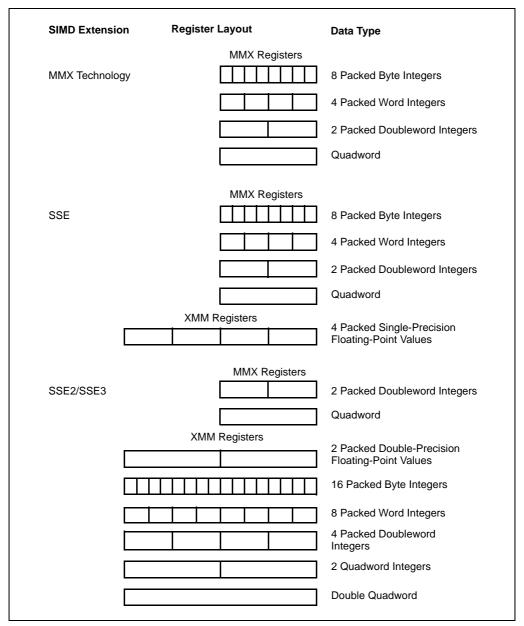

| 2.2.3    | SIMD Instructions                                                      | 2-11   |

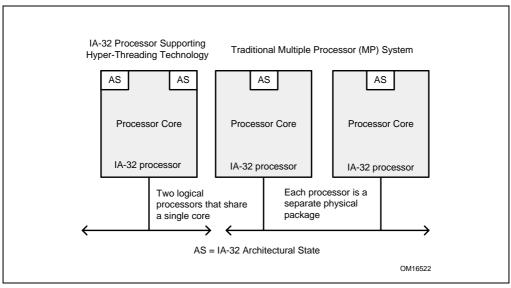

| 2.2.4    | Hyper-Threading Technology                                             | 2-13   |

| 2.2.4.1  | Some Implementation Notes                                              | 2-14   |

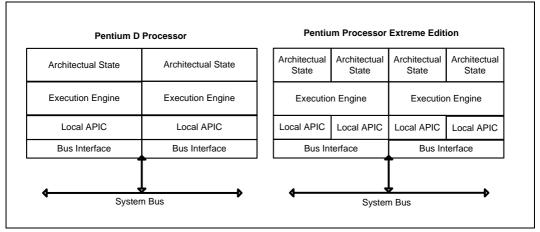

| 2.2.5    | Dual-Core Technology                                                   | 2-15   |

| 2.2.6    | Intel <sup>®</sup> Extended Memory 64 Technology                       | 2-15   |

| 2.2.7    | Intel <sup>®</sup> Virtualization Technology                           |        |

| 2.3      | IA-32 PROCESSOR GENERATIONS                                            | . 2-16 |

| СНАРТ    | ER 3                                                                   |        |

| BASIC    | EXECUTION ENVIRONMENT                                                  |        |

| ~ .      |                                                                        | ~ 4    |

|       | MODES OF OPERATION                          |     |

|-------|---------------------------------------------|-----|

| 3.1.1 | IA-32e Mode                                 | 3-2 |

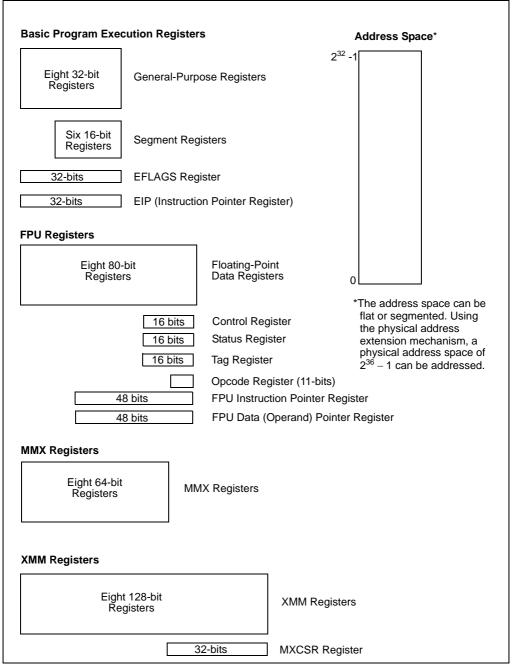

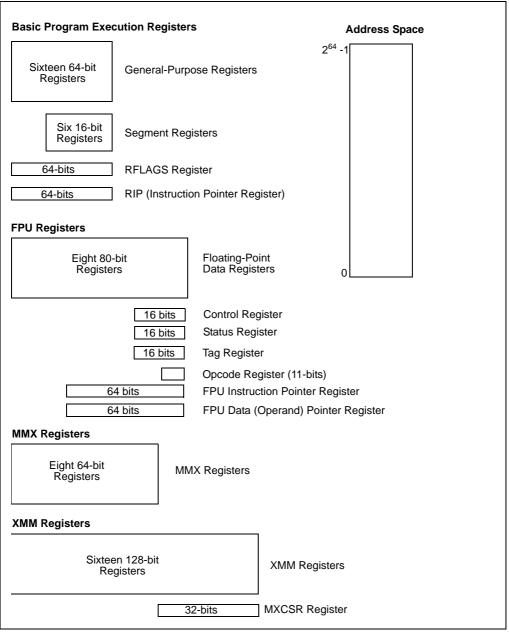

| 3.2   | OVERVIEW OF THE BASIC EXECUTION ENVIRONMENT | 3-3 |

| 3.2.1 | 64-Bit Mode Execution Environment           | 3-6 |

| 3.3   | MEMORY ORGANIZATION.                        | 3-8 |

#### PAGE

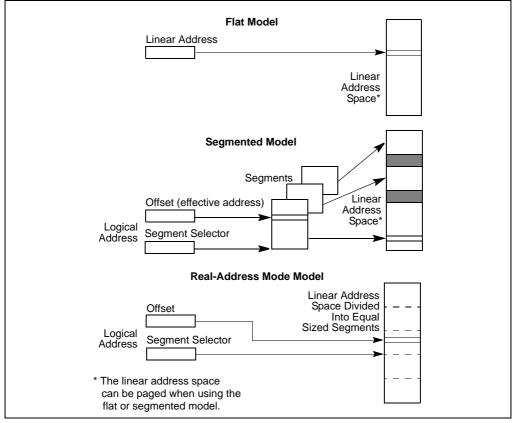

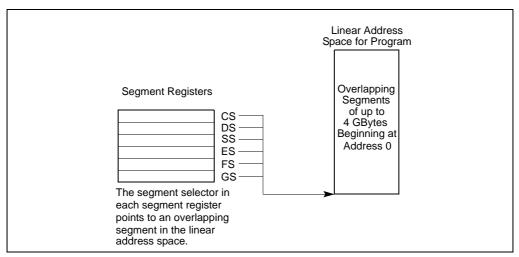

| 3.3.1   | Three Memory Models                            | 3-8 |

|---------|------------------------------------------------|-----|

| 3.3.2   | Paging and Virtual Memory                      | 3-9 |

| 3.3.3   | Memory Organization in 64-Bit Mode             |     |

| 3.3.4   | Modes of Operation vs. Memory Model            | -10 |

| 3.3.5   | 32-Bit and 16-Bit Address and Operand Sizes    | -11 |

| 3.3.6   | Extended Physical Addressing in Protected Mode |     |

| 3.3.7   | Address Calculations in 64-Bit Mode            | -12 |

| 3.3.7.1 | Canonical Addressing                           | -12 |

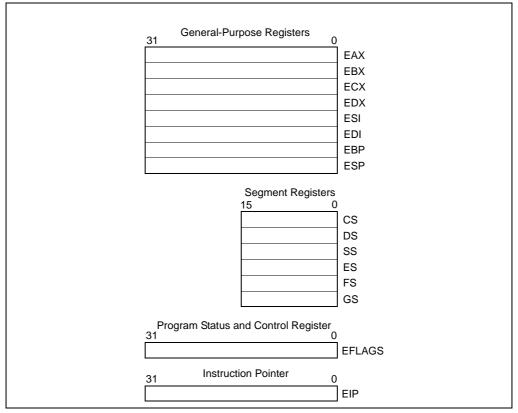

| 3.4     | BASIC PROGRAM EXECUTION REGISTERS              | -13 |

| 3.4.1   | General-Purpose Registers                      |     |

| 3.4.1.1 | General-Purpose Registers in 64-Bit Mode       | -15 |

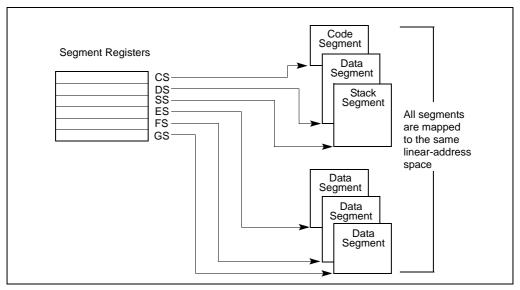

| 3.4.2   | Segment Registers                              |     |

| 3.4.2.1 | Segment Registers in 64-Bit Mode               | -19 |

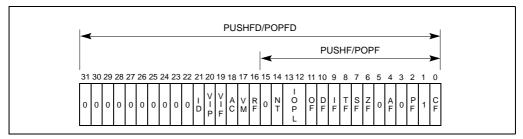

| 3.4.3   | EFLAGS Register                                | -20 |

| 3.4.3.1 | Status Flags                                   |     |

| 3.4.3.2 | DF Flag                                        | -22 |

| 3.4.3.3 | System Flags and IOPL Field                    |     |

| 3.4.3.4 | RFLAGS Register in 64-Bit Mode                 |     |

| 3.5     | INSTRUCTION POINTER                            |     |

| 3.5.1   | Instruction Pointer in 64-Bit Mode             |     |

| 3.6     | OPERAND-SIZE AND ADDRESS-SIZE ATTRIBUTES 3     |     |

| 3.6.1   | Operand Size and Address Size in 64-Bit Mode   |     |

| 3.7     | OPERAND ADDRESSING 3                           |     |

| 3.7.1   | Immediate Operands                             |     |

| 3.7.2   | Register Operands                              | -27 |

| 3.7.2.1 | Register Operands in 64-Bit Mode               |     |

| 3.7.3   | Memory Operands                                |     |

| 3.7.3.1 | Memory Operands in 64-Bit Mode                 |     |

| 3.7.4   | Specifying a Segment Selector                  |     |

| 3.7.4.1 | Segmentation in 64-Bit Mode                    |     |

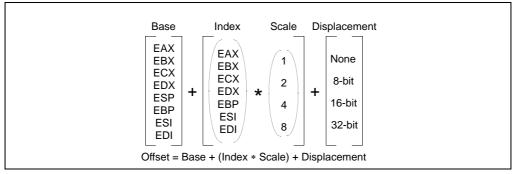

| 3.7.5   | Specifying an Offset                           | -30 |

| 3.7.5.1 | Specifying an Offset in 64-Bit Mode            |     |

| 3.7.6   | Assembler and Compiler Addressing Modes        |     |

| 3.7.7   | I/O Port Addressing                            | -33 |

|         |                                                |     |

## CHAPTER 4

#### DATA TYPES

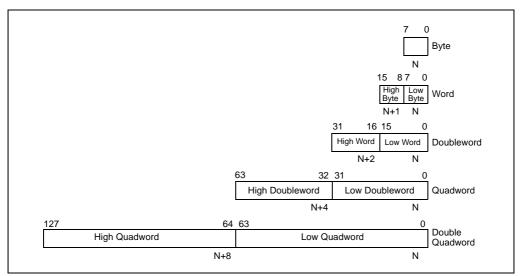

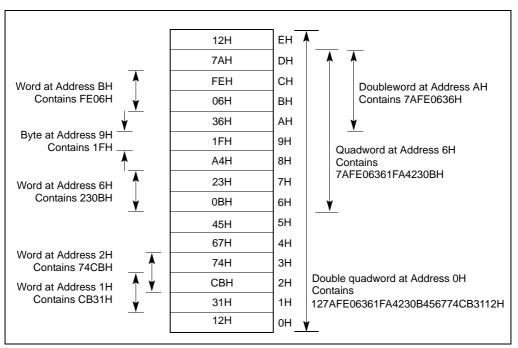

| 4.1     | FUNDAMENTAL DATA TYPES                                            | -1 |

|---------|-------------------------------------------------------------------|----|

| 4.1.1   | Alignment of Words, Doublewords, Quadwords, and Double Quadwords4 | -2 |

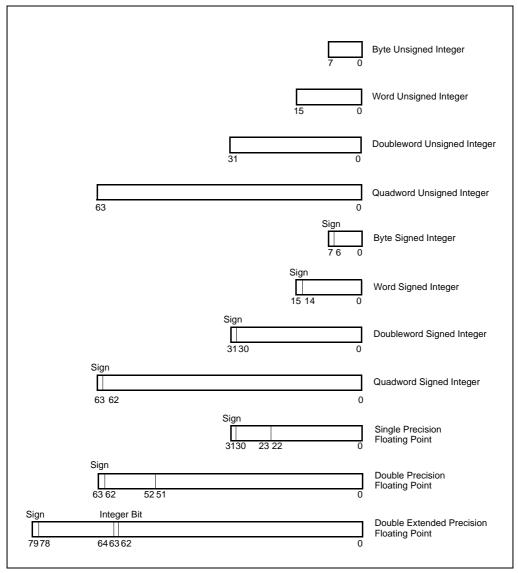

| 4.2     | NUMĚRIC DATA TYPĖS 4                                              | -3 |

| 4.2.1   | Integers                                                          | -4 |

| 4.2.1.1 | Unsigned Integers                                                 |    |

| 4.2.1.2 | Signed Integers                                                   | -4 |

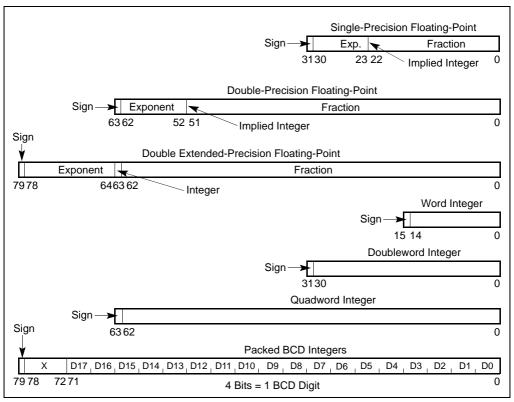

| 4.2.2   | Floating-Point Data Types4                                        | -5 |

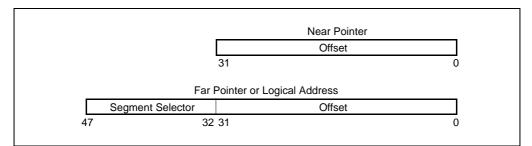

| 4.3     | POINTER DATA TYPES 4                                              | -7 |

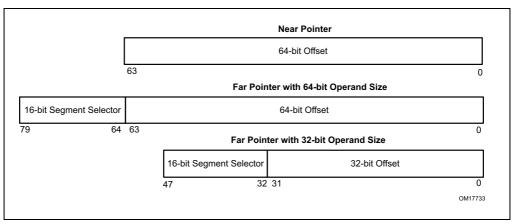

| 4.3.1   | Pointer Data Types in 64-Bit Mode4                                | -7 |

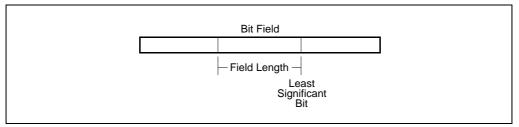

| 4.4     | BIT FIELD DATA TYPE 4                                             | -8 |

| 4.5     | STRING DATA TYPES 4                                               |    |

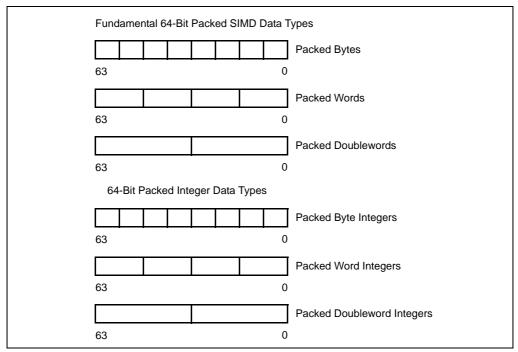

| 4.6     | PACKED SIMD DATA TYPES 4                                          | -8 |

| 4.6.1   | 64-Bit SIMD Packed Data Types                                     | -9 |

| 4.6.2   | 128-Bit Packed SIMD Data Types4                                   | -9 |

| 4.7     | BCD AND PACKED BCD INTEGERS 4-                                    | 11 |

#### PAGE

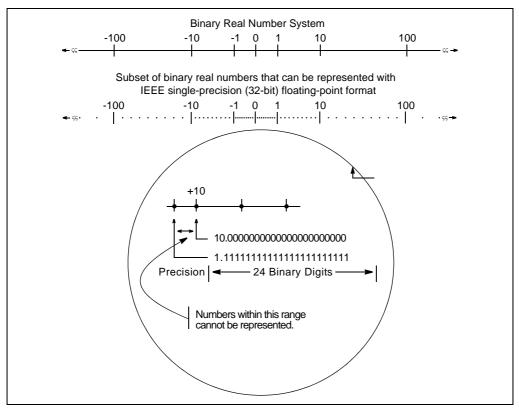

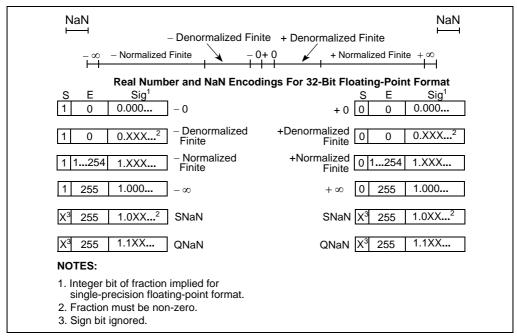

| 4.8     | REAL NUMBERS AND FLOATING-POINT FORMATS 4-12              |

|---------|-----------------------------------------------------------|

| 4.8.1   | Real Number System 4-13                                   |

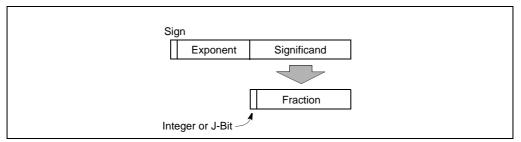

| 4.8.2   | Floating-Point Format 4-13                                |

| 4.8.2.1 | Normalized Numbers 4-15                                   |

| 4.8.2.2 | Biased Exponent 4-15                                      |

| 4.8.3   | Real Number and Non-number Encodings 4-15                 |

| 4.8.3.1 | Signed Zeros                                              |

| 4.8.3.2 | Normalized and Denormalized Finite Numbers                |

| 4.8.3.3 | Signed Infinities 4-18                                    |

| 4.8.3.4 | NaNs                                                      |

| 4.8.3.5 | Operating on SNaNs and QNaNs 4-19                         |

| 4.8.3.6 | Using SNaNs and QNaNs in Applications 4-20                |

| 4.8.3.7 | QNaN Floating-Point Indefinite 4-20                       |

| 4.8.4   | Rounding                                                  |

| 4.8.4.1 | Rounding Control (RC) Fields 4-22                         |

| 4.8.4.2 | Truncation with SSE and SSE2 Conversion Instructions 4-22 |

| 4.9     | OVERVIEW OF FLOATING-POINT EXCEPTIONS 4-22                |

| 4.9.1   | Floating-Point Exception Conditions 4-24                  |

| 4.9.1.1 | Invalid Operation Exception (#I) 4-24                     |

| 4.9.1.2 | Denormal Operand Exception (#D) 4-24                      |

| 4.9.1.3 | Divide-By-Zero Exception (#Z) 4-25                        |

| 4.9.1.4 | Numeric Overflow Exception (#O) 4-25                      |

| 4.9.1.5 | Numeric Underflow Exception (#U) 4-26                     |

| 4.9.1.6 | Inexact-Result (Precision) Exception (#P) 4-27            |

| 4.9.2   | Floating-Point Exception Priority 4-28                    |

| 4.9.3   | Typical Actions of a Floating-Point Exception Handler     |

#### **CHAPTER 5**

#### INSTRUCTION SET SUMMARY

| 5.1    | GENERAL-PURPOSE INSTRUCTIONS                       | -2 |

|--------|----------------------------------------------------|----|

| 5.1.1  | Data Transfer Instructions 5                       | -2 |

| 5.1.2  | Binary Arithmetic Instructions 5                   | -3 |

| 5.1.3  | Decimal Arithmetic Instructions 5                  | -4 |

| 5.1.4  | Logical Instructions                               | -4 |

| 5.1.5  | Shift and Rotate Instructions 5                    | -5 |

| 5.1.6  | Bit and Byte Instructions 5                        | -5 |

| 5.1.7  | Control Transfer Instructions 5                    | -6 |

| 5.1.8  | String Instructions                                | -7 |

| 5.1.9  | I/O Instructions                                   |    |

| 5.1.10 | Enter and Leave Instructions 5                     | -8 |

| 5.1.11 | Flag Control (EFLAG) Instructions                  | -8 |

| 5.1.12 | Segment Register Instructions 5                    |    |

| 5.1.13 | Miscellaneous Instructions 5                       |    |

| 5.2    | X87 FPU INSTRUCTIONS                               | -9 |

| 5.2.1  | x87 FPU Data Transfer Instructions 5-1             | 10 |

| 5.2.2  | x87 FPU Basic Arithmetic Instructions              | 10 |

| 5.2.3  | x87 FPU Comparison Instructions 5-1                | 11 |

| 5.2.4  | x87 FPU Transcendental Instructions 5-1            |    |

| 5.2.5  | x87 FPU Load Constants Instructions                | 12 |

| 5.2.6  | x87 FPU Control Instructions 5-1                   | 13 |

| 5.3    | X87 FPU AND SIMD STATE MANAGEMENT INSTRUCTIONS 5-1 | 13 |

| 5.4    | MMX™ INSTRUCTIONS                                  | 14 |

|        |                                                    |    |

#### PAGE

| 5.4.1            | MMX Data Transfer Instructions                                            |       |

|------------------|---------------------------------------------------------------------------|-------|

| 5.4.2            | MMX Conversion Instructions                                               |       |

| 5.4.3            | MMX Packed Arithmetic Instructions.                                       |       |

| 5.4.4            | MMX Comparison Instructions                                               | .5-15 |

| 5.4.5            | MMX Logical Instructions                                                  |       |

| 5.4.6            | MMX Shift and Rotate Instructions                                         | .5-16 |

| 5.4.7            | MMX State Management Instructions                                         |       |

| 5.5              | SSE INSTRUCTIONS                                                          | 5-17  |

| 5.5.1            | SSE SIMD Single-Precision Floating-Point Instructions                     |       |

| 5.5.1.1          | SSE Data Transfer Instructions                                            |       |

| 5.5.1.2          | SSE Packed Arithmetic Instructions                                        | .5-18 |

| 5.5.1.3          | SSE Comparison Instructions                                               | .5-19 |

| 5.5.1.4          | SSE Logical Instructions                                                  | .5-19 |

| 5.5.1.5          | SSE Shuffle and Unpack Instructions                                       |       |

| 5.5.1.6          | SSE Conversion Instructions                                               | .5-19 |

| 5.5.2            | SSE MXCSR State Management Instructions.                                  | .5-20 |

| 5.5.3            | SSE 64-Bit SIMD Integer Instructions                                      |       |

| 5.5.4            | SSE Cacheability Control, Prefetch, and Instruction Ordering Instructions | .5-21 |

| 5.6              | SSE2 INSTRUCTIONS                                                         | 5-21  |

| 5.6.1            | SSE2 Packed and Scalar Double-Precision Floating-Point Instructions       | .5-22 |

| 5.6.1.1          | SSE2 Data Movement Instructions.                                          | .5-22 |

| 5.6.1.2          | SSE2 Packed Arithmetic Instructions                                       | .5-22 |

| 5.6.1.3          | SSE2 Logical Instructions.                                                |       |

| 5.6.1.4          | SSE2 Compare Instructions                                                 | .5-23 |

| 5.6.1.5          | SSE2 Shuffle and Unpack Instructions                                      | .5-23 |

| 5.6.1.6          | SSE2 Conversion Instructions                                              | .5-24 |

| 5.6.2            | SSE2 Packed Single-Precision Floating-Point Instructions                  | .5-25 |

| 5.6.3            | SSE2 128-Bit SIMD Integer Instructions                                    |       |

| 5.6.4            | SSE2 Cacheability Control and Ordering Instructions.                      | .5-26 |

| 5.7              | SSE3 INSTRUCTIONS                                                         | 5-26  |

| 5.7.1            | SSE3 x87-FP Integer Conversion Instruction                                | .5-27 |

| 5.7.2            | SSE3 Specialized 128-bit Unaligned Data Load Instruction                  | .5-27 |

| 5.7.3            | SSE3 SIMD Floating-Point Packed ADD/SUB Instructions                      |       |

| 5.7.4            | SSE3 SIMD Floating-Point Horizontal ADD/SUB Instructions.                 |       |

| 5.7.5            | SSE3 SIMD Floating-Point LOAD/MOVE/DUPLICATE Instructions                 | .5-28 |

| 5.7.6            | SSE3 Agent Synchronization Instructions                                   | .5-28 |

| 5.8              | SYSTEM INSTRUCTIONS.                                                      |       |

| 5.9              | 64-BIT MODE INSTRUCTIONS.                                                 |       |

| 5.10             | VIRTUAL-MACHINE EXTENSIONS                                                |       |

| 0.10             |                                                                           | 0.00  |

| СНАРТІ           | ED 6                                                                      |       |

|                  | DURE CALLS, INTERRUPTS, AND EXCEPTIONS                                    |       |

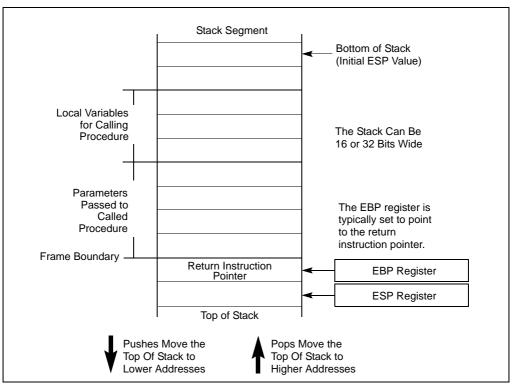

| 6.1              | PROCEDURE CALL TYPES                                                      | 6-1   |

| 6.2              |                                                                           |       |

| 6.2.1            | STACKSSetting Up a Stack                                                  |       |

| 6.2.1            | Stack Alignment.                                                          |       |

| 6.2.2            | Address-Size Attributes for Stack Accesses                                |       |

| 6.2.3            | Procedure Linking Information.                                            | 0-3   |

| 6.2.4<br>6.2.4.1 | Stack-Frame Base Pointer                                                  |       |

| -                |                                                                           |       |

| 6.2.4.2          | Return Instruction Pointer                                                |       |

| 6.2.5            | Stack Behavior in 64-Bit Mode                                             |       |

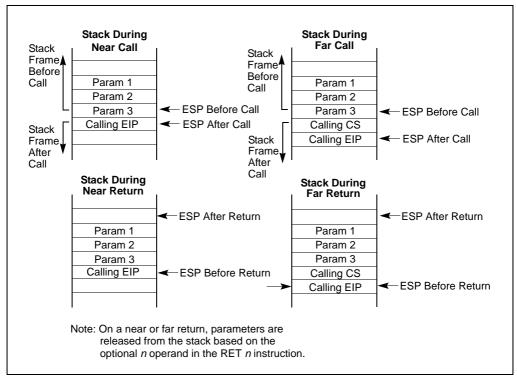

| 6.3              | CALLING PROCEDURES USING CALL AND RET                                     | . 0-5 |

#### PAGE

| 6.3.1<br>6.3.2<br>6.3.3 | Near CALL and RET Operation       6-5         Far CALL and RET Operation       6-5         Parameter Passing       6-7 |

|-------------------------|------------------------------------------------------------------------------------------------------------------------|

| 6.3.3.1                 | Passing Parameters Through the General-Purpose Registers                                                               |

| 6.3.3.2                 | Passing Parameters on the Stack 6-7                                                                                    |

| 6.3.3.3                 | Passing Parameters in an Argument List 6-7                                                                             |

| 6.3.4                   | Saving Procedure State Information                                                                                     |

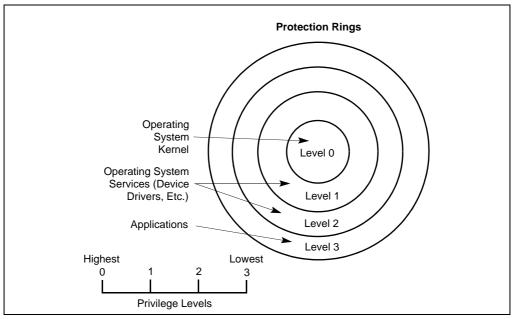

| 6.3.5                   | Calls to Other Privilege Levels 6-8                                                                                    |

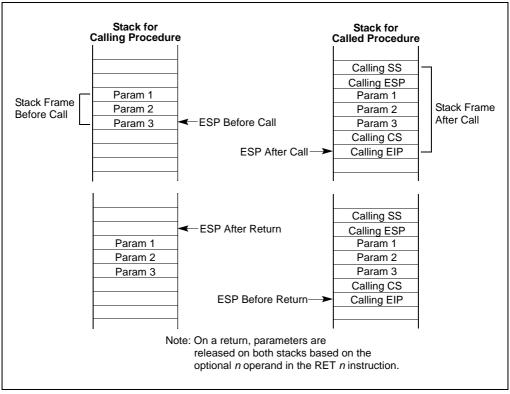

| 6.3.6                   | CALL and RET Operation Between Privilege Levels                                                                        |

| 6.3.7                   | Branch Functions in 64-Bit Mode 6-11                                                                                   |

| 6.4                     | INTERRUPTS AND EXCEPTIONS 6-12                                                                                         |

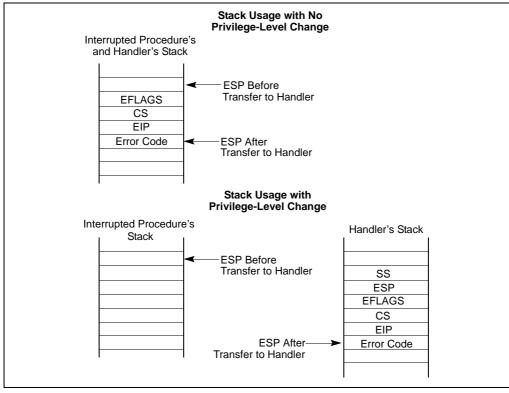

| 6.4.1                   | Call and Return Operation for Interrupt or Exception Handling Procedures 6-13                                          |

| 6.4.2                   | Calls to Interrupt or Exception Handler Tasks 6-17                                                                     |

| 6.4.3                   | Interrupt and Exception Handling in Real-Address Mode                                                                  |

| 6.4.4                   | INT n, INTO, INT 3, and BOUND Instructions                                                                             |

| 6.4.5                   | Handling Floating-Point Exceptions                                                                                     |

| 6.4.6                   | Interrupt and Exception Behavior in 64-Bit Mode                                                                        |

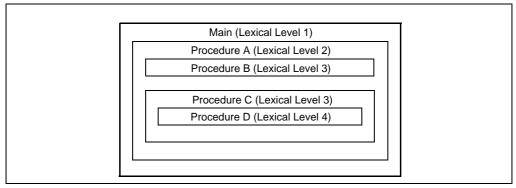

| 6.5                     | PROCEDURE CALLS FOR BLOCK-STRUCTURED LANGUAGES 6-19                                                                    |

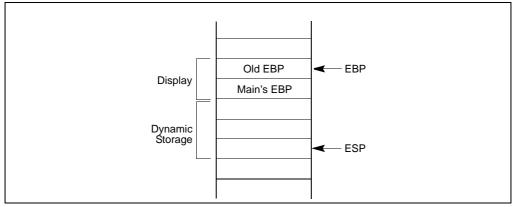

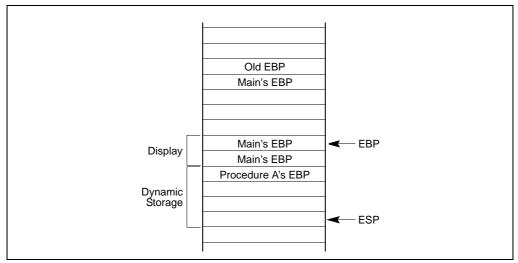

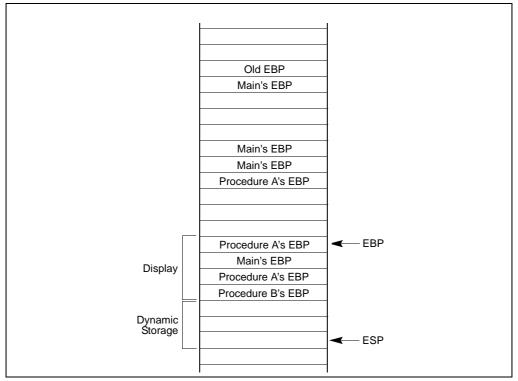

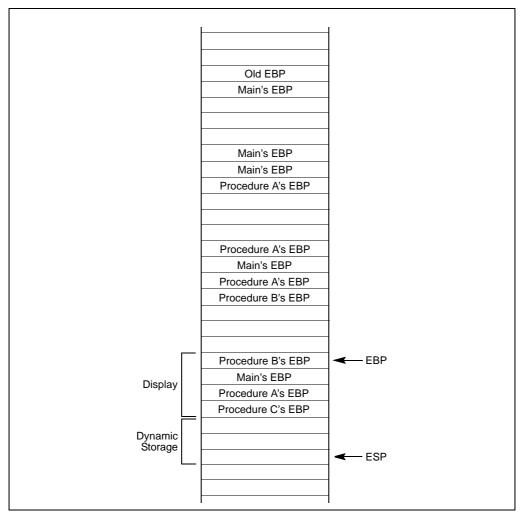

| 6.5.1                   | ENTER Instruction 6-19                                                                                                 |

| 6.5.2                   | LEAVE Instruction 6-26                                                                                                 |

#### CHAPTER 7

#### PROGRAMMING WITH GENERAL-PURPOSE INSTRUCTIONS

| 7.1     | PROGRAMMING ENVIRONMENT FOR GP INSTRUCTIONS                    |

|---------|----------------------------------------------------------------|

| 7.2     | PROGRAMMING ENVIRONMENT FOR GP INSTRUCTIONS IN 64-BIT MODE 7-2 |

| 7.3     | SUMMARY OF GP INSTRUCTIONS                                     |

| 7.3.1.  | Data Transfer Instructions                                     |

| 7.3.1.1 | General Data Movement Instructions                             |

| 7.3.1.2 | Exchange Instructions                                          |

| 7.3.1.3 | Exchange Instructions in 64-Bit Mode 7-7                       |

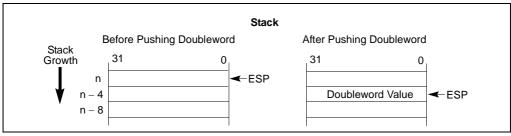

| 7.3.1.4 | Stack Manipulation Instructions 7-7                            |

| 7.3.1.5 | Stack Manipulation Instructions in 64-Bit Mode                 |

| 7.3.1.6 | Type Conversion Instructions                                   |

| 7.3.1.7 | Type Conversion Instructions in 64-Bit Mode                    |

| 7.3.2.  | Binary Arithmetic Instructions 7-10                            |

| 7.3.2.1 | Addition and Subtraction Instructions                          |

| 7.3.2.2 | Increment and Decrement Instructions                           |

| 7.3.2.3 | Increment and Decrement Instructions in 64-Bit Mode            |

| 7.3.2.4 | Comparison and Sign Change Instruction                         |

| 7.3.2.5 | Multiplication and Divide Instructions 7-11                    |

| 7.3.3.  | Decimal Arithmetic Instructions 7-12                           |

| 7.3.3.1 | Packed BCD Adjustment Instructions                             |

| 7.3.3.2 | Unpacked BCD Adjustment Instructions                           |

| 7.3.4.  | Decimal Arithmetic Instructions in 64-Bit Mode 7-13            |

| 7.3.5.  | Logical Instructions                                           |

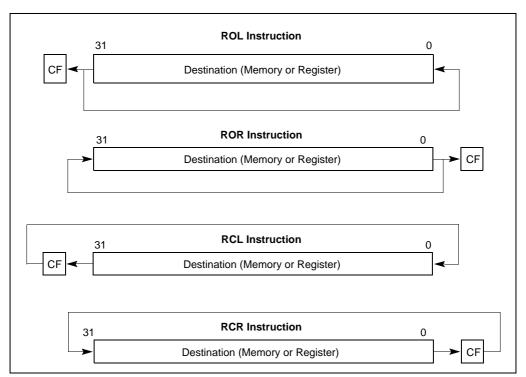

| 7.3.6.  | Shift and Rotate Instructions 7-14                             |

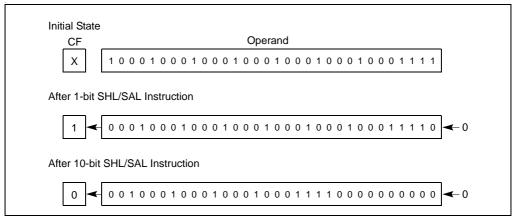

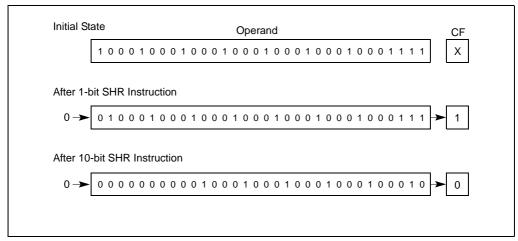

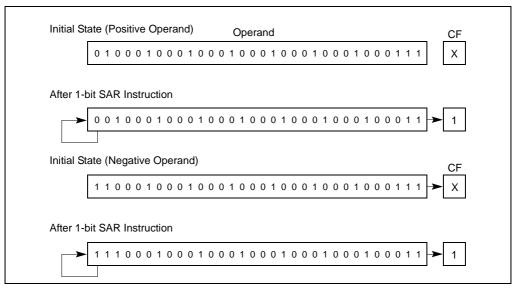

| 7.3.6.1 | Shift Instructions                                             |

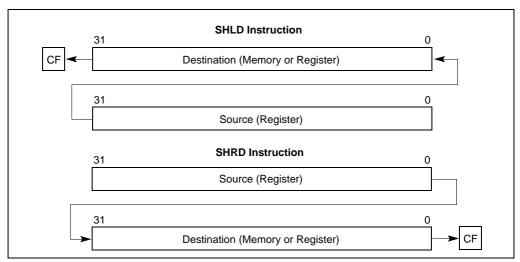

| 7.3.6.2 | Double-Shift Instructions                                      |

| 7.3.6.3 | Rotate Instructions                                            |

| 7.3.7.  | Bit and Byte Instructions 7-19                                 |

| 7.3.7.1 | Bit Test and Modify Instructions 7-19                          |

| 7.3.7.2 | Bit Scan Instructions                                          |

#### PAGE

| Byte Set on Condition Instructions                                    | 7-19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Test Instruction                                                      | 7-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Control Transfer Instructions                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Unconditional Transfer Instructions                                   | 7-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Conditional Transfer Instructions                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Control Transfer Instructions in 64-Bit Mode                          | 7-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Software Interrupt Instructions                                       | 7-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Software Interrupt Instructions in 64-bit Mode and Compatibility Mode | 7-25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| String Operations.                                                    | 7-25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Repeating String Operations                                           | 7-26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| String Operations in 64-Bit Mode                                      | 7-27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Repeating String Operations in 64-bit Mode.                           | 7-27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| I/O Instructions                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| I/O Instructions in 64-Bit Mode                                       | 7-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Enter and Leave Instructions                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Flag Control (EFLAG) Instructions                                     | 7-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Carry and Direction Flag Instructions                                 | 7-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| EFLAGS Transfer Instructions                                          | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Segment-Register Load and Store Instructions                          | 7-30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Far Control Transfer Instructions                                     | 7-30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Software Interrupt Instructions                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Address Computation Instruction                                       | 7-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Table Lookup Instructions                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Processor Identification Instruction                                  | 7-32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| No-Operation and Undefined Instructions                               | 7-32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                       | Test Instruction .<br>Control Transfer Instructions .<br>Unconditional Transfer Instructions .<br>Conditional Transfer Instructions .<br>Control Transfer Instructions in 64-Bit Mode .<br>Software Interrupt Instructions in 64-bit Mode and Compatibility Mode .<br>Software Interrupt Instructions in 64-bit Mode and Compatibility Mode .<br>String Operations .<br>Repeating String Operations .<br>String Operations in 64-Bit Mode .<br>Repeating String Operations in 64-bit Mode .<br>I/O Instructions in 64-Bit Mode .<br>Enter and Leave Instructions .<br>Flag Control (EFLAG) Instructions .<br>EFLAGS Transfer Instructions .<br>Interrupt Flag Instructions .<br>Flag Control (RFLAG) Instructions in 64-Bit Mode .<br>Segment Register Instructions .<br>Flag Control (RFLAG) Instructions .<br>Interrupt Flag Instructions .<br>Segment-Register Load and Store Instructions .<br>Software Interrupt Instructions .<br>Load Far Pointer Instructions .<br>Miscellaneous Instructions .<br>Processor Identification Instruction .<br>Processor Identification Instruction . |

#### **CHAPTER 8**

#### **PROGRAMMING WITH THE X87 FPU**

| 8.1     | X87 FPU EXECUTION ENVIRONMENT                      |

|---------|----------------------------------------------------|

| 8.1.1   | x87 FPU in 64-Bit Mode and Compatibility Mode8-2   |

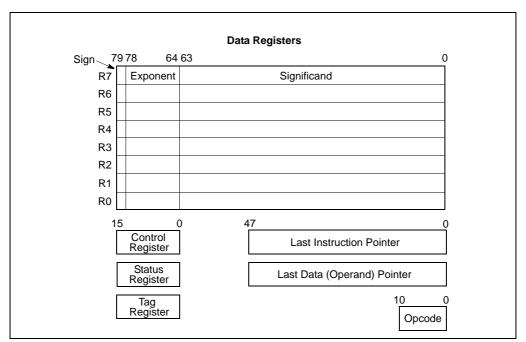

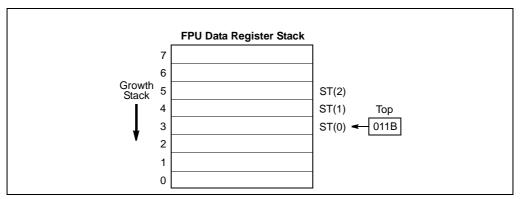

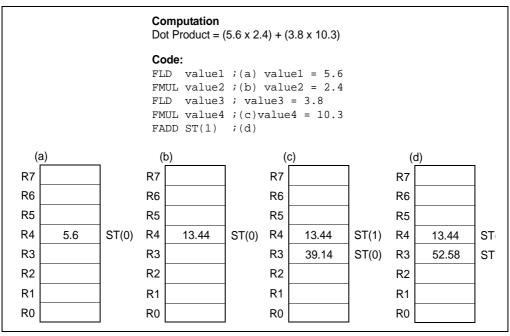

| 8.1.2   | x87 FPU Data Registers                             |

| 8.1.2.1 | Parameter Passing With the x87 FPU Register Stack  |

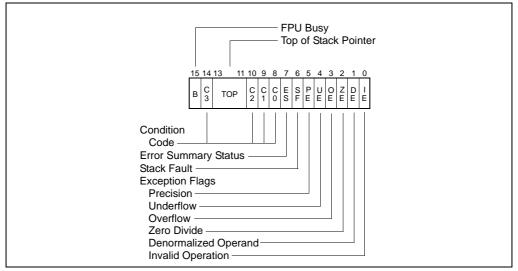

| 8.1.3   | x87 FPU Status Register8-6                         |

| 8.1.3.1 | Top of Stack (TOP) Pointer8-6                      |

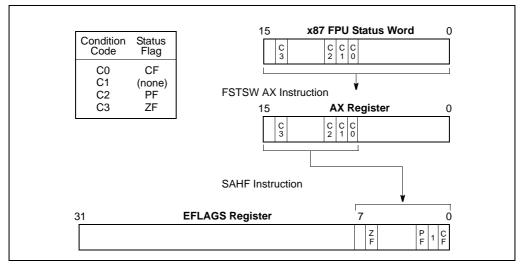

| 8.1.3.2 | Condition Code Flags                               |

| 8.1.3.3 | x87 FPU Floating-Point Exception Flags             |

| 8.1.3.4 | Stack Fault Flag                                   |

| 8.1.4   | Branching and Conditional Moves on Condition Codes |

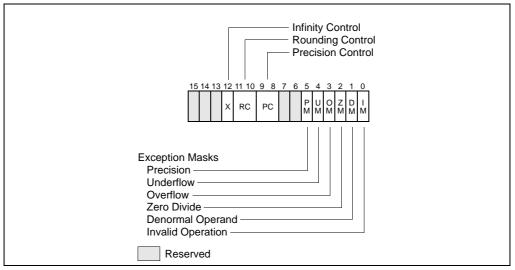

| 8.1.5   | x87 FPU Control Word8-10                           |

| 8.1.5.1 | x87 FPU Floating-Point Exception Mask Bits         |

| 8.1.5.2 | Precision Control Field                            |

| 8.1.5.3 | Rounding Control Field8-11                         |

| 8.1.6   | Infinity Control Flag                              |

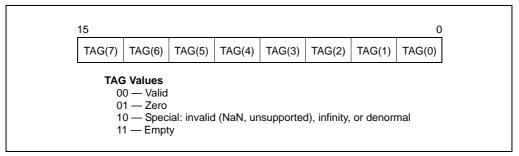

| 8.1.7   | x87 FPU Tag Word                                   |

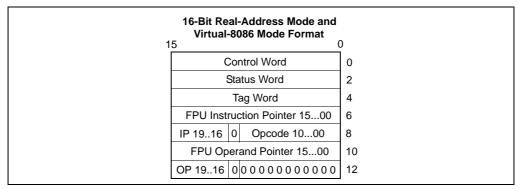

| 8.1.8   | x87 FPU Instruction and Data (Operand) Pointers    |

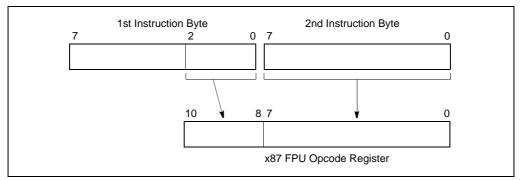

| 8.1.9   | Last Instruction Opcode                            |

| 8.1.9.1 | Fopcode Compatibility Sub-mode                     |

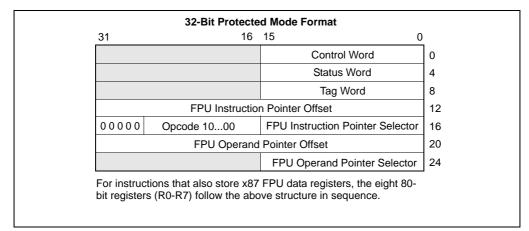

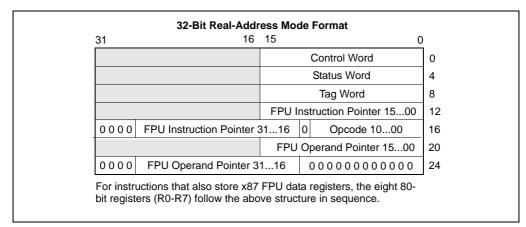

| 8.1.10  | Saving the x87 FPU's State with FSTENV/FNSTENV and FSAVE/FNSAVE | 8-14 |

|---------|-----------------------------------------------------------------|------|

| 8.1.11  | Saving the x87 FPU's State with FXSAVE                          | 8-16 |

| 8.2     | X87 FPU DATA TYPES                                              |      |

| 8.2.1   | Indefinites                                                     | 8-18 |

| 8.2.2   | Unsupported Double Extended-Precision                           |      |

|         | Floating-Point Encodings and Pseudo-Denormals                   | 8-18 |

| 8.3     | X86 FPU INSTRUCTION SET                                         |      |

| 8.3.1   | Escape (ESC) Instructions                                       |      |

| 8.3.2   | x87 FPU Instruction Operands                                    |      |

| 8.3.3   | Data Transfer Instructions                                      |      |

| 8.3.4   | Load Constant Instructions                                      | 8-22 |

| 8.3.5   | Basic Arithmetic Instructions                                   |      |

| 8.3.6   | Comparison and Classification Instructions                      |      |

| 8.3.6.1 | Branching on the x87 FPU Condition Codes                        |      |

| 8.3.7   | Trigonometric Instructions                                      | 8-27 |

| 8.3.8   | Pi                                                              |      |

| 8.3.9   | Logarithmic, Exponential, and Scale                             |      |

| 8.3.10  | Transcendental Instruction Accuracy.                            | 8-29 |

| 8.3.11  | x87 FPU Control Instructions                                    |      |

| 8.3.12  | Waiting vs. Non-waiting Instructions                            | 8-31 |

| 8.3.13  | Unsupported x87 FPU Instructions                                |      |

| 8.4     | X87 FPU FLOATING-POINT EXCEPTION HANDLING.                      | 8-31 |

| 8.4.1   | Arithmetic vs. Non-arithmetic Instructions                      |      |

| 8.5     | X87 FPU FLOATING-POINT EXCEPTION CONDITIONS.                    | 8-34 |

| 8.5.1   | Invalid Operation Exception                                     |      |

| 8.5.1.1 | Stack Overflow or Underflow Exception (#IS)                     |      |

| 8.5.1.2 | Invalid Arithmetic Operand Exception (#IA)                      | 8-35 |

| 8.5.2   | Denormal Operand Exception (#D)                                 | 8-37 |

| 8.5.3   | Divide-By-Zero Exception (#Z)                                   | 8-37 |

| 8.5.4   | Numeric Overflow Exception (#O)                                 | 8-38 |

| 8.5.5   | Numeric Underflow Exception (#U)                                |      |

| 8.5.6   | Inexact-Result (Precision) Exception (#P)                       |      |

| 8.6     | X87 FPU EXCEPTION SYNCHRONIZATION                               |      |

| 8.7     | HANDLING X87 FPU EXCEPTIONS IN SOFTWARE                         | 8-42 |

| 8.7.1   | Native Mode                                                     |      |

| 8.7.2   | MS-DOS* Compatibility Sub-mode                                  | 8-43 |

| 8.7.3   | Handling x87 FPU Exceptions in Software                         | 8-44 |

|         |                                                                 |      |

# CHAPTER 9 PROGRAMMING WITH INTEL<sup>®</sup> MMX<sup>™</sup> TECHNOLOGY

| 9.1   | OVERVIEW OF MMX TECHNOLOGY                               | 9-1 |

|-------|----------------------------------------------------------|-----|

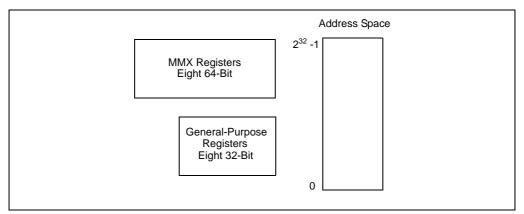

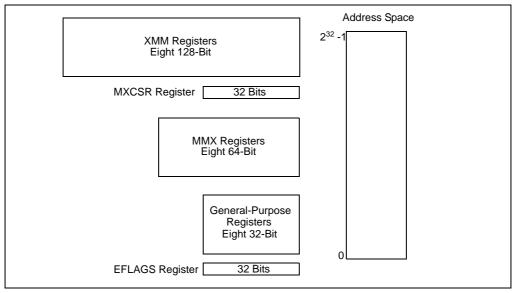

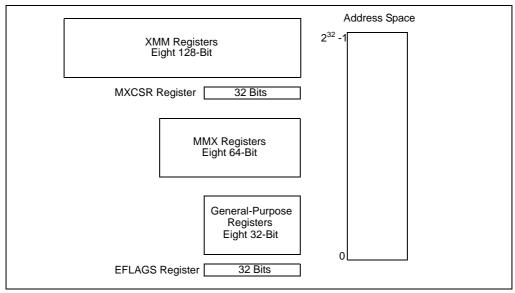

| 9.2   | THE MMX TECHNOLOGY PROGRAMMING ENVIRONMENT               | 9-2 |

| 9.2.1 | MMX Technology in 64-Bit Mode and Compatibility Mode     | 9-2 |

| 9.2.2 | MMX Registers                                            | 9-3 |

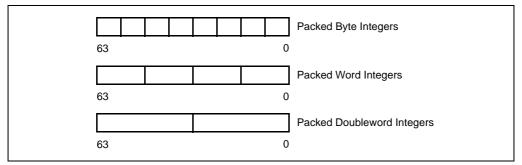

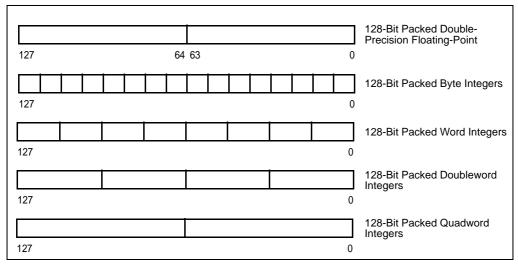

| 9.2.3 | MMX Data Types                                           | 9-4 |

| 9.2.4 | Memory Data Formats                                      | 9-4 |

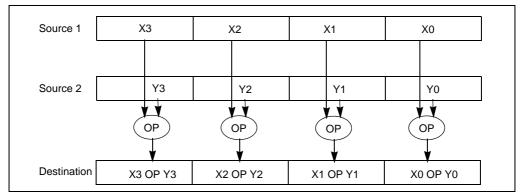

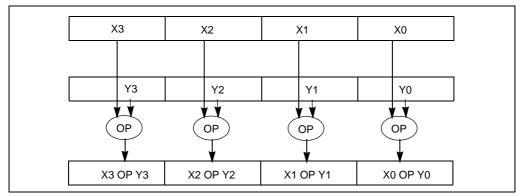

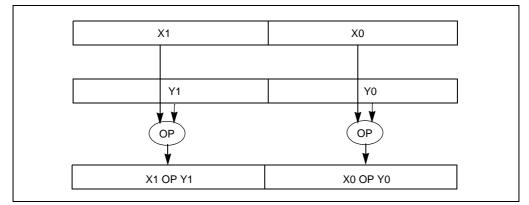

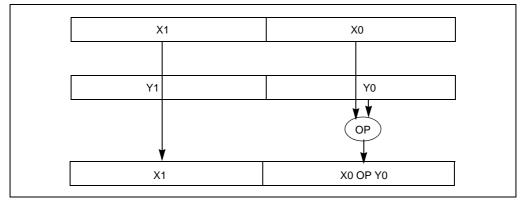

| 9.2.5 | Single Instruction, Multiple Data (SIMD) Execution Model | 9-4 |

| 9.3   | SATURATION AND WRAPAROUND MODES                          | 9-5 |

| 9.4   | MMX INSTRUCTIONS                                         | 9-6 |

| 9.4.1 | Data Transfer Instructions                               |     |

| 9.4.2 | Arithmetic Instructions                                  | 9-8 |

| 9.4.3 | Comparison Instructions                                  | 9-8 |

#### PAGE

| 9.4.4 | Conversion Instructions                                       |

|-------|---------------------------------------------------------------|

| 9.4.5 | Unpack Instructions                                           |

| 9.4.6 | Logical Instructions                                          |

| 9.4.7 | Shift Instructions                                            |

| 9.4.8 | EMMS Instruction                                              |

| 9.5   | COMPATIBILITY WITH X87 FPU ARCHITECTURE                       |

| 9.5.1 | MMX Instructions and the x87 FPU Tag Word                     |

| 9.6   | WRITING APPLICATIONS WITH MMX CODE                            |

| 9.6.1 | Checking for MMX Technology Support9-10                       |

| 9.6.2 | Transitions Between x87 FPU and MMX Code9-11                  |

| 9.6.3 | Using the EMMS Instruction9-12                                |

| 9.6.4 | Mixing MMX and x87 FPU Instructions                           |

| 9.6.5 | Interfacing with MMX Code9-13                                 |

| 9.6.6 | Using MMX Code in a Multitasking Operating System Environment |

| 9.6.7 | Exception Handling in MMX Code                                |

| 9.6.8 | Register Mapping                                              |

| 9.6.9 | Effect of Instruction Prefixes on MMX Instructions            |

|       |                                                               |

#### **CHAPTER 10**

#### PROGRAMMING WITH STREAMING SIMD EXTENSIONS (SSE)

| 10.1     | OVERVIEW OF SSE EXTENSIONS                                           | 10-1    |

|----------|----------------------------------------------------------------------|---------|

| 10.2     | SSE PROGRAMMING ENVIRONMENT                                          |         |

| 10.2.1   | SSE in 64-Bit Mode and Compatibility Mode.                           |         |

| 10.2.2   | XMM Registers                                                        |         |

| 10.2.3   | MXCSR Control and Status Register                                    | 10-5    |

| 10.2.3.1 | SIMD Floating-Point Mask and Flag Bits                               |         |

| 10.2.3.2 | SIMD Floating-Point Rounding Control Field                           |         |

| 10.2.3.3 | Flush-To-Zero.                                                       |         |

| 10.2.3.4 | Denormals-Are-Zeros                                                  |         |

| 10.2.4   | Compatibility of SSE Extensions with SSE2/SSE3/MMX and the x87 FPU . |         |

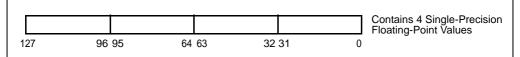

| 10.3     | SSE DATA TYPES                                                       |         |

| 10.4     | SSE INSTRUCTION SET.                                                 |         |

| 10.4.1   | SSE Packed and Scalar Floating-Point Instructions                    |         |

| 10.4.1.1 | SSE Data Movement Instructions.                                      |         |

| 10.4.1.2 | SSE Arithmetic Instructions                                          |         |

| 10.4.2   | SSE Logical Instructions                                             |         |

| 10.4.2.1 | SSE Comparison Instructions.                                         | 10-13   |

| 10.4.2.2 | SSE Shuffle and Unpack Instructions.                                 |         |

| 10.4.3   | SSE Conversion Instructions                                          |         |

| 10.4.4   | SSE 64-Bit SIMD Integer Instructions                                 | 10-16   |

| 10.4.5   | MXCSR State Management Instructions.                                 |         |

| 10.4.6   | Cacheability Control, Prefetch, and Memory Ordering Instructions.    |         |

| 10.4.6.1 | Cacheability Control Instructions                                    |         |

| 10.4.6.2 | Caching of Temporal vs. Non-Temporal Data                            | 10-18   |

| 10.4.6.3 | PREFETCHh Instructions                                               |         |

| 10.4.6.4 | SFENCE Instruction                                                   | 10-19   |

| 10.5     | FXSAVE AND FXRSTOR INSTRUCTIONS                                      | . 10-20 |

| 10.6     | HANDLING SSE INSTRUCTION EXCEPTIONS.                                 |         |

| 10.7     | WRITING APPLICATIONS WITH THE SSE EXTENSIONS                         | . 10-20 |

| CHAPTE   |                                                                        |        |

|----------|------------------------------------------------------------------------|--------|

|          | AMMING WITH STREAMING SIMD EXTENSIONS 2 (SSE2)                         |        |

| 11.1     | OVERVIEW OF SSE2 EXTENSIONS                                            | . 11-1 |

| 11.2     | SSE2 PROGRAMMING ENVIRONMENT                                           |        |

| 11.2.1   | SSE2 in 64-Bit Mode and Compatibility Mode.                            | . 11-4 |

| 11.2.2   | Compatibility of SSE2 Extensions with SSE, MMX                         |        |

|          | Technology and x87 FPU Programming Environment.                        | . 11-4 |

| 11.2.3   | Denormals-Are-Zeros Flag                                               |        |

| 11.3     | SSE2 DATA TYPES                                                        |        |

| 11.4     | SSE2 INSTRUCTIONS                                                      | . 11-6 |

| 11.4.1   | Packed and Scalar Double-Precision Floating-Point Instructions         |        |

| 11.4.1.1 | Data Movement Instructions                                             |        |

| 11.4.1.2 | SSE2 Arithmetic Instructions                                           |        |

| 11.4.1.3 | SSE2 Logical Instructions                                              | . 11-9 |

| 11.4.1.4 | SSE2 Comparison Instructions                                           | 11-10  |

| 11.4.1.5 | SSE2 Shuffle and Unpack Instructions                                   |        |

| 11.4.1.6 | SSE2 Conversion Instructions                                           |        |

| 11.4.2   | SSE2 64-Bit and 128-Bit SIMD Integer Instructions                      |        |

| 11.4.3   | 128-Bit SIMD Integer Instruction Extensions                            | 11-16  |

| 11.4.4   | Cacheability Control and Memory Ordering Instructions                  |        |

| 11.4.4.1 | FLUSH Cache Line                                                       | 11-16  |

| 11.4.4.2 | Cacheability Control Instructions                                      | 11-17  |

| 11.4.4.3 | Memory Ordering Instructions.                                          | 11-17  |

| 11.4.4.4 | Pause                                                                  | 11-17  |

| 11.4.5   | Branch Hints                                                           | 11-18  |

| 11.5     | SSE, SSE2, AND SSE3 EXCEPTIONS                                         |        |

| 11.5.1   | SIMD Floating-Point Exceptions                                         | 11-18  |

| 11.5.2   | SIMD Floating-Point Exception Conditions                               |        |

| 11.5.2.1 | Invalid Operation Exception (#I)                                       | 11-19  |

| 11.5.2.2 | Denormal-Operand Exception (#D)                                        | 11-21  |

| 11.5.2.3 | Divide-By-Zero Exception (#Z)                                          | 11-21  |

| 11.5.2.4 | Numeric Overflow Exception (#O)                                        |        |

| 11.5.2.5 | Numeric Underflow Exception (#U)                                       | 11-22  |

| 11.5.2.6 | Inexact-Result (Precision) Exception (#P)                              | 11-22  |

| 11.5.3   | Generating SIMD Floating-Point Exceptions                              |        |

| 11.5.3.1 | Handling Masked Exceptions                                             |        |

| 11.5.3.2 | Handling Unmasked Exceptions                                           | 11-24  |

| 11.5.3.3 | Handling Combinations of Masked and Unmasked Exceptions                | 11-25  |

| 11.5.4   | Handling SIMD Floating-Point Exceptions in Software                    | 11-25  |

| 11.5.5   | Interaction of SIMD and x87 FPU Floating-Point Exceptions              |        |