# 82389 Message Passing Coprocessor A Multibus II Bus Interface Controller

### Datasheet

### **Product Features**

- Highly Integrated VLSI Device

- Single-Chip Interface for the Parallel System Bus (IEEE 1296)

- —Interrupt Handling/Bus Arbitration Functions

- Dual-Buffer Input and Output DMA Capabilities

- —Nine 32-Byte High Speed FIF09

- Multiple Interface Support

- —Complete Protocol Support of the PSB Bus (Message Passing)

- —Processor Independent Interface (8-, 16-, or 32-bit CPU)

- Low-Cost 8-bit Microcontroller Interface

- —Dual-Port Memory Interface

- High Performance Coprocessing Functions

- —Off-loads CPU for Communication and Bus Interfacing

- —40 Mbytes/s Burst Transfer Speed

- Optimized for Real-time Response (Maximum 900 ns for 32-Byte Interrupt Packet)

- CMOS Technology

- 149-pin PGA Package (15 x 15 Grid)

The MPC 82389 is a highly integrated VLSI device that maximizes the performance of a Multibus II based multiprocessor system. It integrates the functions of bus arbitration, data transmit packetizing, error handling and interrupt control. Because of these integrated functions, the boat CPU can be off-loaded to utilize the maximum bus performance and subsequently increase the system throughput. The MPC 82389 also supports geographic addressing by providing access to the local interconnect registers for reference and control.

The MPC 82389 is designed to interface with an 8-, 16-, or 32-bit processor. The Parallel System Bus (PSB) performance is not affected by the CPU bus width or bandwidth. The data on the PSB is burst transferred at the maximum bus speed of 40 Mbytes/second regardless of CPU bus performance. Such performance is possible due to decoupling of the CPU from the PSB.

Order Number: 290145-005 January 2001

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel<sup>®</sup> products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel<sup>®</sup> products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The 82389 message passing coprocessor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2001

\*Other names and brands may be claimed as the property of others.

| 1.0 | MPC        | 82389 Introduction                       | 5  |

|-----|------------|------------------------------------------|----|

|     | 1.1        | Functional Overview                      | 6  |

|     |            | 1.1.1 MPC 82389 Interfaces               |    |

|     |            | 1.1.2 Major Operations                   | 6  |

| 2.0 | Mess       | sage Passing Protocol                    | 7  |

|     | 2.1        | Unsolicited Messages                     | 7  |

|     | 2.2        | Solicited Messages                       |    |

| 3.0 | MPC        | 82389 Interfaces                         | 8  |

|     | 3.1        | Host CPU Interface                       |    |

|     | 3.2        | Parallel System Bus Interface            |    |

|     | 3.3        | Interconnect Interface                   |    |

|     | 3.4        | Basic Implementation with the MPC 82389  | 11 |

|     | 3.5        | Dual-Port Interface                      | 12 |

| 4.0 | MPC        | 82389 Operations                         | 13 |

|     | 4.1        | MULTIBUS II Message Passing              |    |

|     |            | 4.1.1 Unsolicited Transmit/Receive       |    |

|     |            | 4.1.2 Solicited Input/Output             |    |

|     | 4.2        | Memory and I/O References                |    |

|     | 4.3        | Local Interconnect Reference             | 15 |

|     | 4.4        | Remote Interconnect Reference            | 15 |

|     | 4.5        | Interconnect Replier Operations          |    |

|     | 4.6        | Dual-Port Replier Operations             |    |

|     | 4.7        | Central Services Modular Support         |    |

|     |            | 4.7.1 Additional CSM Requirements        |    |

| 5.0 | MPC        | 82389 Pin Description                    | 17 |

|     | 5.1        | PSB Signals                              | 17 |

|     |            | 5.1.1 Arbitration Operation Signal Group |    |

|     |            | 5.1.2 Address/Data Bus Signal Group      |    |

|     |            | 5.1.3 System Control Signal Group        |    |

|     |            | 5.1.4 Central Control Signal Group       |    |

|     |            | 5.1.5 Exception Operation Signal Group   |    |

|     | 5.2        | Dual-Port Memory Control Signals         |    |

|     | 5.3        | Local Bus Signals                        |    |

|     |            | 5.3.1 Data Bus                           |    |

|     |            | 5.3.2 Address/Status Signals             |    |

|     |            | <b>5</b>                                 |    |

|     |            | 5.3.4 Interrupt Signals                  |    |

|     | 5.4        | Interconnect Bus Signals                 |    |

| 6.0 | _          | age Dimensions                           |    |

| 7.0 |            | 82389 Electrical Data                    |    |

| 7.0 | 7.1        | Maximum Ratings                          |    |

|     | 7.1<br>7.2 | DC Specifications                        |    |

|     | 7.2        | AC Specifications                        |    |

|     | 7.5        | / 10 Opoomoudono                         |    |

| HI | $\sim$ |   | r | Δ | C |

|----|--------|---|---|---|---|

|    | ч      | u |   | C | J |

|    | _      | _ |   | _ | _ |

**Tables**

| 1  | Multiprocessor Architecture                                               | 5  |

|----|---------------------------------------------------------------------------|----|

| 2  | Message Passing Performance Example                                       | 5  |

| 3  | MPC Bus Interfaces                                                        | 8  |

| 4  | MPC Implementation to Support References                                  | 11 |

| 5  | The MPC Implemented with Dual-Port Memory                                 |    |

| 6  | The MPC Uses Nine Dedicated Internal 32-Byte FIFO Buffers                 | 14 |

| 7  | Byte Lanes                                                                |    |

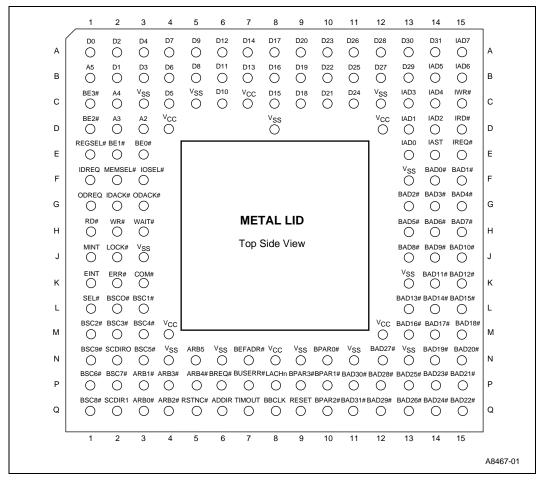

| 8  | MPC 82389 Pinout (View from Top Side)                                     | 28 |

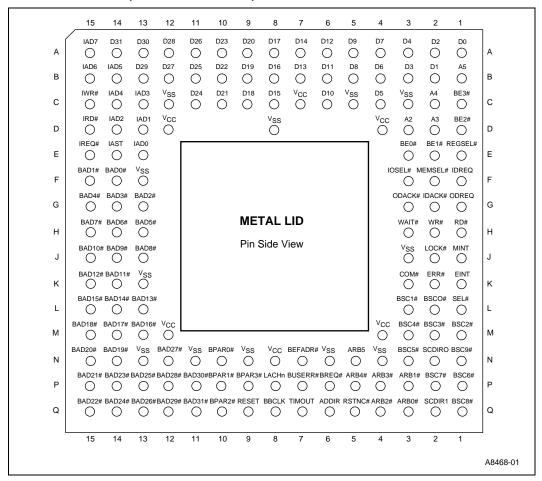

| 9  | MPC 82389 Pinout (View from Pin Side)                                     | 29 |

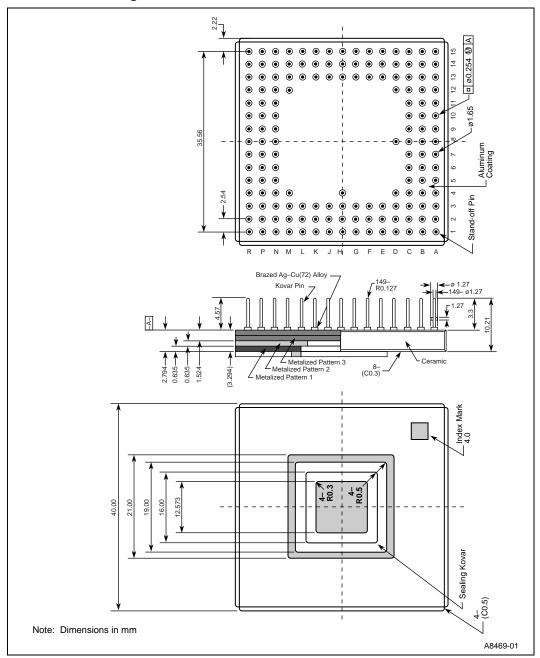

| 10 | 149-Pin PGA Package Dimensions                                            |    |

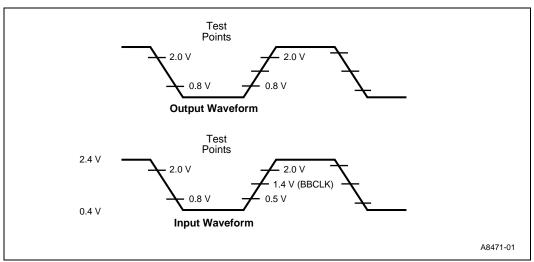

| 11 | AC Test Waveforms                                                         |    |

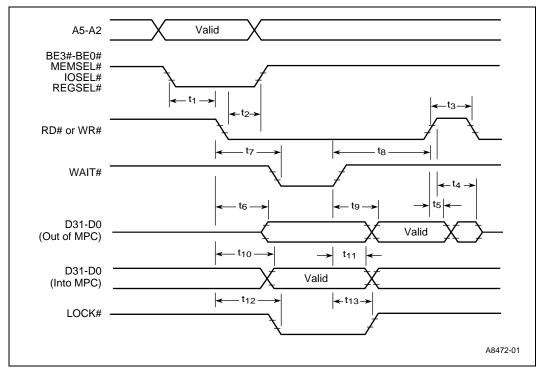

| 12 | Host CPU Interface Reference Operation Timing                             | 34 |

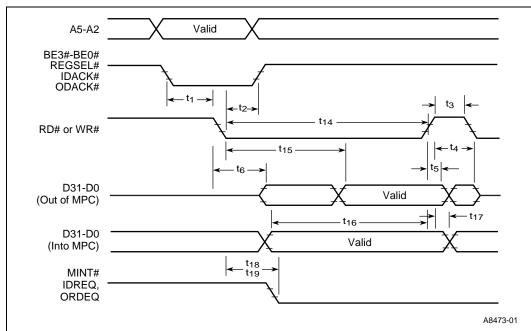

| 13 | Host CPU Interface Register and DMA Operation Timing                      |    |

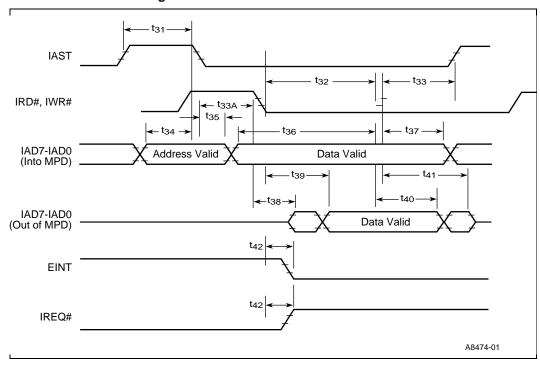

| 14 | Interconnect Bus Timing                                                   |    |

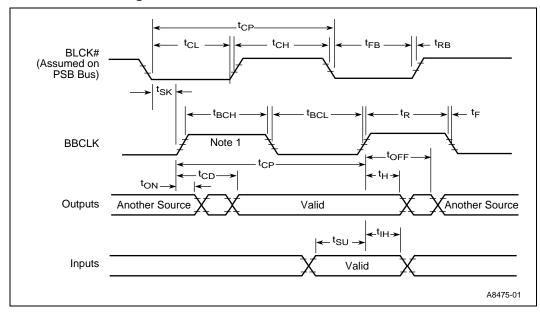

| 15 | PSB Interface Timing                                                      |    |

| 16 | AC Test Load                                                              |    |

|    |                                                                           |    |

| 1  | Summary of BW Signal Functions                                            | 19 |

| 2  | Signal States During Reset                                                | 20 |

| 3  | Valid Byte Enable Combinations                                            | 23 |

| 4  | Byte Enable Usage for DMA Control                                         |    |

| 5  | MPC Signal Summary                                                        |    |

| 6  | DC Specifications                                                         |    |

| 7  | Host CPU Bus AC Specifications ( $V_{CC} = 5V 15\%$ , TA = 0°C to + 70°C) |    |

| 8  | Interconnect Bus AC Specifications (Vcc = 5V ±5%, TA = 0°C to +70°C)      |    |

| 9  | PSB Interface AC Specifications (Vcc = 5V ±5%, TA = 0°C to + 70'C)        |    |

|    |                                                                           |    |

### 1.0 MPC 82389 Introduction

The 82389 Message Passing Coprocessor (MPC) is a highly integrated CMOS VLSI device which interfaces any microprocessor to the MULTIBUS II Parallel System Bus (PSB). The PSB is defined for easy access and sharing of resources in a processing environment which allows the existence of both intelligent and non-intelligent add-in boards. The MPC complements the MULTIBUS II environment by providing an optimized interface for the PSB at its maximum bandwidth. The MPC also off-loads the host CPU, thus increasing system throughput, by providing the necessary bus arbitration, message passing protocol, error handling and interrupt control for a MULTIBUS II system. Figure 2 shows an example of the MPC's message passing performance.

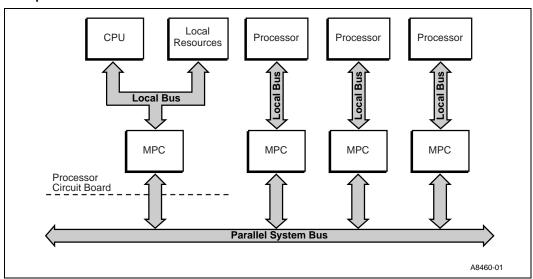

Figure 1. Multiprocessor Architecture

Figure 2. Message Passing Performance Example

### 1.1 Functional Overview

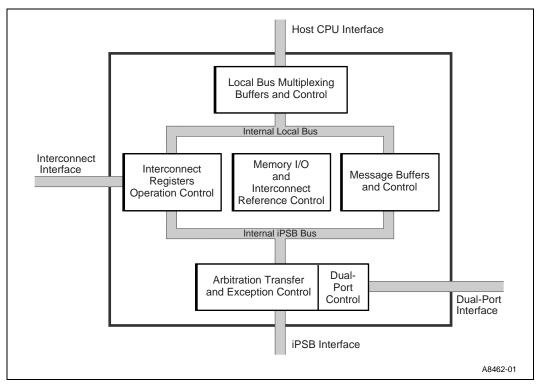

The MPC 82389 is a bus interface controller which off-loads the host CPU for interprocessor communication on the PSB. The MPC 82389 features four interfaces which support a variety of data transfer operations.

#### 1.1.1 MPC 82389 Interfaces

The three primary interfaces to the MPC (PSB Interface, Host CPU Interface and Interconnect Interface) all function asynchronously to one another. This is accomplished through the use of internal latches and FIFOs that allow references to occur simultaneously on all interfaces. In addition to the three primary interfaces, the MPC contains a Dual-Port Interface which provides compatibility with past system implementations and software.

• PSB Interface

The PSB Interface is the synchronized, shared data pathway in the MULTIBUS II system.

· Host CPU Interface

The Host CPU Interface is a set of addressable registers and ports that is the private pathway for the local microprocessor on the MULTIBUS II board.

Interconnect Interface

The Interconnect Interface provides a path for added board functionality that is independent from the host CPU.

Dual-Port Interface

The Dual-Port Interface supports shared memory references.

### 1.1.2 Major Operations

Unsolicited and Solicited Message Passing

The unsolicited and solicited message passing protocol is an interprocessor communication protocol which allows an intelligent agent<sup>1</sup> on the PSB to communicate with another agent without any CPU intervention at full PSB speed.

PSB Memory and I/O Single-Cycle Access

The MPC performs single-cycle read/write transfers from the host to memory and I/O locations across the PSB. The MPC handles bus arbitration, parity generation and error detection without CPU intervention.

Local Interconnect Access

The host CPU and other agents on the PSB can access local interconnect space via the MPC.

• Remote Interconnect Access

MPC enables host CPU to access remote interconnect locations assigned to other PSB agents.

• Dual-Port Memory Access Support

Other PSB agents can access dual-port memory via the MPC.

• Central Services Module (CSM) support

The MPC has a minimal set of built-in CSM support features which allow the CSM to be incorporated into any MULTIBUS II board design.

<sup>1.</sup> An agent is any device with an interface to the PSB.

# 2.0 Message Passing Protocol

The MULTIBUS II architecture designates the data transfer protocol between agents on the PSB as message passing. Message passing allows agents to transfer variable amounts of data at maximum PSB speed. The MPC fully supports the PSBs standardized message passing protocol. The entire handshaking procedure between agents on the PSB is handled by the MPC without CPU intervention.

There are two types of messages that can be transmitted from one agent to another: Unsolicited Messages and Solicited Messages.

# 2.1 Unsolicited Messages

Unsolicited messages are short, fixed-length messages that can arrive unexpectedly. Unsolicited messages can be transmitted without explicit buffer allocation and without synchronization between sending and receiving agents on the PSB. Unsolicited messages are often referred to as intelligent or virtual interrupts, since they can be used as a signaling mechanism between boards, replacing traditional system interrupts and freeing the CPU from having to poll for information. In addition, unsolicited messages allow for up to 28 bytes of user data.

# 2.2 Solicited Messages

Solicited messages are used to transfer large amounts of data. Up to 16 Mbytes (less 1 byte) of data can be transferred in a single solicited message transmission sequence. Solicited message transfers require the receiving agent to explicitly allocate a buffer. Buffer negotiation between sending and receiving agents is handled using unsolicited messages as follows:

- A buffer request message initiates a solicited message transfer. It requests the receiving agent to allocate a buffer large enough to hold the solicited data.

- A buffer grant message must be returned by the receiving agent before the solicited data can be transferred. The buffer grant informs the sending agent MPC that a buffer has been allocated and indicates that the receiving agent MPG is ready to begin the data transfer.

- A buffer reject message is returned by the receiving agent if a buffer for the solicited data cannot be provided. In this case, the rejection is final, and no further action is required.

If a DMA controller handles the solicited message transfer, DMA controller setup is also needed. Typically, the sending agent programs its DMA controller immediately before sending a buffer request, and the receiving agent programs its DMA controller immediately before sending a buffer grant.

Once solicited buffer negotiation is complete (the sending agent MPC has received a buffer grant), the agents transfer the data without further intervention. The data is sent as a series of solicited packets on the sending agent local bus. The MPCs perform transfer and routing across the PSB automatically. At the end of the solicited data transfer, both the sending and receiving agents get a completion indication from their local MPC.

# 3.0 MPC 82389 Interfaces

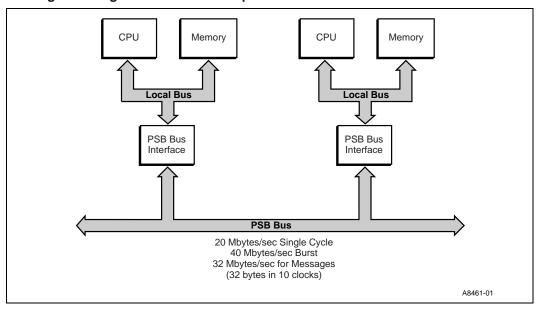

The MPC 82389 features a total of four Interfaces. The three primary Interfaces are the Host CPU Interface, PSB Interface and the Interconnect Interface. The MPC also has a Dual-Port Memory Interface which provides compatibility with past system implementations and software. Figure 3 shows the four MPC bus interfaces.

Figure 3. MPC Bus Interfaces

### 3.1 Host CPU Interface

The Host CPU Interface connects an 8-, 18-, or 32-bit processor to the MPC. The Host CPU Interface supports direct references to memory, I/O, and interconnect address space on the PSB. The entire Host CPU Interface is composed of three sub-interfaces:

#### • Register Sub-Interface

The Register Sub-Interface is composed of a bank of 8-bit registers on the Host CPU Interface. These registers provide the configuration, status and command interface for the host CPU. A host register operation is independent from operations which may be in progress at the MPCs other interfaces. However, some host register operations are dependent on the internal state of the MPC. In host register operations, the maximum duration is decided by the strobe width. Thus, the number of wait states required at the local interface is under the control of the host CPU.

#### • Reference Sub-Interface

The Reference Sub-Interface supports direct references to memory, I/O, and interconnect address space on the PSB. Memory and I/O references are initiated by the CPU to the MPC. The MPC responds to a memory or I/O reference by putting the CPU on hold while arbitrating for the PSB. The CPU is held in wait states until the reference is complete or until a bus exception condition occurs on the PSB. The Reference Sub-Interface supports both read and write operations to the registers. The local interconnect address space is differentiated from the interconnect address on the PSB by the bit pattern stored in the MPCs slot address register.

#### DMA Sub-Interface

The DMA Sub-Interface supports data transfers between the local memory and the MPC during solicited message operations. The DMA Interface is designed to support either two-cycle or fly-by (single-cycle) read/write transfers. For two-cycle operations, the DMA controller performs one cycle into memory and another cycle to the MPC; a read command is used to get data from the MPC and a write command is used to put data into the MPC. Fly-by operations allow data to be transferred during a single bus cycle; a fly-by transfer uses a write command to get data from the MPC (corresponding to a memory write) and a read command to put data into the MPC (corresponding to a memory read). The higher performance possible with fly-by transfers mandates the alignment of data on 4-byte boundaries.

# 3.2 Parallel System Bus Interface

The Parallel System Bus (PSB) Interface is a full 32bit interface to other boards in the MULTIBUS II chassis. The PSB Interface supports:

• Parallel System Bus Arbitration

The MPC begins PSB access arbitration upon a request which is generated inside the MPC. This request could be the result of a synchronized PSB memory, I/O or interconnect reference request, or a message packet transmit request from the CPU.

• Data Transfer

The PSB Interface contains all the address/data lines and necessary control signals for data transfer. Those control signals provide the control mechanism between agents during transfer operations.

Error Handling

The MPC monitors errors generated during data transfer operations. The MPC recognizes data integrity problems on the PSB and bus time-out conditions.

### 3.3 Interconnect Interface

The Interconnect Interface is an independent 8-bit communication interface which allows the MPC to be connected to a microcontroller. (It is highly recommended that an 8051 or similar microcontroller be used on the Interconnect Interface.) This microcontroller performs tasks such as board configuration at startup and local diagnostics.

The interconnect apace of an agent is the only required bus space by the IEEE 1296 specification and has a 512-byte register range. Within this space the microcontroller can store the local operating and configuration parameters associated with the agent. For example, local diagnostics can be executed out of the rnicrocontroller and the results posted in the interconnect space.

Local resources on an agent gain access to interconnect space through the MPCs interconnect bus. A microcontroller connects to the interconnect bus for intelligent handling of interconnect operations. All interconnect bus signals are asynchronous to the bus clock and to the local bus signals.

# 3.4 Basic Implementation with the MPC 82389

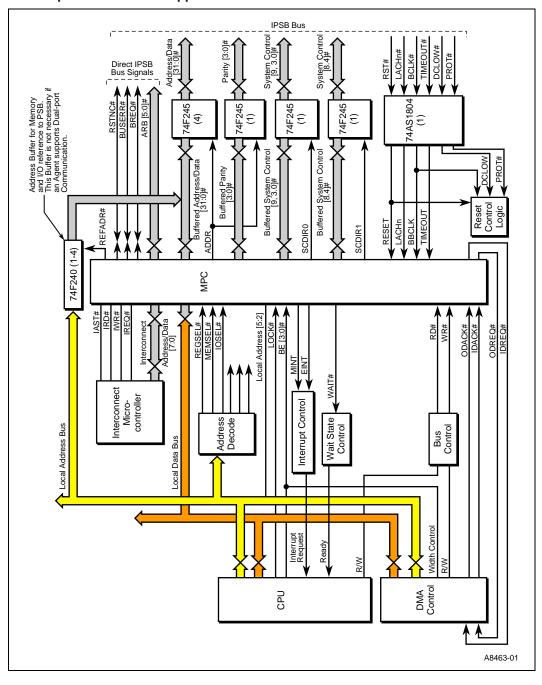

Figure 4 shows a basic implementation of the MPG 82389. Included in this implementation is the Interconnect Interface, the Host CPU Interface and the PSB Interface.

Figure 4. MPC Implementation to Support References

# 3.5 **Dual-Port Interface**

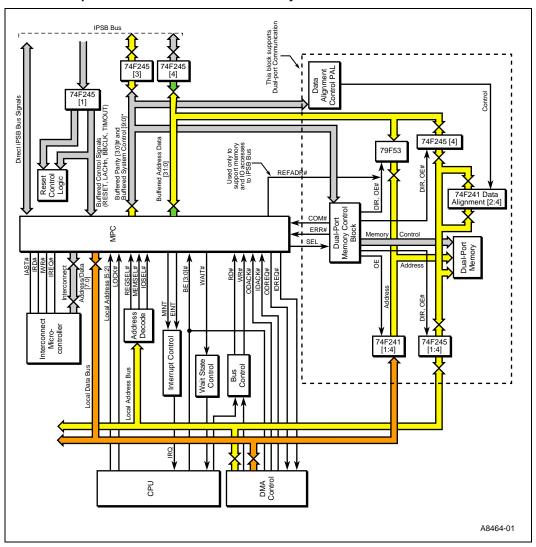

The Dual-Port interface supports shared memory accesses between agents on the PSB. In order to fully implement dual-port memory, some additional dual-port memory controller logic is required. Figure 5 shows an example of the MPC implemented with dual-port memory.

Figure 5. The MPC Implemented with Dual-Port Memory

# 4.0 MPC 82389 Operations

The primary function of the MPC 82389 is MULTIBUS II message passing. In addition to message passing, the MPC performs the following functions:

- Memory and I/O Reference

- Local Interconnect Reference

- Remote Interconnect Reference

- Interconnect Replier Operations

- Dual-Port Replier Operations

- Central Services Module Support

# 4.1 MULTIBUS II Message Passing

The MPC manages the routing of message packets as they flow between the interfaces of each MULTIBUS II agent in the system. For message traffic on the PSB, message decode logic on the PSB input bus determines message routing through the MPC. For the Host CPU Interface and Interconnect Interface, the MPC defines a signal protocol for message passing.

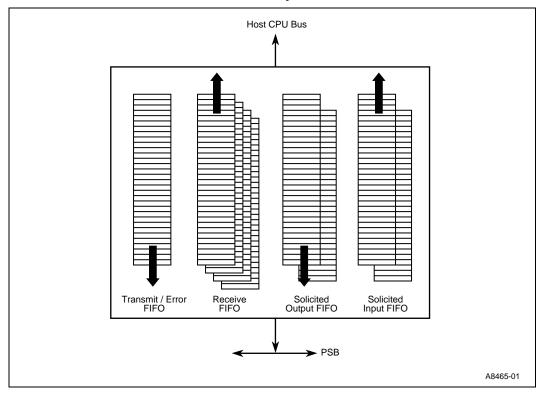

MULTIBUS II messages, both unsolicited and solicited, are transferred through nine dedicated internal FIFO buffers between the Host CPU Interface and PSB Interface. Unsolicited messages are intelligent (also called virtual) interrupts which notify the receiving agent to prepare for the receipt of solicited messages. Unsolicited messages use the Transmit/Error FIFO and the Receive FIFO. The Transmit FIFO holds a 32-byte packet for transmittal across the PSB. If there is an error in transmission, the Transmit FIFO becomes the Error FIFO, where the errant message can be read back along with error status. The Receive FIFO is a circular queue of four 32-byte buffers from which unsolicited messages are received from the PSB by the host CPU.

Solicited messages consist of information data packets which are transmitted between agents. Solicited messages use the Solicited Input FIFO and Solicited Output FIFO. These FIFOs are dual 32-byte buffers which are used for the temporary storage of solicited data packets as they travel between the Host CPU Interface and the PSB Interface. The solicited output header logic attaches header information to the solicited data packet before sending it onto the PSB. All FIFOs are able to operate independently and concurrently, thus creating a true multitasking message passing environment. Figure 6 shows the nine dedicated internal FIFO buffers.

Figure 6. The MPC Uses Nine Dedicated Internal 32-Byte FIFO Buffers

#### 4.1.1 Unsolicited Transmit/Receive

Unsolicited message passing sequences occur between the Host CPU Interface and the PSB Interface using FIFOs Internal to the MPC. FIFO status is available on the Host CPU Interface and in state machines internal to the MPC. On the Host CPU Interface, host register operations write bytes to the Transmit FIFO and read bytes from the Receive FIFO. On the PSB, the MPG manages the emptying and filling of the Transmit and Receive FIFOs using MULTIBUS II message passing protocol and the Transmit and Receive FIFOs on another agent MPC. For detailed information about message passing protocol across the PSB, see the *IEEE 1296 High Performance Synchronous 32-bN Bus Standard*.

### 4.1.2 Solicited Input/Output

Solicited transfers are pre-negotiated using unsolicited message sequences. Dedicated FIFOs (Solicited Input FIFO and Solicited Output FIFO) are then used for the transfer of solicited data packets. This allows large amounts of data to be moved between agents independently of unsolicited messages. In most cases, the solicited transfer occurs under DMA control, freeing the host CPU to handle other activities. The DMA controller uses the input channel DMA request/acknowledge and output channel DMA request/acknowledge signals along with the read/write signal to stream the data from/to the solicited FIFOs. On the PSB, the data is transferred in bursts using MULTIBUS II message passing protocol and similar solicited FIFOs on another agent MPC. The MPCs add header information to the packets on the PSB indicating source, destination and length. Data transfers through the solicited FIFOs can be set up for 8, 18 or 32 bits of data width on the Host CPU Interface, but occur at full 32-bit width on the PSB.

# 4.2 Memory and I/O References

Remote memory or I/O reference operations are Host CPU Interface operations that involve an access through the MPG to a resource across the PSB. This resource can be a dumb memory or I/O board. The remote reference can only be done through the MPC as a single-cycle operation (no block transfers) to the remote resource and can involve an unknown number of Wait states. Many MULTIBUS II CPU boards use an alternate path (such as the iLBX bus found on the Intel<sup>®</sup> iSBC boards) that is an independent extension of the local bus for full-speed and block transfer operations.

The host CPU initiates a memory or I/O reference by activating memory select (MEMSEL#¹) or I/O select (IOSEL#), A<5-2>, BE#<3-0>, with a RD# or WR# strobe. If necessary, LOCK# is activated to allow back-to-back accesses across the PSB, holding all other agents off the memory or I/O resource. The MPC activates its WAIT# output to indicate that the operation is in progress.

The date for reference operation proceeds through the MPC and PSB to a memory or I/O address on another agent. A data path from D<31-0> through the buffered address/data bus (BAD# 31-0>) is used for the data transfer. Data is latched internally in a reference data latch. Parity is generated to the PSB on BPAR<3-0> for the data on each write operation and checked on data read. Completion of the operation is indicated when the MPC deactivates the WAI# output.

The memory or I/O address for the reference operation is routed around the MPC through an external reference address latch. This latch is controlled by the REFADR signal from the MPC.

### 4.3 Local Interconnect Reference

A local interconnect reference operation is an access by the host CPU to the interconnect records maintained by the local interconnect microcontroller. The geographic interconnect address is preloaded into a pair of registers internal to the MPC. The upper five bits of the interconnect address determine whether the operation is local or remote. A data path from D<7-0> to the interconnect address/data bus (IAD<7-0>) is used. The microcontroller uses the interconnect request (IREQ#) output to sense the request. The request is serviced by the interconnect microcontroller through a sequence of accesses to registers within the MPC using the interconnect address strobe (IAST), interconnect read (IRD#), and interconnect write (IWR#) strobes, and the IAD multiplexed bus. The WAIT# signal is used as for memory and I/O references to indicate completion of the local interconnect reference operation.

### 4.4 Remote Interconnect Reference

A remote interconnect reference is an access by the host CPU to interconnect space on another agent. The host CPU requests a remote interconnect reference by writing the interconnect address to the same register used in the local interconnect request, except that the upper five bits of the interconnect address indicate the slot address of another agent on the PSB. The data flows through the MPC as in a remote memory or I/O reference, except that the data transfer occurs only on D<7-0>. The remote microcontroller services the request through an interconnect replier operation.

<sup>1.</sup> Indicates that the signal is active low.

### 4.5 Interconnect Replier Operations

When another agent performs a remote interconnect reference request, It gains access to local interconnect space through the MPC. The MPC decodes an interconnect request on the PSB for a slot ID match and signals the interconnect rnicrocontroller independently of the local bus interface. The microcontroller then handles the request in the same way as a local interconnect request.

# 4.6 Dual-Port Replier Operations

Other agents can access dual-port memory via the MPC. A memory access request on the PSB is decoded by the MPC for an address range match and serviced by the dual-port controller (external circuitry must be provided). The MPC provides only the handshaking path. Data transfer occurs directly on the BAD# bus. If a bus exception occurs while a dual-port memory reference is in progress, the MPC signals the dual-port controller to terminate the operation.

# 4.7 Central Services Modular Support

The IEEE 1296 specification defines the Central Services Module (CSM) that resides in Slot 0 of a MULTIBUS II system. The CSM is responsible for these functions:

- Reset sequencing (generates reset signal on the PSB)

- Assignment of card slot and arbitration IDs during reset initialization

- Generation of system wide clocks for all agents (bus clocks and time of day)

- · Generation of bus time-out

- Battery back-up of system constants (host ID, time of day, etc.)

The MPC has a minimal set of built-in CSM support features that allow the incorporation of CSM into any MULTIBUS II board design. The MPC, interconnect microcontroller, and a small amount of external circuitry can fully implement the CSM automatically when the board is inserted into Card Slot 0.

### 4.7.1 Additional CSM Requirements

In addition to the interconnect microcontroller and the MPC, the following functions must be provided through external logic:

- clock generation

- PSB reset generation

- cold/warm start detection

- PSB time-out generation

The clock generator provides the bus clock (BCLK#) and central clock (CCLK#) signals to the PSB. The reset generator provides the hardware reset line (RESET#) to all agents on the PSB. Cold/warm start detection circuitry distinguishes between a power-up reset and a warm-start reset. On power-up the CSM assigns arbitration and slot IDs. The PSB time-out function determines when the PSB is hung.

# 5.0 MPC 82389 Pin Description

This section describes each signal pin (or group of pins) on the MPC. Emphasis is placed on giving as much information as possible to ease the task of designing hardware associated with the MPC signal pins. The pins are described in terms of these functional groups:

- · PSB interface

- Local bus (host CPU) interface

- Dual-port memory control

- Interconnect bus interface

### 5.1 PSB Signals

The PSB signals provide the interface to other boards in the MULTIBUS II chassis. Very little support circuitry is required for this part of the board. Only high-current drivers and reset control logic is needed. Some MPC signal pins have built-in open collector high-current drivers that allow connection directly to the PSB. For complete information on the PSB, see the IEEE 1296 High Performances Synchronous 32-bit Bus Standard document.

PSB signals fall into five groups, depending on function:

- Arbitration operation signal group

- Address/data bus signal group

- System control signal group

- · Central control signal group

- Exception operation signal group

Unless otherwise stated, all PSB signals are synchronous to the bus clock.

Note:

High current drivers used to drive the buffered address/data (8 M bus should be controlled with minimal logic. This is to limit propagation delays and avoid possible bus contention problems. Ensure that the placement of these drivers and the MPC is done as close to the PSB (the P1 connector on a MULTIBUS II board) as possible to minimize signal stub lengths and capacitive loading.

# 5.1.1 Arbitration Operation Signal Group

These MPC pins are used by an agent to obtain exclusive access to the PSB. They are all high-current drive, open-collector signals. Following are descriptions of each signal.

- BREQ# (Bus Request)

- BRIM is a bidirectional open-collector signal that connects directly to the PSB. As an input to the MPC, it indicates that agents are awaiting access to the bus. As an output, the MPC asserts BREO# to request PSB access.

- ARB#<5-0> (Arbitration)

- ARB#<5-0> are bidirectional, open-collector signals that connect directly to the PSB. ARB#<5-0> are used (during normal operation) to identify the mode and arbitration priority of an agent during an arbitration cycle. During system initialization (while reset is active), the central services module (CSM) drives these signals to initialize slot and arbitration IDs.

### 5.1.2 Address/Data Bus Signal Group

This signal group includes a 32-bit multiplexed address/data path (BAD#<31-0>) and the byte parity signals (BPAR#<3-0>). These signals require buffering through bus transceivers before connection to the PSB. This signal group also Includes the bus transceiver control signals (ADDIR and REFADR#).

BAD#<31-0> (Buffered Address/Data)

SAT5<31-0> are the 32 bidirectional, multiplexed address/data signals that provide the interface to the PSB address/data bus (AD#) when buffered through 74F245 or equivalent bus transceivers.

**Note:** Do not use pull-up resistors to drive the BAD bus high. If pull-up resistors are present, the MPC cannot guarantee valid logic states with proper timing.

- BPAR#<3-0> (Buffered Parity)

BPAR# are four signals that provide parity for the 32-bit BAD# bus. These bidirectional lines connect to the PSB PAR#<3-0> signals through a 74F245 or equivalent transceiver. These signals are used to receive byte parity for incoming data and to drive byte parity for outgoing data.

- ADDIR (Address/Data Direction)

ADDIR is an output that provides direction control over the bus transceivers buffering the BAD#<31-0> and BPAR#<3-0> signals. In the high state, this signal causes the transceivers to drive address/data information along with parity onto the PSB. In the low state, this signal causes address/data information and parity to be received from the PSB.

- REFADR# (Reference Address Enable)

REFADR# is an output used to enable external reference address buffers during reference operations. Asserting this signal places the reference address onto the BAD# bus. The address path enabled by this signal is only used for memory and I/O reference operations to the PSB. It is not used during message passing or for PSB references to interconnect space.

### 5.1.3 System Control Signal Group

The system control signal group on the PSB provides a control mechanism between agents during transfer operations.

• BSC#<9-0> (Buffered System Control)

BSC#<9-0> is a group of ten bidirectional signals that conned to the PSB through 74F245 or equivalent transceivers. Agents on the PSB use these signals for commands or status, depending on the phase of the operation. The function of each of these lines during request and reply phases of transfer operations is summarized in Table 1.

Table 1. Summary of BW Signal Functions

| Signal | Request Phase              | Reply Phase              |

|--------|----------------------------|--------------------------|

| BSC0#  | Bus Owner in Request Phase | Bus Owner in Reply Phase |

| BSC1#  | LOCK                       | LOCK                     |

| BSC2#  | Data Width                 | End-of-Transfer          |

| BSC3#  | Data Width                 | Bus Owner Ready          |

| BSC4#  | Address Space              | Replying Agent Ready     |

| BSC5#  | Address Space              | Agent Status             |

| BSC6#  | Read/Write Data Transfer   | Agent Status             |

| BSC7#  | Reserved                   | Agent Status             |

| BSC8#  | Even Parity on BSC<7-4>    | Even Parity on BSC<7-4>  |

| BSC9#  | Even Parity on BSC<3-0>    | Even Parity on BSC<3-0>  |

te: The end-of-transfer (EOT) handshake in single-cycle operations is indicated by BSC<4,3,2> as follows: the requesting MPC drives BSC#<3,2> end waits for the replier to drive BSC4#; when the replier responds, the EOT handshake is complete.

• SCDIR<1,0> (System Control Direction)

SCDIR<1,0> are output signals that provide direction control of the 74F245 transceivers driving and receiving BSC#<9-0>. SCDIR0 provides control for BSC#<9,3-0>, while SCDIR1 provides control for BSC#<8-4>. When either signal is high, the bus transceiver drives BSC# signals onto the PSB. When either signal is low, signals on the PSB are driven onto the BSC# lines.

### 5.1.4 Central Control Signal Group

The central control signal group provides bus status and control information for devices operating on the PSB. The CSM, residing in slot 0 of the MULTIBUS II backplane, generates BCLK#, LACHn, and RESET.

• BBCLK (Buffered Bus Clock)

BBCLK is received by the MPC to synchronize all operations on the PSB. This input should be connected to BCLK# (on the PSB) using a 74AS1804 or equivalent inverting buffer. The falling edge of BCLK# provides all system timing references. BBCLK normally has a fixed operating frequency of 10 MHz.

**Note:** BCLK# can be varied from DC to 10 MHz. You may use this feature for single-stepping on the PSB during debugging.

• LACHn (ID Latch)

LACHn is an input signal used during initialization of slot and arbitration IDs (where "n" is the slot number). When the RESET signal is active, LACHn indicates when a slot or arbitration ID is available and should be latched. LACHn is an active high input and should be connected to the LACHn# signal on the PSB with a 74AS1804 or equivalent inverting buffer.

#### RESET

Reset is an input that places the MPC in a known state. Only the parts of the MPC involved with initialization of slot and arbitration IDs remain unaffected. RESET is an active high input and should be connected to the RST# signal on the PSB with a 74AS1804 or equivalent inverting buffer.

If the MPC is used in a CSM implementation, the interconnect microcontroller and some external logic controls RESET. On power up, the CSM generates the RESET signal to the backplane. Within a few clock cycles, receiving MPCs complete their internal reset. Table 2 summarizes the states of MPC signal outputs while the RESET signal is active.

Table 2. Signal States During Reset

| Signal     | Reset State | Signal       | Reset State |

|------------|-------------|--------------|-------------|

| BREQ#      | Z(H)        | ARB#<5-0 >   | Z(H)        |

| BAD#<31-0> | Z           | D<31-0>      | Z           |

| ADDIR      | L           | SEL#         | Н           |

| REFADR#    | Н           | WAIT#        | Н           |

| BSC#<9-0>  | Z           | ODREQ, IDREQ | L           |

| SCDIR<1,0> | L           | MINT, EINT   | L           |

| BUSERR#    | Z(H)        | RSTNC#       | L           |

#### NOTE:

H = Electrical high state.

L = Electrical low state.

Z = High Impedance (tri-state).

#### • RSTNC# (Reset Not Complete)

Agents assert RSTNC# during reset to extend the initialization time period beyond the time that RESET allows. RSTNC# is a bidirectional OR-tied signal on the PSB that is low when one or more agents have not completed their reset requirements. Agents cannot perform bus operations while RSTNC# is asserted. However, agents may access local interconnect space if your firmware implementation allows such access. RSTNC# is an open-collector signal with high-current drive that connects directly to the PSB.

### 5.1.5 Exception Operation Signal Group

The exception operation signal group indicates exception errors on the PSB.

• BUSERR# (Bus Error)

The MPC asserts BUSERR# when a data Integrity problem on the PSB Is detected during a transfer operation. Possible <u>problems</u> are: detection of a parity error on the BAD# bus or BSC# lines, or a protocol error associated with the BSC# lines. BUSERR# is a bidirectional, open-collector signal with high current drive that connects directly to the PSB.

• TIMOUT (Time-out)

TIMOUT, as an input from the PSB, is used to detect a bus time-out condition. The CSM activates this signal when it determines that an agent is taking too much time asserting a handshake signal, or if a bus owner has maintained bus ownership for an excessive length of time. The exact amount of time is a fixed value relative to BBCLK that is approximately 10,000 clock cycles (1 ms 10 MHz). TIMOUT is an active high input to the MPC and must be connected to the TIMOUT# signal of the PSB through a 74AS1804 or equivalent inverting buffer.

When the MPC is configured for CSM operation, TIMOUT becomes an output, generating the time-out condition to all agents on the PSB. In this case, the TIMOUT pin should be connected to the PSB by a 74F242 driver or equivalent.

# 5.2 Dual-Port Memory Control Signals

The MPC provides these signals (SEL#, COM#, ERR#) to support dual-port memory. In order to fully implement dual-port memory, some additional dual-port memory controller logic is required.

• SEL# (Select)

The SEL# output indicates that a dual-port memory access is in progress. SEL# initiates dual-port operations and may be used to enable the dual-port data buffers onto the BAD# bus. When the MPC receives the EOT handshake, or If the MPC detects an exception, it deactivates SEL#.

• COM# (Complete)

COM# is an input to the MPC. The dual-port memory controller asserts COM# to indicate completion of a dual-port access. COM# is assumed to be synchronous to the bus clock. After the memory controller has asserted COM#, the MPC asserts the replier ready (BSC4#) signal on the next bus clock. The memory controller cannot deassert COM# until the EOT handshake is complete on the PSB. This requires that the memory controller monitor the PSB for the EOT handshake.

• ERR# (Error)

ERR#, an input to the MPC, is asserted by the dual-port memo controller to signal a memory data parity error. ERR# must be stable (high or low) whenever COM# Is asserted. The MPC responds to this signal by completing the replier handshake on the PSB using a *data error* agent error code. This signal may be asynchronous to the bus clock since it is qualified by the COM# signal.

# 5.3 Local Bus Signals

The MPC local bus allows many types of microprocessors, perhaps with differing data widths, byte alignment, and bit ordering, to connect to the MULTIBUS II PSB. This microprocessor Is often referred to as the *host CPU* on the MULTIBUS II processor board. The MPC has five signal groups on the local bus:

- Data bus

- Address/status signals

- Transfer control

- Interrupt signals

- DMA control lines

#### 5.3.1 Data Bus

The local data bus is the signal path for data transfers between the host CPU and the MPC.

• D<31-0>

D<31-0> is the 32-bit local data bus. Although this is a 32-bit interface, the MPC allows operation with processors using 8-, 16-, or 32-bit data busses.

**Note:** Intel® CPU architecture defines bit 0 and byte 0 as least significant. When connecting non-Intel processors to the MPC local data bus, it is important that this bit and byte ordering be maintained across the PSB. This allows agents of differing CPU types to work together in a single chassis. If byte-swapping is needed, see the discussion of the *byte enable* (BE<3-0>) signal pins.

### 5.3.2 Address/Status Signals

The address/status signals select or identify all MPC operations over the local bus.

• A<5-2> (Address)

The address inputs select MPC registers for message and interconnect space operations. A1 and A0 are omitted to provide a consistent register address for all data bus width options. A<5-2> are qualified by RD# or WR# and therefore must be stable within the specified set-up and hold window.

• MEMSEL# (Memory Select)

This MPC input signal tells the MPC that the current operation is a memory reference across the PSB. MEMSEL# is qualified by RD# or WR# and therefore must be stable within the specified set-up and hold window.

**Note:** MEMSEL#, IOSEL#, REGSEL#, IDACK#, and ODACK# are mutually exclusive. In order to be valid, no more than one should be active during the same set-up and hold window.

• IOSEL# (I/O Select)

This input signal tells the MPC that the current operation is an I/O reference to the PSB. IOSEL# is qualified by RD# or WR# and therefore must be stable within the specified set-up and hold window.

# intal

#### 82389 Message Passing Coprocessor A Multibus II Bus Interface Controller

#### • REGSEL# (Register Select)

This Input signal Is used to identify MPC register operations. REGSEL# is qualified by RD# or WR# and therefore must be stable within the specified set-up and hold window.

#### LOCK#

This input signal allows back-to-back operations to be performed on the PSB or local interconnect space. When the bus owner activates LOCK#, all other agents are held off the PSB or local resource until LOCK# is deactivated.

#### • BE#<3-0> (Byte Enable)

These input signals, generated by the host CPU or DMA controller, validate bytes on the data bus. BE#<3-0> are qualified by RD# or WR# and therefore must be stable within the specified set-up and hold window. BE#<3-0> correspond to data bytes 3 through 0 on the data bus (where byte 3 is D<31-24>). For remote reference operations, only combinations supported by the IEEE 1296 specification are valid.

A 32-bit local bus requires that all byte enable and data signals are used. For 16-bit local buses, BE1# and BE2# are used to Indicate which of the two bytes contain valid data, and only D<15-0> aroused. For 8-bit local bus operations, BE1# and BE0# are used to select which byte of the PSB carries the valid data byte. This mode uses only D<7-0> (on the local bus). Note that during all read operations, the MPC drives all data lines (D<31-0>). Consecutive accesses to message FIFOs must be in ascending byte sequence 0, 1, 2, 3 in any non-overlapping combination.

Table 3 shows the valid byte enable combinations for both the local data bus (D<31-0>) and the PSB (AD#<31-0>):

| Table 3. Valid Byte Enabl | e Combinations |

|---------------------------|----------------|

|---------------------------|----------------|

| BE3# | BE2# | BE1# | BE0# | D31-24 | D23-16 | D15-8 | D7-0 | AD31-24 | AD23-16 | AD15-8 | AD7-0 |

|------|------|------|------|--------|--------|-------|------|---------|---------|--------|-------|

| L    | L    | L    | L    | V3     | V2     | V1    | V0   | V3      | V2      | V1     | V0    |

| L    | L    | L    | Н    | V3     | V2     | V1    | Х    | V3      | V2      | V1     | Х     |

| Н    | L    | L    | L    | Х      | V2     | V1    | V0   | Х       | V2      | V1     | V0    |

| L    | L    | Н    | Н    | V3     | V1     | Х     | Х    | Х       | Х       | V3     | V2    |

| Н    | L    | L    | Н    | Х      | V2     | V1    | Х    | Х       | V2      | V1     | Х     |

| Н    | Н    | L    | L    | Х      | Х      | V1    | V0   | Х       | Х       | V1     | V0    |

| L    | Н    | Н    | Н    | V3     | Х      | Х     | Х    | Х       | Х       | V3     | Х     |

| Н    | L    | Н    | Н    | Х      | V2     | Х     | Х    | Х       | Х       | Х      | V2    |

| Н    | Н    | L    | Н    | Х      | Х      | V1    | Х    | Х       | Х       | V1     | Х     |

| Н    | Н    | Н    | L    | Х      | Х      | Х     | V0   | Х       | Х       | Х      | V0    |

| L    | Н    | L    | Н    | Х      | Х      | Х     | V0   | Х       | Х       | V0     | Х     |

| L    | Η    | Н    | L    | Х      | Х      | Х     | V0   | Х       | Х       | Х      | V0    |

#### NOTES:

L = Electrical low state (active)

H = Electrical high state (inactive)

Vn = Valid data bytes

X = Active bytes with undefined data

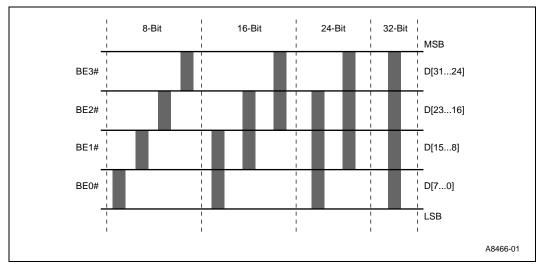

For the 32-bit host interface, legal combinations of byte enables form *byte lanes*: the paths where valid data bytes are present during a single transfer on the local data bus (as well as in the MULTIBUS II environment). Non-Intel microprocessors can use byte lanes to perform byte-swapping or other data manipulations in hardware. Figure 7 illustrates the legal byte lanes as they relate to byte enable combinations:

Figure 7. Byte Lanes

Each shaded box in Figure 7 represents a valid byte lane for a given combination of 99 during a single read or write operation. There are four types of byte lanes: 8-, 18-, 24- and 32-bit. Bit and byte ordering follow the Intel standard of bit or byte 0 as least significant. Assume that invalid byte lanes contain any value of data (i.e., non-constant). Take precautions (masking in software, etc.) to ensure that invalid data does not cause problems.

When using a DMA controller to handle solicited data transfers to/from local memory, misalignment of data in memory and resulting partial packets are handled using the BE# lines. The DMA interface of the MPC provides support by only incrementing internal pointers (or detecting completion) when the proper byte-enable signal is active. Table 4 shows which BE# line the MPC recognizes for partial packets:

Table 4. Byte Enable Usage for DMA Control

| DMA Width | Bytes Remaining | Byte Enable Recognized |

|-----------|-----------------|------------------------|

| 32-bit    | > 3             | BE3#                   |

| 32-bit    | 3               | BE2#                   |

| 32-bit    | 2               | BE1#                   |

| 32-bit    | 1               | BE0#                   |

| 16-bit    | > 1             | BE1#                   |

| 16-bit    | 1               | BE0#                   |

| 6-bit     | > 0             | BE0#                   |

### 5.3.3 Transfer Control Signals

Transfer operation control to the MPC over the local bus is provided by two commend signals and a wait signal. This handshake provides fully interlocked (two-sided handshake) operation.

• RD# (Read)

This Input signal starts a read operation. RD# must transition cleanly, since it is used to qualify other signals in the read operation.

• WR# (Write)

This input signal starts a write operation. WR# must transition cleanly, since it is used to qualify other signals in the write operation.

WAIT#

WAIT# is an MPC output signal used to extend a transfer operation. The signal is used by the MPC for all accesses that require synchronization to another resource. It is activated when a command goes active and deactivated when the operation is completed.

### 5.3.4 Interrupt Signals

Interrupt signals are used to inform the host CPU that the MPC requires service. The MPC generates two signals: one for message operations and one for reference errors.

• MINT (Message Interrupt)

The MINT output signal is used for all message-related signaling to the host CPU. This includes the arrival of an unsolicited message, the availability of the transmit FIFO, the completion of a solicited transfer, and an error-on message transfer.

• EINT (Error Interrupt)

The EINT output signal is used to signal all errors related to memory, I/O, or interconnect apace operations. Internal registers in the MPC provide exact details of the error via interconnect space.

### 5.3.5 DMA Control Signals

The MPC provides four DMA control signals that connect with an external DMA controller.

- ODREQ (Output Channel DMA Request)

ODREQ is an output signal that enables DMA transfers to the MPC (i.e., output to the PSB).

This signal behaves as a normal DMA request line during solicited message output operations.

ODREQ is activated during the transfer phase of a solicited message operation when the solicited output FIFO is empty. The DMA controller responds to ODREQ by moving data from local memory to the FIFO for transfer to a receiving agent on the PSB.

- IDREQ (Input Channel DMA Request)

IDREQ is an output signal that enables DMA transfers from the MPC (i.e., input from the PSB). This signal behaves as a normal DMA request line during solicited message input operations. IDREQ is activated during the transfer phase of a solicited message operation when the solicited input FIFO is full. The DMA controller responds to ODREQ by moving data from the FIFO to local memory. When the FIFO is emptied, IDREQ is deactivated.

- ODACK# (Output Channel DMA Acknowledge)

ODACK# is generated by the DMA controller in response to an output channel DMA request.

ODACK# is qualified by RD# or WR# and therefore must be stable within the specified set-up and hold window.

**Note:** MEMSEL#, IOSEL#, REGSEL#, IDACK#, and ODACK# are mutually exclusive. In order to be valid, no more than on should be active during the same set-up and hold window.

IDACK# (Input Channel DMA Acknowledge)

IDACK# is generated by the DMA controller in response to an input channel DMA request.

IDACK# is qualified by RD# or WR# and therefore must be stable within the specified set-up and hold window.

# 5.4 Interconnect Bus Signals

Brief descriptions of the interconnect bus signal pins are given here.

• IAD<7-0> (Interconnect Address/Data)

IAD<7-0> is an 8-bit, bidirectional, multiplexed address and data bus intended to interface directly to a microcontroller. In addition to the MPG, other interconnect accessible local resources can be connected to this bus.

• IREQ# (Interconnect Request)

The MPC asserts this output signal when an interconnect operation has been requested from either the local bus or the PSB. The MPC asserts IREQ# to the interconnect microcontroller at different times for read and write operations. For a read operation, IREQ# Is asserted immediately after detecting an address match between the requested address and an internal register. For a write operation, IREQ# is delayed until valid data is available (i.e., BSC3# is asserted). In either case, if the local bus interface has locked the local interconnect space, IREQ# is inhibited.

• IAST (interconnect Address Strobe)

IAST is a signal from the microcontroller that tells the MPC that a valid address is on the interconnect bus. IAST may be directly connected to the ALE (Address Latch Enable or equivalent) output of most microcontrollers. IAST must provide clean transitions.

• IRD# (Interconnect Bus Read)

The microcontroller asserts IRD# to perform a read operation to one of the MPC interconnect interface registers. IRD# must provide clean transitions.

**Note:** When IRD# and IWR# are activated at the same time, all MPC outputs are disabled. Use this feature to disable the MPC in board test applications.

• IWR# (Interconnect Write)

The microcontroller asserts IWR# to perform a write operation to one of the MPC interconnect interface registers. IWR# must provide clean transitions.

# 6.0 Package Dimensions

The MPC 82389 is packaged in a 149-pin Ceramic Pin Grid Array (PGA). The pins are arranged 0.100 inch (2.54 mm) center-to-center, in a 15 x 15 matrix. Please refer to Figure 10 for case outlines.

A wide variety of sockets are available including the zero-insertion force socket for prototypes.

Figure 8. MPC 82389 Pinout (View from Top Side)

Figure 9. MPC 82389 Pinout (View from Pin Side)

Table 5. MPC Signal Summary

| Mnemonic        | Туре    | Pin # | Mnemonic        | Туре    | Pin# | Mnemonic        | Туре    | Pin # |

|-----------------|---------|-------|-----------------|---------|------|-----------------|---------|-------|

| V <sub>CC</sub> |         | D4    | REFADR          | 0       | N7   | IAST            | I       | E14   |

| A5              | 1       | B1    | ADDIR           | 0       | Q8   | IRD#            | 1       | D15   |

| A4              | I       | C2    | BPAR3#          | I/O     | P9   | IWR#            | I       | C15   |

| A3              | I       | D2    | BAD31#          | I/O     | Q11  | IAD7            | I/O     | A15   |

| A2              | I       | D3    | BAD30#          | I/O     | P11  | IAD6            | I/O     | B15   |

| BE3#            | I       | C1    | BAD29#          | I/O     | Q12  | IAD5            | I/O     | B14   |

| BE2#            | I       | D1    | BAD28#          | I/O     | P12  | IAD4            | I/O     | C14   |

| BE1#            | I       | E2    | BAD27#          | I/O     | N12  | IAD3            | I/O     | C13   |

| BE0#            | I       | E3    | BAD26#          | I/O     | Q13  | IAD2            | I/O     | D14   |

| IOSEL#          | I       | F3    | BAD25#          | I/O     | P13  | IADI            | I/O     | D13   |

| MEMSEL#         | I       | F2    | BAD24#          | I/O     | Q14  | IAD0            | I/O     | E13   |

| REGSEL#         | I       | E1    | BAD23#          | I/O     | P14  | V <sub>CC</sub> |         | D12   |

| IDACK#          | ı       | G2    | BAD22#          | I/O     | Q15  | V <sub>SS</sub> |         | C12   |

| ODACK#          | ı       | G3    | BAD21#          | I/O     | P15  | D31             | I/O     | A14   |

| IDREQ           | 0       | F1    | BAD20#          | I/O     | N15  | D30             | I/O     | A13   |

| ODREQ           | 0       | G1    | BAD19#          | I/O     | N14  | D29             | I/O     | B13   |

| WR#             | I       | H2    | BAD18#          | I/O     | M15  | D28             | I/O     | A12   |

| RD#             | I       | H1    | BAD17#          | I/O     | M14  | D27             | I/O     | B12   |

| WAIT#           | 0       | H3    | BAD16#          | I/O     | M13  | D26             | I/O     | A11   |

| V <sub>SS</sub> |         | J3    | BAD15#          | I/O     | L15  | D25             | I/O     | B11   |

| MINT            | 0       | J1    | BAD14#          | I/O     | L14  | D24             | I/O     | C11   |

| EINT            | 0       | K1    | BAD13#          | I/O     | L13  | D23             | I/O     | A10   |

| LOCK#           | 1       | J2    | BAD12#          | I/O     | K15  | D22             | I/O     | B10   |

| ERR#            | ı       | K2    | BAD11#          | I/O     | K14  | D21             | I/O     | C10   |

| SEL#            | 0       | L1    | BAD10#          | I/O     | J15  | D20             | I/O     | A9    |

| COM#            | 1       | K3    | BAD9#           | I/O     | J14  | D19             | I/O     | 89    |

| BSC9#           | I/O     | N1    | BAD8#           | I/O     | J13  | D18             | I/O     | C9    |

| BSC8#           | I/O     | Q1    | BAD7#           | I/O     | H15  | D17             | I/O     | A8    |

| BSC7#           | I/O     | P2    | BAD6#           | I/O     | H14  | D16             | I/O     | B8    |

| BSC6#           | I/O     | P1    | BAD5#           | I/O     | H13  | D15             | I/O     | C8    |

| BSC5#           | I/O     | N3    | BAD4#           | I/O     | G15  | D14             | I/O     | A7    |

| BSC4#           | I/O     | M3    | BAD3#           | I/O     | G14  | D13             | I/O     | B7    |

| ARB3#           | I/O, OC | P4    | V <sub>SS</sub> |         | N13  | D2              | I/O     | A2    |

| BSC3#           | I/O     | M2    | BAD2#           | I/O     | G13  | D12             | I/O     | A6    |

| BSC2#           | I/O     | M1    | BAD1#           | I/O     | F15  | D11             | I/O     | B6    |

| BSC1#           | I/O     | L3    | BAD0#           | I/O     | F14  | D10             | I/O     | C6    |

| BSC0#           | I/O     | L2    | BPAR2#          | I/O     | Q10  | D9              | I/O     | A5    |

| SCDIR1          | 0       | Q2    | BPAR1#          | I/O     | P10  | D8              | I/O     | B5    |

| SCDIR0          | 0       | N2    | BPAR0#          | I/O     | N10  | D7              | I/O     | A4    |

| V <sub>CC</sub> |         | M4    | V <sub>CC</sub> |         | N8   | D6              | I/O     | B4    |

| V <sub>SS</sub> |         | N4    | V <sub>SS</sub> |         | N9   | D5              | I/O     | C4    |

| ARB5#           | I/O, OC | N5    | V <sub>SS</sub> |         | N11  | D4              | I/O     | A3    |

| ARB4#           | I/O, OC | P5    | V <sub>CC</sub> |         | M12  | D3              | I/O     | B3    |

| ARB2#           | I/O, OC | Q4    | V <sub>SS</sub> |         | F13  | D1              | I/O     | B2    |

| ARB1#           | I/O, OC | P3    | V <sub>SS</sub> |         | K13  | D0              | I/O     | A1    |

| ARB0#           | I/O,OC  | Q3    | BBCLK           | 1       | Q8   | V <sub>CC</sub> |         | C7    |

| V <sub>SS</sub> | ,       | N6    | LACHn           | I       | P8   | V <sub>SS</sub> |         | D8    |

| BREQ#           | I/O, OC | P6    | RESET           | 1       | Q9   | V <sub>SS</sub> | 1       | C5    |

| TIMOUT          | I/O     | Q7    | RSTNC#          | I/O, OC | Q5   | BUSERR#         | I/O, OC | P7    |

| I IIVIOU I      |         |       |                 |         |      |                 |         |       |

$\textbf{NOTES:} I = input, \ O = output, \ I/O = input/output, \ OC \ a \ open-collector, \ ^* = active-low$

Figure 10. 149-Pin PGA Package Dimensions

# 7.0 MPC 82389 Electrical Data

This section provides detailed AC and DC specifications for the MPC 82389.

# 7.1 Maximum Ratings

| Parameter                       | Maximum Rating              |

|---------------------------------|-----------------------------|

| Operating Temperature Under Bia | s 0°C to + 70°C             |

| Storage Temperature             | − 65°C to + 150°C           |

| Voltage on any pin              | – 0.5 V to $V_{CC}$ + 0.5 V |

| Power Dissipation               | 2.5 W                       |

#### **†WARNING:**

Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only.

Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

# 7.2 DC Specifications

- $V_{CC} = 5.0V \pm 5\%$

- $TA = 0^{\circ}C$  to  $+70^{\circ}C$

### Table 6. DC Specifications

| Symbol           | Parameter                            | Min   | Max                   | Units | Test Conditions                       |

|------------------|--------------------------------------|-------|-----------------------|-------|---------------------------------------|

| $V_{IL}$         | Input Low Voltage                    | - 0.5 | 0.8                   | V     |                                       |

| V <sub>IH</sub>  | Input High Voltage                   | 2.0   | V <sub>CC</sub> + 0.5 | V     |                                       |

| V <sub>OL1</sub> | Output Low Voltage                   |       | 0.45                  | V     | I <sub>OL</sub> Max                   |

| V <sub>OL2</sub> | Output Low Voltage<br>Open Collector |       | 0.55                  | V     | I <sub>OL</sub> Max                   |

| V <sub>OH</sub>  | Output High Voltage                  | 2.4   |                       | V     | I <sub>OH</sub> Max                   |

| I <sub>CC</sub>  | Power Supply Current                 |       | 400                   | mA    |                                       |

| IL               | Input Leakage Current                |       | ± 10                  | μΑ    | $0V \le V_{IN} \le V_{CC}$            |

|                  | Open Collector                       |       | ± 100                 | μΑ    | $0.4V \le V_{IN} \le 2.4V$            |

| I <sub>L1</sub>  | Leakage Current                      |       | ± 400                 | μΑ    | $0V \le V_{IN} \le V_{CC}$            |

| I <sub>L2</sub>  | BBCLK Input Leakage<br>Current       |       | ± 100                 | μА    | $0V \le V_{IN} \le V_{CC}$            |

| I <sub>OL</sub>  | Output Low Current                   | 4.0   |                       | mA    | V <sub>OL</sub> = 0.45V               |

| I <sub>OL1</sub> | Open Collector Output<br>Low Current | 60.0  |                       | mA    | V <sub>OL</sub> = 0.55V               |

| I <sub>OL2</sub> | ADDIR and REFADR# Output Low Current | 8.0   |                       | mA    | V <sub>OL</sub> = 0.45V               |

| I <sub>OH</sub>  | Output High Current                  | - 1.0 |                       | mA    | V <sub>OH</sub> = 2.4V                |

| CI               | Input Capacitance                    |       | 10                    | pF    | f <sub>C</sub> = 1 MHz, 25°C (Note 1) |

| C <sub>IO</sub>  | I/O Capacitance                      |       | 20                    | pF    | f <sub>C</sub> = 1 MHz, 25°C (Note 1) |

| C <sub>CLK</sub> | Clock Input Capacitance              |       | 15                    | pF    | f <sub>C</sub> = 1 MHz, 25°C (Note 1) |

| C <sub>OC</sub>  | Open Collector<br>Capacitance        |       | 20                    | pF    | f <sub>C</sub> = 1 MHz, 25°C (Note 1) |

#### NOTES:

<sup>1.</sup> Sampled only, not 100% tested.

# 7.3 AC Specifications

The AC specifications for the MPC 82389 are specified in Table 7, Table 8 and Table 9; and Figure 12, Figure 13, Figure 14 and Figure 15. Figure 11 specifies the test points for measuring the AC parameters. Table 7, Figure 12 and Figure 13 specify the AC parameters for the host CPU bus. Figure 8 and Figure 14 specify the AC parameters for the interconnect bus. Table 9 and Figure 15 specify the AC parameters for the PSB. Figure 16 defines the test load for the AC specifications.

Table 7. Host CPU Bus AC Specifications ( $V_{CC} = 5V 15\%$ , TA = 0°C to + 70°C)

|                 |                                                           |          | 1   | ı        | 1                      |  |

|-----------------|-----------------------------------------------------------|----------|-----|----------|------------------------|--|

| Symbol          | Parameter                                                 |          | Max | Units    | Test Conditions        |  |

| t               | Address and BE# Setup to Command Active                   |          |     | ns       |                        |  |

| t <sub>1</sub>  | Select and DACK Setup to Command Active                   | 18       |     | ns       |                        |  |

| t <sub>2</sub>  | Address, BE#, Select and DACK<br>Hold from Command Active | 5        |     | ns       |                        |  |

| t <sub>3</sub>  | Time between Commands                                     | 24       |     | ns       |                        |  |

| t <sub>4</sub>  | Command Inactive to Read Data Disable (Note 5)            |          | 15  | ns       |                        |  |

| t <sub>5</sub>  | Read Data Hold from Command Inactive                      | 3        |     | ns       |                        |  |

| t <sub>6</sub>  | Read Data Enable from Command Active                      | 0        |     | ns       |                        |  |

| t <sub>7</sub>  | WAIT# Active from Command Active                          |          | 20  | ns       | C <sub>L</sub> = 50 pF |  |

| t <sub>8</sub>  | Command Inactive from WAIT# Inactive                      | 0        |     | ns       |                        |  |

| t <sub>9</sub>  | WAIT# Inactive to Read Data Valid                         |          | 25  | ns       | C <sub>L</sub> = 90 pF |  |

| t <sub>10</sub> | Command Active to Write Data Valid                        |          | 200 | ns       |                        |  |

| t <sub>11</sub> | Write Data Hold from WAIT# Inactive                       | 0        |     | ns       |                        |  |

| t <sub>12</sub> | Command Active to LOCK# Active (Note 1)                   |          | 100 | ns       |                        |  |

| t <sub>13</sub> | LOCK# Hold from WAIT# Inactive (Note 2)                   | 0        |     | ns       |                        |  |

| t <sub>14</sub> | Command Active Time                                       | 42       |     | ns       |                        |  |

| t <sub>15</sub> | Read Data Valid tram Command Active                       |          | 42  | ns       | CL = 90 pF             |  |

| t <sub>16</sub> | Write Data Setup to Command Inactive Registers DMA        | 20<br>20 |     | ns<br>ns |                        |  |

| t <sub>17</sub> | Write Data Hold from Command Inactive                     | 3        |     | ns       |                        |  |

| t <sub>18</sub> | Command Active to MINT or DREQ Inactive (Notes 3, 4)      |          | 42  | ns       | CL = 50 pF             |  |

| t <sub>19</sub> | Command Active to DREQ Inactive (Note 4)                  |          | 25  | ns       | CL = 50 pF             |  |

#### NOTES:

- 1. Required to guarantee locking of resource.

- 2. Required to guarantee resource remains lacked.

- 3. MINT deassertion only if no other sources are pending.

- For DREQ inactive timing, t<sub>19</sub> applies to a normal last transfer deassert condition and t<sub>18</sub> to an error deassert condition.

- $5. \ \ Disable \ condition \ occurs \ when \ the \ output \ current \ becomes \ less \ than \ the \ input \ leakage \ specification.$

Figure 11. AC Test Waveforms

Figure 12. Host CPU Interface Reference Operation Timing

Figure 13. Host CPU Interface Register and DMA Operation Timing

Table 8. Interconnect Bus AC Specifications (Vcc =  $5V \pm 5\%$ , TA =  $0^{\circ}$ C to  $\pm 70^{\circ}$ C)

| Symbol           | Parameter                                         | Min | Max | Units | Test Conditions |

|------------------|---------------------------------------------------|-----|-----|-------|-----------------|

| t <sub>31</sub>  | IAST Active Time                                  | 85  |     | ns    |                 |

| t <sub>32</sub>  | Command Active Time                               | 250 |     | ns    |                 |

| t <sub>33</sub>  | Command Inactive to IAST Active                   | 25  |     | ns    |                 |

| t <sub>33A</sub> | IAST Inactive to Command Active                   | 120 |     | ns    |                 |

| t <sub>34</sub>  | Address Setup to IAST Inactive                    | 40  |     | ns    |                 |

| t <sub>35</sub>  | Address Hold from IAST Inactive                   | 20  |     | ns    |                 |

| t <sub>36</sub>  | Write Data Setup to Command Inactive              | 120 |     | ns    |                 |

| t <sub>37</sub>  | Write Data Hold from Command Inactive             | 5   |     | ns    |                 |

| t <sub>38</sub>  | Read Data Enable from Command Active              | 0   |     | ns    |                 |

| t <sub>39</sub>  | Read Data Valid from Command Active               |     | 120 | ns    | CL = 150 pF     |

| t <sub>40</sub>  | Read Data Hold from Command Inactive              | 0   |     | ns    |                 |

| t <sub>41</sub>  | Read Data Disable from Command Inactive (Note 2)  |     | 30  | ns    |                 |

| t <sub>42</sub>  | EINT, IREQ# Inactive from Command Active (Note 1) |     | 100 | ns    | CL = 150 pF     |

#### NOTES:

- 1. EINT inactive orgy on write to error register. IREQ# inactive only on write to arbitration register.

- 2. Disable condition occurs when the output current becomes less than the input leakage specification.

Figure 14. Interconnect Bus Timing

Table 9. PSB Interface AC Specifications ( $Vcc = 5V \pm 5\%$ , TA = 0°C to + 70'C) (Sheet 1 of 2)

| Symbol           | Parameter                                                                                                                                                                                                          | Min   | Max                                                      | Units                                        | Test Conditions                                                                                                                            |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>CP</sub>  | Clock Period                                                                                                                                                                                                       | 99.9  |                                                          | ns                                           |                                                                                                                                            |

| t <sub>CL</sub>  | BCLK# Low Time (Note 1)                                                                                                                                                                                            | 40    |                                                          | ns                                           |                                                                                                                                            |

| t <sub>CH</sub>  | BCLK# High Time (Note 1)                                                                                                                                                                                           | 40    |                                                          | ns                                           |                                                                                                                                            |

| t <sub>BCL</sub> | BBCLK Low Time                                                                                                                                                                                                     | 38    |                                                          | ns                                           |                                                                                                                                            |

| t <sub>BCH</sub> | BBCLK High Time                                                                                                                                                                                                    | 38    |                                                          | ns                                           |                                                                                                                                            |

| t <sub>RB</sub>  | BCLK# Rise Time                                                                                                                                                                                                    | 1     | 5                                                        | ns                                           |                                                                                                                                            |

| t <sub>FB</sub>  | BCLK# Fall Time                                                                                                                                                                                                    | 1     | 2                                                        | ns                                           |                                                                                                                                            |

| t <sub>R</sub>   | BBCLK Rise Time                                                                                                                                                                                                    | 0.5   | 1                                                        | ns                                           |                                                                                                                                            |

| t <sub>F</sub>   | BBCLK Fall Time                                                                                                                                                                                                    | 0.5   | 1                                                        | ns                                           |                                                                                                                                            |