# Pentium® OverDrive® PROCESSOR WITH MMX™ TECHNOLOGY FOR Pentium PROCESSOR-BASED SYSTEMS

200-MHz Pentium® OverDrive® Processor with MMX<sup>™</sup> Technology to upgrade 100/133/166-MHz Pentium Processor-Based Systems

180-MHz Pentium OverDrive Processor with MMX Technology to upgrade 90/120/150-MHz Pentium Processor-Based Systems and upgrades 75-MHz Pentium Processor-Based Systems to 150-MHz

- Support for MMX<sup>TM</sup> Technology

- Powerful Processor Upgrades for Upgradable Pentium® Processor-Based Systems

- Superscalar Architecture

- Enhanced pipelines

- Two Pipelined Integer Units

Capable of 2 Instructions/Clock

- Pipelined MMX Unit

- Pipelined Floating-Point Unit

- Separate Code and Data Caches

- Deeper Write Buffers, "Pool" Configuration

- Enhanced Branch Prediction

- Virtual Mode Extensions

- 32-Bit CPU with 64-Bit Data Bus

- .35µM CMOS Silicon Technology

- On-package Voltage Regulation and Voltage Filtering

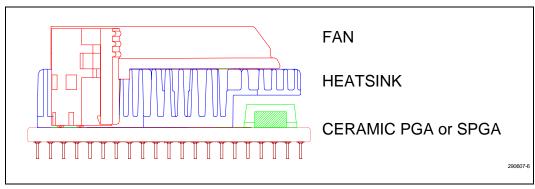

- Integrated Fan/Heatsink Thermal Solution

- Compatible with Installed Software

- MS-DOS\*, Windows\*, Windows 95, Windows NT, OS/2\*, UNIX\*

- Product Line Supports Socket 5 & Socket 7 Designs

- 320 pin SPGA Package

- Bus/Core Ratio, Hard-Bonded in 2/5 and 1/3 Modes

- Easy Installation

- Supports 50, 60, 66-MHz Bus Speeds

- Single 3.3 Volt Supply

The Pentium® OverDrive® processor with MMX™ technology is an end-user, single chip, Pentium processor upgrade product. The end user is able to add support for Intel's new MMX technology and increase the performance of their PC by simply replacing the existing 75, 90, 100, 120, 133, 150, and 166-MHz Pentium processor with a Pentium OverDrive processor with MMX technology. The Pentium OverDrive processor with MMX technology provides the performance needed for today's mainstream desktop applications and workstations. The Pentium OverDrive processor with MMX technology is binary compatible with the Pentium processor and compatible with the entire installed base of applications for MS-DOS\*, Windows\*, Windows 95, Windows NT, OS/2\*, and UNIX\*.

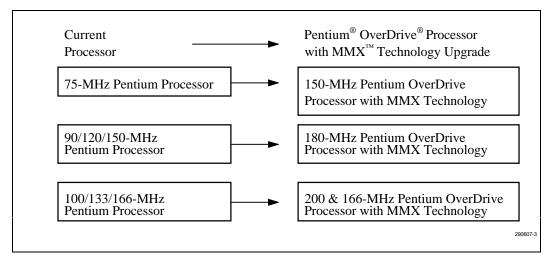

The 200-MHz Pentium OverDrive processor with MMX technology is designed to upgrade 100, 133, and 166-MHz Pentium processor-based systems. All most all of these systems use ZIF sockets that allow easy end user installation of the processor upgrade.

The 180/150-MHz Pentium OverDrive processor with MMX technology is designed to upgrade 75, 90, 120, and 150-MHz Pentium processor-based systems.

The 166-MHz Pentium OverDrive processor with MMX technology is designed to upgrade 100 and 133-MHz Pentium processor-based systems.

The Pentium OverDrive processor with MMX technology for Pentium processor-based systems has 4.5 million transistors and is built on Intel's advanced 0.35-micron silicon technology. The Pentium OverDrive processor with MMX technology is equipped with high reliability, integrated fan/heatsinks.

#### **Technical Product Notice**

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Pentium OverDrive processor with MMX technology may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 7641 Mt. Prospect IL 60056-7641

or call 1-800-879-4683 or visit Intel's website at http://www.intel.com

Copyright © Intel Corporation 1996, 1997.

\* Third-party brands and names are the property of their respective owners.

## **CONTENTS**

| PAGE                                                                                                                                                                                                |                                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0. INTRODUCTION       .5         1.1. Product Overview       .5         1.2. Product Description       .8         1.3. Purpose of this Document       .8         1.4. Compatibility Note       .8 | 3.7. On-Package Vo 3.8. Cache Support. 3.9. Code Prefetch C Buffers 3.10. I/O Buffers 3.11. Test Register /                                                                           |

| 2.0. PINOUT AND PIN DESCRIPTION8                                                                                                                                                                    | 4.0. BIOS AND SOFT                                                                                                                                                                    |

| 2.1. Pinout                                                                                                                                                                                         | 5.0. ELECTRICAL SP 5.1. Power and Grou 5.2. Decoupling Rec 5.3. Other Connectio 5.4. Absolute Maxim 5.5. D.C. Specificatio 5.6. A.C. Specificatio 5.6.1. A. C. TABL 5.6.2. A. C. TABL |

| 3.1. Core to Bus Ratio for Higher Speed27 3.2. Hardware Interface Differences27                                                                                                                     | 5.6.3. A. C. TABL<br>5.6.4. TIMING AN                                                                                                                                                 |

| 3.2.1. CPUTYP SIGNAL                                                                                                                                                                                | 6.0. MECHANICAL SF 6.1. Package Dimen 6.2. Spatial Requirer 6.3. Socket 6.3.1. SOCKET C 6.3.2. SOCKET 5 6.3.3. SOCKET 7                                                               |

| 3.4. Instruction Differences                                                                                                                                                                        | 7.0. THERMAL SPECI<br>8.0. TESTABILITY<br>8.1. Introduction<br>8.2. Built in Self Test<br>8.3. Tri-State Test M                                                                       |

|                                          | PAGE |

|------------------------------------------|------|

| 3.7. On-Package Voltage Regulator        | _    |

| 3.8. Cache Support                       |      |

| 3.9. Code Prefetch Queue and Branch Targ |      |

| Buffers                                  |      |

| 3.10. I/O Buffers                        |      |

| 3.11. Test Register Access               | 30   |

| 4.0. BIOS AND SOFTWARE                   | 31   |

| 5.0. ELECTRICAL SPECIFICATIONS           | 31   |

| 5.1. Power and Ground                    | 31   |

| 5.2. Decoupling Recommendations          | 31   |

| 5.3. Other Connection Recommendations    | 31   |

| 5.4. Absolute Maximum Ratings            | 31   |

| 5.5. D.C. Specifications                 | 33   |

| 5.6. A.C. Specifications                 | 34   |

| 5.6.1. A. C. TABLES FOR A 50-MHZ BU      | S34  |

| 5.6.2. A. C. TABLES FOR A 60-MHZ BU      | S38  |

| 5.6.3. A. C. TABLES FOR A 66-MHZ BU      | S42  |

| 5.6.4. TIMING AND WAVEFORMS              | 46   |

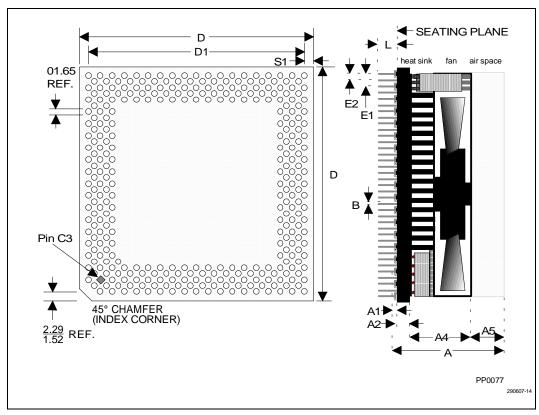

| 6.0. MECHANICAL SPECIFICATIONS           | 50   |

| 6.1. Package Dimensions                  | 50   |

| 6.2. Spatial Requirements                | 52   |

| 6.3. Socket                              | 53   |

| 6.3.1. SOCKET COMPATIBILITY              | 53   |

| 6.3.2. SOCKET 5 PINOUT                   | 53   |

| 6.3.3. SOCKET 7 PINOUT                   | 54   |

| 7.0. THERMAL SPECIFICATIONS              | 57   |

| 8.0. TESTABILITY                         | 57   |

| 8.1. Introduction                        | 57   |

| 8.2. Built in Self Test (BIST)           | 57   |

| 8.3. Tri-State Test Mode                 | 57   |

| FIGURES                  |                                                                                                                                                                                                                        | Figure 19.                                  |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

|                          | Pentium <sup>®</sup> OverDrive <sup>®</sup> Processor with MMX <sup>™</sup> Technology Block Diagram6                                                                                                                  | N<br>V                                      |

|                          | Pentium <sup>®</sup> OverDrive <sup>®</sup> Processor with MMX <sup>™</sup> Technology Key Features7                                                                                                                   |                                             |

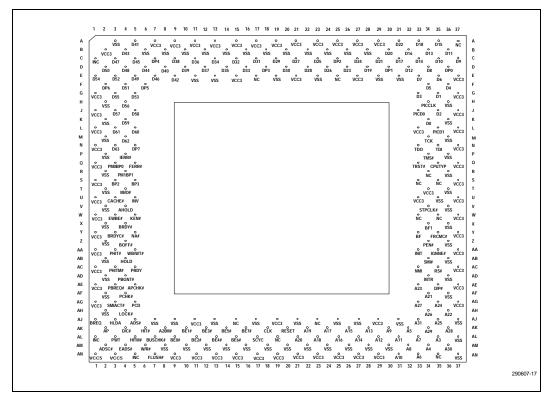

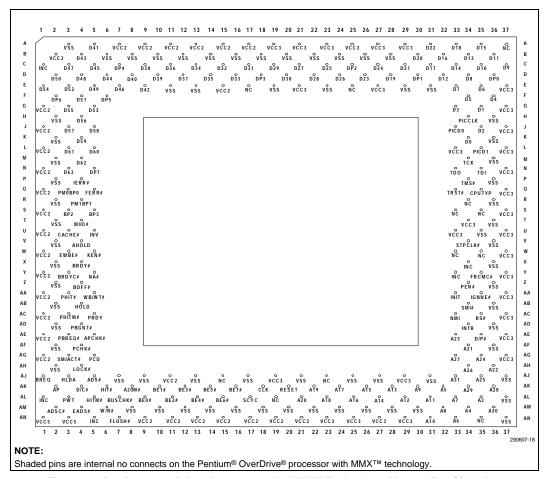

| Figure 4.                | Pentium <sup>®</sup> OverDrive <sup>®</sup> Processor with MMX <sup>™</sup> Technology Upgrade Choices .7 Pentium <sup>®</sup> OverDrive <sup>®</sup> Processor with MMX <sup>™</sup> Technology Pinout—Top Side View9 | TABLES Table 1. 32 by Table 2. Qu           |

| Ū                        | Pentium <sup>®</sup> OverDrive <sup>®</sup> Processor with<br>MMX™ Technology Pinout—Pin Side<br>View10                                                                                                                | Table 3. Inp<br>Table 4. Ou<br>Table 5. Inp |

|                          | Pentium <sup>®</sup> OverDrive <sup>®</sup> Processor with MMX™ Technology with Fan/Heatsink30                                                                                                                         | Table 6. Int<br>Table 7. Pir                |

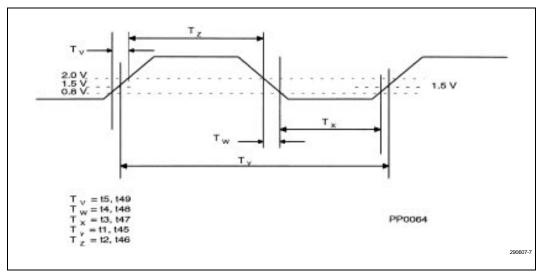

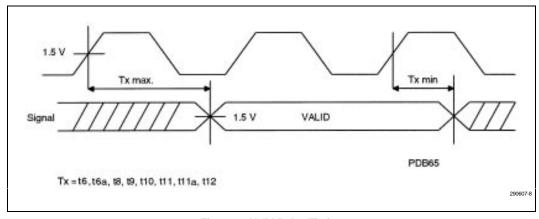

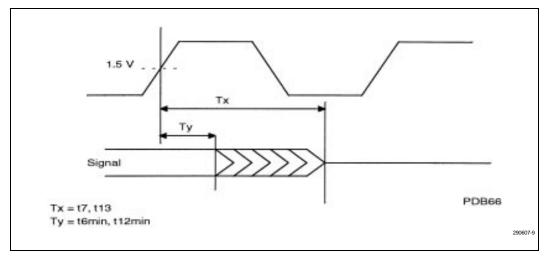

| Figure 8.                | Clock Waveform                                                                                                                                                                                                         | Table 8. Pir<br>by<br>wi                    |

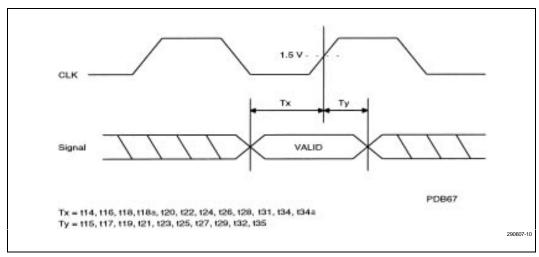

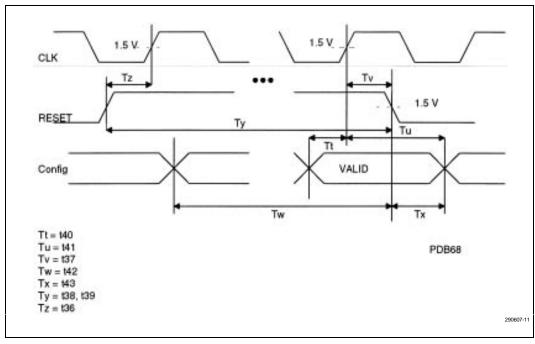

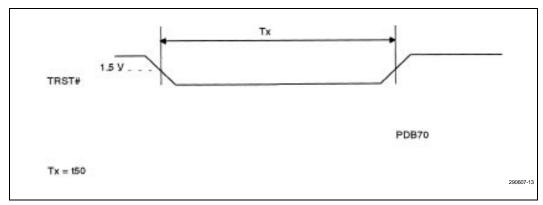

| Figure 10.<br>Figure 11. | Setup and Hold Timing47 Reset and Configuration Timing48                                                                                                                                                               | Table 9. Co<br>Table 10. E<br>Table 11. E   |

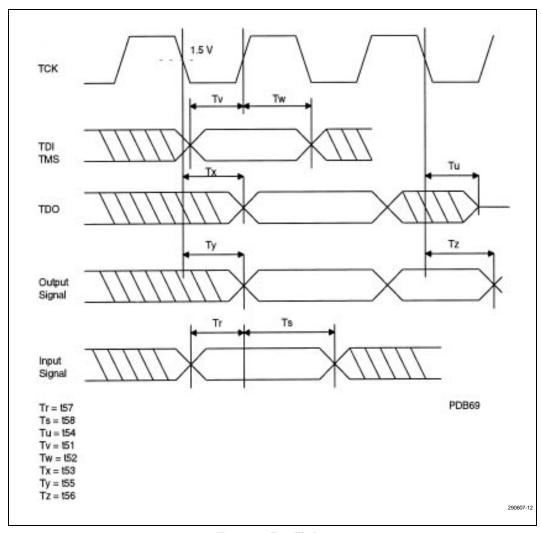

| Figure 13.<br>Figure 14. | Test Timing                                                                                                                                                                                                            | Ty<br>Table 12. A<br>Fa<br>Table 13. A      |

| Figure 15.               | Dimensions                                                                                                                                                                                                             | Table 14. 3 Table 15. 5 Table 16. 6         |

| Figure 16.               | Required Free Space from Sides of SPGA Package                                                                                                                                                                         | Table 16. 6<br>Table 17. 6<br>Table 18. F   |

| J                        | Pentium <sup>®</sup> OverDrive <sup>®</sup> Processor with<br>MMX <sup>™</sup> Technology Pinout—Top Side<br>View55                                                                                                    | Table 19. P                                 |

| Figure 19. Pentium <sup>®</sup> OverDrive <sup>®</sup> Processor with MMX <sup>™</sup> Technology Pinout—Pin Side                           |

|---------------------------------------------------------------------------------------------------------------------------------------------|

| View56                                                                                                                                      |

|                                                                                                                                             |

|                                                                                                                                             |

| ABLES                                                                                                                                       |

| Table 1. 320-Pin SPGA Pin Cross Reference by Pin Name11                                                                                     |

| Table 2. Quick Pin Reference14                                                                                                              |

| Table 3. Input Pins22                                                                                                                       |

| Table 4. Output Pins24                                                                                                                      |

| Table 5. Input/Output Pins25                                                                                                                |

| Table 6. Interprocessor I/O Pins25                                                                                                          |

| Table 7. Pin Functional Grouping26                                                                                                          |

| Table 8. Pin Functional Groupings Not Supported by Pentium <sup>®</sup> OverDrive <sup>®</sup> Processor with MMX <sup>™</sup> Technology27 |

| Table 9. Core/Bus Frequencies27                                                                                                             |

| Table 10. EAX Bit Values Definition for CPUID29                                                                                             |

| Table 11. EAX Bit Values Definition for Processor Type29                                                                                    |

| Table 12. Absolute Maximum Ratings without Fan/Heatsink32                                                                                   |

| Table 13. Absolute Maximum Ratings for Fan/Heatsink Only32                                                                                  |

| Table 14. 3.3V D.C. Specifications33                                                                                                        |

| Table 15. 50-MHz Bus A.C. Specifications34                                                                                                  |

| Table 16. 60-MHz Bus A.C. Specifications38                                                                                                  |

| Table 17. 66-MHz Bus A.C. Specifications42                                                                                                  |

| Table 18. Pentium <sup>®</sup> OverDrive <sup>®</sup> Processor with MMX <sup>™</sup> Technology Package Summary50                          |

| Table 19. Package Dimensions51                                                                                                              |

| Table 20. Design Considerations59                                                                                                           |

|                                                                                                                                             |

#### 1.0. INTRODUCTION

This datasheet describes Intel's Pentium OverDrive processor with MMX technology for upgradable Pentium processor-based systems. The Pentium OverDrive processor with MMX technology currently includes upgrades for 75, 90, 100, 120, 133, 150, and 166-MHz Pentium processors. Technical descriptions of other Pentium OverDrive processors are available in Intel OverDrive® Processors datasheet (Order #290436).

This datasheet is intended to be used in conjunction with the *Pentium® Family User's Manual* (Order #241428), which describes the Pentium family architecture and functionality. All enhancements or differences between the Pentium OverDrive processor with MMX technology and the original Pentium processor (i.e., 75/90/100/120/133/150/166-MHz Pentium processor vs. 200/180/166-MHz Pentium OverDrive processor with MMX technology) are described in this datasheet.

Pentium processor-based systems that are compatible with the Pentium OverDrive processor with MMX technology must be designed to both the original processor specifications and the Pentium OverDrive processor with MMX technology specifications.

#### 1.1. Product Overview

The Pentium OverDrive processor with MMX technology, for upgradable 75, 90, 100, 120, 150, and 166-MHz Pentium systems, allows users to upgrade to more advanced Pentium processor technology and adds Intel's new MMX technology.

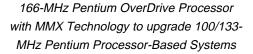

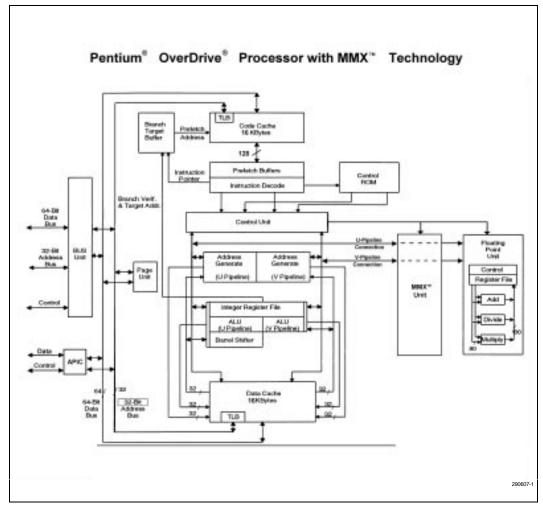

Figure 1 contains the block diagram of the Pentium OverDrive processor with MMX technology. Figure 2 lists some of the enhancements of the Pentium OverDrive processor with MMX technology. Figure 3 describes the upgrade choices available for an existing Pentium processor system.

Figure 1. Pentium<sup>®</sup> OverDrive<sup>®</sup> Processor with MMX™ Technology Block Diagram

- Based on Advanced Pentium<sup>®</sup> Processor with MMX<sup>™</sup> Technology

- Superscalar Architecture

- Pipelined Floating-Point Unit

- Separate 16K Code and 16K Data caches Bus Cycle Pipelining

- 64 Bit Data Bus

- Address Parity

- Virtual Mode Extensions

- System Management Mode

- Fractional Bus Operation

200, 180, and 166-MHz Pentium OverDrive® Processors with MMX Technology

- .35µM CMOS Silicon Technology

- Dynamic Branch prediction

- Improved Execution Time

- Writeback MESI Protocol in the Data Cache

- Internal Parity Checking

- Performance Monitoring

- Execution Tracing

- Active Fan/Heatsink

- For 75, 90, and 100-MHz Pentium Processor-Based Systems

- 320 Pin SPGA Pinout

- On-package Voltage Regulation

290607-2

Figure 2. Pentium® OverDrive® Processor with MMX™ Technology Key Features

Figure 3. Pentium® OverDrive® Processor with MMX™ Technology Upgrade Choices

#### 1.2. Product Description

The Pentium OverDrive processor with MMX technology comes in a 320-pin SPGA package and is a drop-in replacement for the 75, 90, 100, 120, 133, 150 and 166-MHz Pentium processor. It comes with on-package voltage regulation to provide the required 2.8 volts for the core and a fan/heatsink for a complete thermal solution. The internal core operates at 3.0 and 2.5 times the speed of the system bus for respective 200MHz and 166-MHz Pentium OverDrive processor with MMX technology. For dual socket systems the original processor must be removed and the Pentium OverDrive processor with MMX technology should be installed in the secondary socket since it does not support dual processing.

#### 1.3. Purpose of this Document

This document describes the system architecture and physical environment of Pentium OverDrive processor with MMX technology. It also outlines differences between the originally installed Pentium processor and the Pentium OverDrive processor with MMX technology.

#### 1.4. Compatibility Note

In this document some register bits are shown as "Intel Reserved" (RES) and some pins are marked as "No Connects" (NC) or "Reserved" (RES). When reserved bits are called out, treat them as fully undefined. This is essential for software compatibility with current and future processors. When a pin is marked as a "NC" or "RES" it is important to not connect any other signals to such pins to ensure proper operation. Intel strongly recommends following the guidelines below:

- Do not depend on the states of any undefined bits when testing the values of defined register. Mask them out when testing.

- Do not depend on the states of any undefined bits when storing them to memory or another register.

- Do not depend on the ability to retain information written into any undefined bits.

- When loading registers always load the undefined bits as zeros.

- Never connect signals to device pins marked "NC" or "RES".

- 6. INC pins are Internal No-Connects. This means that the pin is not connected to the processor internally. For example; the CPUTYP signal pin on the Pentium OverDrive processor with MMX technology is internally not connected to the package pin. The core is internally tied to V<sub>SS</sub>. The pin on the package is defined as INC. Any external connections to the package pin will not affect the processor core because the core is physically disconnected from the package pin.

#### 2.0. PINOUT AND PIN DESCRIPTION

#### 2.1. Pinout

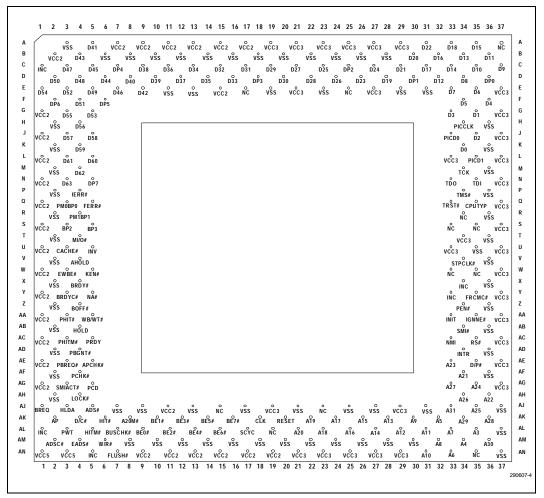

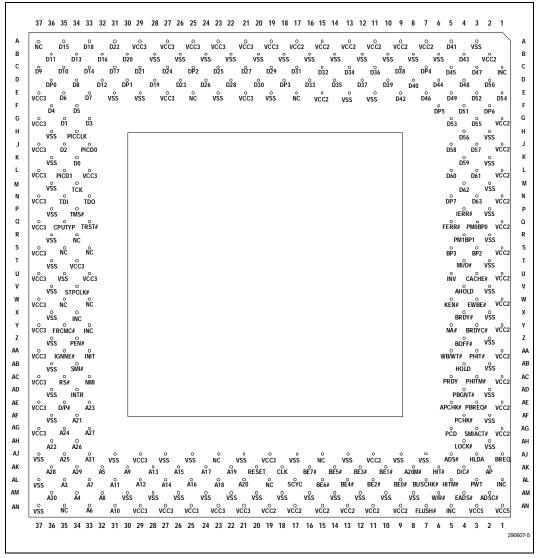

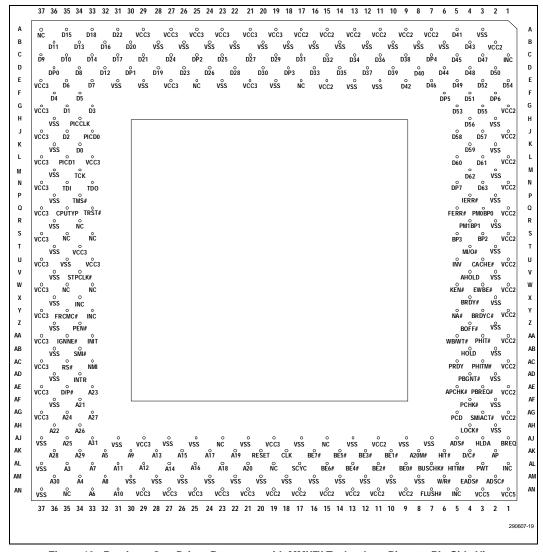

The Pentium OverDrive processor with MMX technology has a 320-pin SPGA pinout and is designed to be installed into Socket 5 or Socket 7. See Section 6.3 for more details on Socket 5 and Socket 7. Figure 4 and Figure 5 are illustrations of each side of the SPGA package.

Figure 4. Pentium® OverDrive® Processor with MMX™ Technology Pinout—Top Side View

PRELIMINARY

9

Figure 5. Pentium® OverDrive® Processor with MMX™ Technology Pinout—Pin Side View

#### 2.2. Pin Cross Reference

Table 1. 320-Pin SPGA Pin Cross Reference by Pin Name

|        | Address  |        |          |        |          |        |          |        |          |

|--------|----------|--------|----------|--------|----------|--------|----------|--------|----------|

| Signal | Location |

| А3     | AL35     | A9     | AK30     | A15    | AK26     | A21    | AF34     | A27    | AG33     |

| A4     | AM34     | A10    | AN31     | A16    | AL25     | A22    | AH36     | A28    | AK36     |

| A5     | AK32     | A11    | AL31     | A17    | AK24     | A23    | AE33     | A29    | AK34     |

| A6     | AN33     | A12    | AL29     | A18    | AL23     | A24    | AG35     | A30    | AM36     |

| A7     | AL33     | A13    | AK28     | A19    | AK22     | A25    | AJ35     | A31    | AJ33     |

| A8     | AM32     | A14    | AL27     | A20    | AL21     | A26    | AH34     |        |          |

|        |          |        |          | D      | ata      |        |          |        |          |

| Signal | Location |

| D0     | K34      | D13    | B34      | D26    | D24      | D39    | D10      | D52    | E03      |

| D1     | G35      | D14    | C33      | D27    | C21      | D40    | D08      | D53    | G05      |

| D2     | J35      | D15    | A35      | D28    | D22      | D41    | A05      | D54    | E01      |

| D3     | G33      | D16    | B32      | D29    | C19      | D42    | E09      | D55    | G03      |

| D4     | F36      | D17    | C31      | D30    | D20      | D43    | B04      | D56    | H04      |

| D5     | F34      | D18    | A33      | D31    | C17      | D44    | D06      | D57    | J03      |

| D6     | E35      | D19    | D28      | D32    | C15      | D45    | C05      | D58    | J05      |

| D7     | E33      | D20    | B30      | D33    | D16      | D46    | E07      | D59    | K04      |

| D8     | D34      | D21    | C29      | D34    | C13      | D47    | C03      | D60    | L05      |

| D9     | C37      | D22    | A31      | D35    | D14      | D48    | D04      | D61    | L03      |

| D10    | C35      | D23    | D26      | D36    | C11      | D49    | E05      | D62    | M04      |

| D11    | B36      | D24    | C27      | D37    | D12      | D50    | D02      | D63    | N03      |

| D12    | D32      | D25    | C23      | D38    | C09      | D51    | F04      | -      |          |

Table 1. 320-Pin SPGA Pin Cross Reference by Pin Name (Continued)

|        |          |       |            | Cor      | ntrol      |          |              |                |

|--------|----------|-------|------------|----------|------------|----------|--------------|----------------|

| Signal | Location | Signa | al         | Location | Signal     | Location | Signal       | Location       |

| A20M#  | AK08     | BRDY  | C#         | Y03      | FLUSH#     | AN07     | PEN#         | Z34            |

| ADS#   | AJ05     | BRE   | Q          | AJ01     | FRCMC#     | Y35      | PM0/BP0      | Q03            |

| ADSC#  | AM02     | BUSCH | łK#        | AL07     | HIT#       | AK06     | PM1/BP1      | R04            |

| AHOLD  | V04      | CACH  | E#         | U03      | HITM#      | AL05     | PRDY         | AC05           |

| AP     | AK02     | CPUTY | ′P**       | Q35      | HLDA       | AJ03     | PWT          | AL03           |

| APCHK# | AE05     | D/C#  | #          | AK04     | HOLD       | AB04     | R/S#         | AC35           |

| BE0#   | AL09     | D/P#  | <u>!</u> * | AE35     | IERR#      | P04      | RESET        | AK20           |

| BE1#   | AK10     | DPC   | )          | D36      | IGNNE#     | AA35     | SCYC         | AL17           |

| BE2#   | AL11     | DP1   | ]          | D30      | INIT       | AA33     | SMI#         | AB34           |

| BE3#   | AK12     | DP2   | 2          | C25      | INTR/LINT0 | AD34     | SMIACT#      | AG03           |

| BE4#   | AL13     | DP3   | 3          | D18      | INV        | U05      | TCK          | M34            |

| BE5#   | AK14     | DP4   | 1          | C07      | KEN#       | W05      | TDI          | N35            |

| BE6#   | AL15     | DP5   | 5          | F06      | LOCK#      | AH04     | TDO          | N33            |

| BE7#   | AK16     | DP6   | 6          | F02      | M/IO#      | T04      | TMS          | P34            |

| BOFF#  | Z04      | DP7   | 7          | N05      | NA#        | Y05      | TRST#        | Q33            |

| BP2    | S03      | EADS  | EADS# AM04 |          | NMI/LINT1  | AC33     | W/R#         | AM06           |

| BP3    | S05      | EWB   | EWBE# W03  |          | PCD        | AG05     | WB/WT#       | AA05           |

| BRDY#  | X04      | FERF  | R#         | Q05      | PCHK#      | AF04     |              |                |

|        | APIC     |       |            | Clock    | Control    | Dual P   | rocessor Pri | vate Interface |

| AP                | IC       | Clock ( | Control  | Dual Processor Private Interface |          |  |

|-------------------|----------|---------|----------|----------------------------------|----------|--|

| Signal            | Location | Signal  | Location | Signal                           | Location |  |

| PICCLK            | H34      | CLK     | AK18     | PBGNT#                           | AD04     |  |

| PICD0             | J33      | BF **   | Y33      | PBREQ#                           | AE03     |  |

| [DPEN#]           |          | BF1**   | X34      | PHIT#                            | AA03     |  |

| PICD1<br>[APICEN] | L35      | STPCLK# | V34      | PHITM#                           | AC03     |  |

#### NOTES:

The shaded pin definitions on the Pentium® OverDrive® processor with MMX™ technology are dual processing pins and are not supported by the Pentium OverDrive processor with MMX technology in Table 2.

<sup>•</sup> The D/P# signal in the 75, 90, 100, 120, 133, 150, and 166-MHz Pentium processor is always driven. Low indicates primary processor has the bus and high indicates the secondary processor is driving the bus. In the Pentium OverDrive processor with MMX technology this pin is defined internal no connect.

<sup>\*\*</sup> These signals are internally set and are not connected to the Pentium OverDrive processor with MMX technology pins. The pins are defined as Internal No-Connects.

Table 1. 320-Pin SPGA Pin Cross Reference by Pin Name (Continued)

|     | Vcc |     |     |             |     |      |        |      |                  |      |      |      |

|-----|-----|-----|-----|-------------|-----|------|--------|------|------------------|------|------|------|

| A07 | A19 | B02 | G37 |             | N01 | T    | 34 Y01 |      | 1 AE01           |      | AJ29 | AN19 |

| A09 | A21 | E15 | J01 |             | N37 | U    | 01     | Y37  | 7                | AE37 | AN09 | AN21 |

| A11 | A23 | E21 | J37 | (           | Q01 | U:   | 33     | AAO  | )1               | AG01 | AN11 | AN23 |

| A13 | A25 | E27 | L01 | (           | Q37 | U:   | 37     | AA3  | 37               | AG37 | AN13 | AN25 |

| A15 | A27 | E37 | L33 |             | S01 | W    | 01     | AC0  | )1               | AJ11 | AN15 | AN27 |

| A17 | A29 | G01 | L37 |             | S37 | W    | 37     | AC3  | 37               | AJ19 | AN17 | AN29 |

|     |     |     |     |             | V   | ss   |        |      |                  |      |      |      |

| A03 | B20 | E23 |     | <b>Л</b> 36 | ٧   | ′02  | P      | AD02 | AJ17             |      | AM10 | AM26 |

| B06 | B22 | E29 |     | P02         | ٧   | '36  | P      | AD36 |                  | AJ21 | AM12 | AM28 |

| B08 | B24 | E31 |     | P36 X0      |     | 02   | P      | AF02 | AJ25             |      | AM14 | AM30 |

| B10 | B26 | H02 |     | R02 X3      |     | 36   | P      | AF36 |                  | AJ27 | AM16 | AN37 |

| B12 | B28 | H36 |     | R36 Z02     |     | :02  | AH02   |      |                  | AJ31 | AM18 | AL01 |

| B14 | E11 | K02 |     | T02 Z       |     | Z36  |        | 4J07 |                  | AJ37 | AM20 |      |

| B16 | E13 | K36 |     | T36         |     | .B02 |        | 4J09 |                  | AL37 | AM22 |      |

| B18 | E19 | M02 |     | U35 AI      |     | AB36 |        | AJ13 |                  | AM08 | AM24 |      |

|     |     |     | N   | NC/INC      |     |      |        |      | V <sub>CC5</sub> |      |      |      |

| A37 | E25 | S33 | ,   | V33         | С   | :01  | A      | AJ23 |                  | AN35 |      | AN01 |

| E17 | R34 | S35 | ,   | V35         | A   | J15  | P      | AL19 |                  | AN05 |      | AN03 |

#### NOTE:

The shaded VCC/VSS/NC pins are new pin definitions (additions) on the Pentium® OverDrive® processor with MMX<sup>TM</sup> technology with the exception of A03 and B02.

#### 2.3. Quick Pin Reference

Table 2. Quick Pin Reference

| Symbol                 | Туре     | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A20M#                  | I        | When the <b>address bit 20 mask</b> pin is asserted, Pentium® OverDrive® processor with MMX <sup>TM</sup> technology emulates the address wraparound at 1 Mbyte which occurs on the 8086. When A20M# is asserted, the Pentium OverDrive processor with MMX technology masks physical address bit 20 (A20) before performing a lookup to the internal caches or driving a memory cycle on the bus. The effect of A20M# is undefined in protected mode. A20M# must be asserted only when the processor is in real mode. |

| A31-A3                 | I/O      | As outputs, the address lines of the processor along with the byte enables define the physical area of memory or I/O accessed. The external system drives the inquire address to the processor on A31-A3.                                                                                                                                                                                                                                                                                                             |

| ADS#                   | 0        | The address status indicates that a new valid bus cycle is currently being driven by the Pentium OverDrive processor with MMX technology.                                                                                                                                                                                                                                                                                                                                                                             |

| ADSC#                  | 0        | ADSC# is functionally identical to ADS#.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| AHOLD                  | I        | In response to the assertion of address hold, Pentium OverDrive processor with MMX technology will stop driving the address lines (A31-A3), and AP in the next clock. The rest of the bus will remain active so data can be returned or driven for previously issued bus cycles.                                                                                                                                                                                                                                      |

| АР                     | I/O      | Address parity is driven by the Pentium OverDrive processor with MMX technology with even parity information on all the Pentium OverDrive processor with MMX technology generated cycles in the same clock that the address is driven. Even parity must be driven back to the Pentium OverDrive processor with MMX technology during inquire cycles on this pin in the same clock as EADS# to ensure that correct parity check status is indicated by the Pentium OverDrive processor with MMX technology             |

| APCHK#                 | 0        | The address parity check status pin is asserted two clocks after EADS# is sampled active if the Pentium OverDrive processor with MMX technology has detected a parity error on the address bus during inquire cycles. APCHK# will remain active for one clock each time a parity error is detected (including during dual processing private snooping).                                                                                                                                                               |

| [APICEN]<br>PICD1      | I        | The APIC is not supported by the Pentium OverDrive processor with MMX technology.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| BE7#-BE5#<br>BE4#-BE0# | O<br>I/O | The <b>byte enable</b> pins are used to determine which bytes must be written to external memory, or which bytes were requested by the CPU for the current cycle. The byte enables are driven in the same clock as the address lines (A31-3).                                                                                                                                                                                                                                                                         |

| [BF]                   | I        | <b>Bus Frequency</b> determines the bus-to-core frequency ratio on the Pentium processor. These are Internal No Connects on the Pentium OverDrive processor with MMX technology which has a preset bus fraction of 5/2 for 166-MHz OverDrive Processor and 3/1 for 200-MHz OverDrive Processor core/bus ratio.                                                                                                                                                                                                        |

Table 2. Quick Pin Reference (Continued)

| Symbol                | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BOFF#                 | I    | The backoff input is used to abort all outstanding bus cycles that have not yet completed. In response to BOFF#, the Pentium OverDrive processor with MMX technology will float all pins normally floated during bus hold in the next clock. The processor remains in bus hold until BOFF# is negated, at which time Pentium OverDrive processor with MMX technology restarts the aborted bus cycle(s) in their entirety.                                               |

| BP[3:2]<br>PM/BP[1:0] | 0    | The breakpoint pins (BP3-0) correspond to the debug registers, DR3-DR0. These pins externally indicate a breakpoint match when the debug registers are programmed to test for breakpoint matches.                                                                                                                                                                                                                                                                       |

|                       |      | BP1 and BP0 are multiplexed with the performance monitoring pins (PM1 and PM0). The PB1 and PB0 bits in the Debug Mode Control Register determine if the pins are configured as breakpoint or performance monitoring pins. The pins come out of RESET configured for performance monitoring.                                                                                                                                                                            |

| BRDY#                 | I    | The burst ready input indicates that the external system has presented valid data on the data pins in response to a read or that the external system has accepted the Pentium OverDrive processor with MMX technology data in response to a write request. This signal is sampled in the T2, T12 and T2P bus states.                                                                                                                                                    |

| BRDYC#                | I    | This signal has the same functionality as BRDY#.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| BREQ                  | 0    | The bus request output indicates to the external system that Pentium OverDrive processor with MMX technology has internally generated a bus request. This signal is always driven whether or not the Pentium OverDrive processor with MMX technology is driving its bus.                                                                                                                                                                                                |

| BUSCHK#               | I    | The <b>bus check</b> input allows the system to signal an unsuccessful completion of a bus cycle. If this pin is sampled active, Pentium OverDrive processor with MMX technology will latch the address and control signals in the machine check registers. If, in addition, the MCE bit in CR4 is set, the Pentium OverDrive processor with MMX technology will vector to the machine check exception.                                                                 |

| CACHE#                | 0    | For Pentium OverDrive processor with MMX technology-initiated cycles the cache pin indicates internal cacheability of the cycle (if a read), and indicates a burst writeback cycle (if a write). If this pin is driven inactive during a read cycle, Pentium OverDrive processor with MMX technology will not cache the returned data, regardless of the state of the KEN# pin. This pin is also used to determine the cycle length (number of transfers in the cycle). |

| CLK                   | ı    | The clock input provides the fundamental timing for Pentium OverDrive processor with MMX technology. The clock frequency is the operating frequency of the Pentium OverDrive processor with MMX technology external bus and requires TTL levels. All external timing parameters except TDI, TDO, TMS, TRST#, and PICD0-1 are specified with respect to the rising edge of CLK.                                                                                          |

| CPUTYP                | I    | CPUTYP is internally tied to ground and is a Internal No-Connect (INC) to the package pin on the Pentium OverDrive processor with MMX technology.                                                                                                                                                                                                                                                                                                                       |

Table 2. Quick Pin Reference (Continued)

| Symbol  | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D/C#    | 0    | The data/code output is one of the primary bus cycle definition pins. It is driven valid in the same clock as the ADS# signal is asserted. D/C# distinguishes between data and code or special cycles.                                                                                                                                                                                                                                                                                                                                                    |

| D/P#    | 0    | The Pentium OverDrive processor with MMX technology does not support dual processing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| D63-D0  | I/O  | These are the 64 data lines for the processor. Lines D7-D0 define the least significant byte of the data bus; lines D63-D56 define the most significant byte of the data bus. When the CPU is driving the data lines, they are driven during the T2, T12, or T2P clocks for that cycle. During reads, the CPU samples the data bus when BRDY# is returned.                                                                                                                                                                                                |

| DP7-DP0 | I/O  | These are the data parity pins for the processor. There is one for each byte of the data bus. They are driven by Pentium OverDrive processor with MMX technology with even parity information on writes in the same clock as write data. Even parity information must be driven back to the Pentium OverDrive processor with MMX technology on these pins in the same clock as the data to ensure that the correct parity check status is indicated by the Pentium OverDrive processor with MMX technology. DP7 applies to D63-D56, DP0 applies to D7-D0. |

| [DPEN#] | I/O  | The Pentium OverDrive processor with MMX technology does not support dual                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PICD0   |      | processing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| EADS#   | I    | This signal indicates that a valid external address has been driven onto the Pentium OverDrive processor with MMX technology address pins to be used for an inquire cycle.                                                                                                                                                                                                                                                                                                                                                                                |

| EWBE#   | I    | The external write buffer empty input, when inactive (high), indicates that a write cycle is pending in the external system. When Pentium OverDrive processor with MMX technology generates a write, and EWBE# is sampled inactive, the Pentium OverDrive processor with MMX technology will hold off all subsequent writes to all E- or M-state lines in the data cache until all write cycles have completed, as indicated by EWBE# being active.                                                                                                       |

| FERR#   | 0    | The floating-point error pin is driven active when an unmasked floating-point error occurs. FERR# is similar to the ERROR# pin on the Intel387™ math coprocessor. FERR# is included for compatibility with systems using DOS-type floating-point error reporting.                                                                                                                                                                                                                                                                                         |

| FLUSH#  | I    | When asserted, the cache flush input forces the Pentium OverDrive processor with MMX technology to writeback all modified lines in the data cache and invalidate its internal caches. A Flush Acknowledge special cycle will be generated by the Pentium OverDrive processor with MMX technology indicating completion of the writeback and invalidation.                                                                                                                                                                                                 |

|         |      | If FLUSH# is sampled low when RESET transitions from high to low, tristate test mode is entered.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| FRCMC#  | I    | The Pentium OverDrive processor with MMX technology does not support functional redundancy checking.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Table 2. Quick Pin Reference (Continued)

| Symbol | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HIT#   | 0    | The hit indication is driven to reflect the outcome of an inquire cycle. If an inquire cycle hits a valid line in either Pentium OverDrive processor with MMX technology data or instruction cache, this pin is asserted two clocks after EADS# is sampled asserted. If the inquire cycle misses the Pentium OverDrive processor with MMX technology cache, this pin is negated two clocks after EADS#. This pin changes its value only as a result of an inquire cycle and retains its value between the cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| HITM#  | 0    | The hit to a modified line output is driven to reflect the outcome of an inquire cycle. It is asserted after inquire cycles which resulted in a hit to a modified line in the data cache. It is used to inhibit another bus master from accessing the data until the line is completely written back.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| HLDA   | 0    | The bus hold acknowledge pin goes active in response to a hold request driven to the processor on the HOLD pin. It indicates that Pentium OverDrive processor with MMX technology has floated most of the output pins and relinquished the bus to another local bus master. When leaving bus hold, HLDA will be driven inactive and Pentium OverDrive processor with MMX technology will resume driving the bus. If the Pentium OverDrive processor with MMX technology has a bus cycle pending, it will be driven in the same clock that HLDA is de-asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| HOLD   | I    | In response to the bus hold request, Pentium OverDrive processor with MMX technology will float most of its output and input/output pins and assert HLDA after completing all outstanding bus cycles. The Pentium OverDrive processor with MMX technology will maintain its bus in this state until HOLD is deasserted. HOLD is not recognized during LOCK cycles. The Pentium OverDrive processor with MMX technology will recognize HOLD during reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| IERR#  | 0    | The internal error pin is used to indicate internal parity errors. If a parity error occurs on a read from an internal array, the Pentium OverDrive processor with MMX technology will assert the IERR# pin for one clock and then shutdown.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| IGNNE# |      | This is the ignore numeric error input. This pin has no effect when the NE bit in CR0 is set to 1. When the CR0.NE bit is 0, and the IGNNE# pin is asserted, the Pentium OverDrive processor with MMX technology will ignore any pending unmasked numeric exception and continue executing floating-point instructions for the entire duration that this pin is asserted. When the CR0.NE bit is 0, IGNNE# is not asserted, a pending unmasked numeric exception exists (SW.ES = 1), and the floating-point instruction is one of FINIT, FCLEX, FSTENV, FSAVE, FSTSW, FSTCW, FENI, FDISI, or FSETPM, the Pentium OverDrive processor with MMX technology will execute the instruction in spite of the pending exception. When the CR0.NE bit is 0, IGNNE# is not asserted, a pending unmasked numeric exception exists (SW.ES = 1), and the floating-point instruction is one other than FINIT, FCLEX, FSTENV, FSAVE, FSTSW, FSTCW, FENI, FDISI, or FSETPM, the Pentium OverDrive processor with MMX technology will stop execution and wait for an external interrupt. |

Table 2. Quick Pin Reference (Continued)

| Symbol     | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INIT       | I    | The Pentium OverDrive processor with MMX technology <b>initialization</b> input pin forces the Pentium OverDrive processor with MMX technology to begin execution in a known state. The processor state after INIT is the same as the state after RESET except that the internal caches, write buffers, and floating-point registers retain the values they had prior to INIT. INIT may NOT be used in lieu of RESET after power up.                                         |

|            |      | If INIT is sampled high when RESET transitions from high to low, the Pentium OverDrive processor with MMX technology will perform built-in self test prior to the start of program execution.                                                                                                                                                                                                                                                                                |

| INTR/LINT0 | I    | An active maskable interrupt input indicates that an external interrupt has been generated. If the IF bit in the EFLAGS register is set, the Pentium OverDrive processor with MMX technology will generate two locked interrupt acknowledge bus cycles and vector to an interrupt handler after the current instruction execution is completed. INTR must remain active until the first interrupt acknowledge cycle is generated to assure that the interrupt is recognized. |

| INV        | I    | The invalidation input determines the final cache line state (S or I) in case of an inquire cycle hit. It is sampled together with the address for the inquire cycle in the clock EADS# is sampled active.                                                                                                                                                                                                                                                                   |

| KEN#       | I    | The cache enable pin is used to determine whether the current cycle is cacheable or not and is consequently used to determine cycle length. When the Pentium OverDrive processor with MMX technology generates a cycle that can be cached (CACHE# asserted) and KEN# is active, the cycle will be transformed into a burst line fill cycle.                                                                                                                                  |

| LOCK#      | 0    | The bus lock pin indicates that the current bus cycle is locked. Pentium OverDrive processor with MMX technology will not allow a bus hold when LOCK# is asserted (but AHOLD and BOFF# are allowed). LOCK# goes active in the first clock of the first locked bus cycle and goes inactive after the BRDY# is returned for the last locked bus cycle. LOCK# is guaranteed to be deasserted for at least one clock between back to back locked cycles.                         |

| M/IO#      | 0    | The memory/input-output is one of the primary bus cycle definition pins. It is driven valid in the same clock as the ADS# signal is asserted. M/IO# distinguishes between memory and I/O cycles.                                                                                                                                                                                                                                                                             |

| NA#        | I    | An active next address input indicates that the external memory system is ready to accept a new bus cycle although all data transfers for the current cycle have not yet completed. The Pentium OverDrive processor with MMX technology will issue ADS# for a pending cycle two clocks after NA# is asserted. The Pentium OverDrive processor with MMX technology supports up to 2 outstanding bus cycles.                                                                   |

| NMI/LINT1  | I    | The non-maskable interrupt request signal indicates that an external non-maskable interrupt has been generated.                                                                                                                                                                                                                                                                                                                                                              |

| PBGNT#     | I/O  | The Pentium OverDrive processor with MMX technology does not support dual processing.                                                                                                                                                                                                                                                                                                                                                                                        |

Table 2. Quick Pin Reference

| Symbol                         | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCD                            | 0    | The page cache disable pin reflects the state of the PCD bit in CR3, the Page Directory Entry, or the Page Table Entry. The purpose of PCD is to provide an external cacheability indication on a page by page basis.                                                                                                                                                                                                                                                                                                                                                                                                      |

| PCHK#                          | 0    | The parity check output indicates the result of a parity check on a data read. It is driven with parity status two clocks after BRDY# is returned. PCHK# remains low one clock for each clock in which a parity error was detected. Parity is checked only for the bytes on which valid data is returned.                                                                                                                                                                                                                                                                                                                  |

| PEN#                           | I    | The parity enable input (along with CR4.MCE) determines whether a machine check exception will be taken as a result of a data parity error on a read cycle. If this pin is sampled active in the clock a data parity error is detected, the Pentium OverDrive processor with MMX technology will latch the address and control signals of the cycle with the parity error in the machine check registers. If, in addition, the machine check enable bit in CR4 is set to "1", the Pentium OverDrive processor with MMX technology will vector to the machine check exception before the beginning of the next instruction. |

| PHIT#                          | I/O  | The Pentium OverDrive processor with MMX technology does not support dual processing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PHITM#                         | I/O  | The Pentium OverDrive processor with MMX technology does not support dual processing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PICCLK                         | 1    | The Pentium OverDrive processor with MMX technology does not support dual processing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PICD0-1<br>[DPEN#]<br>[APICEN] | I/O  | The Pentium OverDrive processor with MMX technology does not support dual processing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PBREQ#                         | I/O  | The Pentium OverDrive processor with MMX technology does not support dual processing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PM/BP[1:0]                     | 0    | These pins function as part of the performance monitoring feature.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                |      | The breakpoint 1-0 pins are multiplexed with the <b>performance monitoring 1-0</b> pins. The PB1 and PB0 bits in the Debug Mode Control Register determine if the pins are configured as breakpoint or performance monitoring pins. The pins come out of RESET configured for performance monitoring.                                                                                                                                                                                                                                                                                                                      |

| PRDY                           | 0    | The probe ready output pin indicates that the processor has stopped normal execution in response to the R/S# pin going active, or Probe Mode being entered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PWT                            | 0    | The page write through pin reflects the state of the PWT bit in CR3, the Page Directory Entry, or the Page Table Entry. The PWT pin is used to provide an external writeback indication on a page by page basis.                                                                                                                                                                                                                                                                                                                                                                                                           |

| R/S#                           | I    | The run / stop input is an asynchronous, edge sensitive interrupt used to stop the normal execution of the processor and place it into an idle state. A high to low transition on the R/S# pin will interrupt the processor and cause it to stop execution at the next instruction boundary.                                                                                                                                                                                                                                                                                                                               |

Table 2. Quick Pin Reference

| Symbol           | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET            | I    | RESET forces the Pentium OverDrive processor with MMX technology to begin execution at a known state. All Pentium OverDrive processor internal caches will be invalidated upon the RESET. Modified lines in the data cache are not written back. FLUSH#, and INIT are sampled when RESET transitions from high to low to determine if tristate test mode mode will be entered, or if BIST will be run.                                                                                                                          |

| SCYC             | 0    | The <b>split cycle</b> output is asserted during misaligned LOCKed transfers to indicate that more than two cycles will be locked together. This signal is defined for locked cycles only. It is undefined for cycles which are not locked.                                                                                                                                                                                                                                                                                     |