# MIPS32® Architecture for Programmers VolumeIV-e: The MIPS® DSP Application-Specific Extension to the MIPS32® Architecture

Document Number: MD00374 Revision 1.00 July 6 2005

MIPS Technologies, Inc. 1225 Charleston Road Mountain View, CA 94043-1353

Copyright © 2004-2005 MIPS Technologies Inc. All rights reserved.

Copyright © 2004-2005 MIPS Technologies, Inc. All rights reserved.

Unpublished rights (if any) reserved under the copyright laws of the United States of America and other countries.

This document contains information that is proprietary to MIPS Technologies, Inc. ("MIPS Technologies"). Any copying, reproducing, modifying or use of this information (in whole or in part) that is not expressly permitted in writing by MIPS Technologies or an authorized third party is strictly prohibited. At a minimum, this information is protected under unfair competition and copyright laws. Violations thereof may result in criminal penalties and fines.

Any document provided in source format (i.e., in a modifiable form such as in FrameMaker or Microsoft Word format) is subject to use and distribution restrictions that are independent of and supplemental to any and all confidentiality restrictions. UNDER NO CIRCUMSTANCES MAY A DOCUMENT PROVIDED IN SOURCE FORMAT BE DISTRIBUTED TO A THIRD PARTY IN SOURCE FORMAT WITHOUT THE EXPRESS WRITTEN PERMISSION OF MIPS TECHNOLOGIES, INC.

MIPS Technologies reserves the right to change the information contained in this document to improve function, design or otherwise. MIPS Technologies does not assume any liability arising out of the application or use of this information, or of any error or omission in such information. Any warranties, whether express, statutory, implied or otherwise, including but not limited to the implied warranties of merchantability or fitness for a particular purpose, are excluded. Except as expressly provided in any written license agreement from MIPS Technologies or an authorized third party, the furnishing of this document does not give recipient any license to any intellectual property rights, including any patent rights, that cover the information in this document.

The information contained in this document shall not be exported, reexported, transferred, or released, directly or indirectly, in violation of the law of any country or international law, regulation, treaty, Executive Order, statute, amendments or supplements thereto. Should a conflict arise regarding the export, reexport, transfer, or release of the information contained in this document, the laws of the United States of America shall be the governing law.

The information contained in this document constitutes one or more of the following: commercial computer software, commercial computer software documentation or other commercial items. If the user of this information, or any related documentation of any kind, including related technical data or manuals, is an agency, department, or other entity of the United States government ("Government"), the use, duplication, reproduction, release, modification, disclosure, or transfer of this information, or any related documentation of any kind, is restricted in accordance with Federal Acquisition Regulation 12.212 for civilian agencies and Defense Federal Acquisition Regulation Supplement 227.7202 for military agencies. The use of this information by the Government is further restricted in accordance with the terms of the license agreement(s) and/or applicable contract terms and conditions covering this information from MIPS Technologies or an authorized third party.

MIPS, MIPS I, MIPS II, MIPS II, MIPS IV, MIPS V, MIPS-3D, MIPS16, MIPS16e, MIPS32, MIPS64, MIPS-Based, MIPSsim, MIPSpro, MIPS Technologies logo, MIPS RISC CERTIFIED POWER logo, 4K, 4Kc, 4Km, 4Kp, 4KE, 4KEc, 4KEm, 4KEp, 4KS, 4KSc, 4KSd, M4K, 5K, 5Kc, 5Kf, 20Kc, 24K, 24Kc, 24Kf, 24KE, 24KEc, 24KEf, 25Kf, 34K, R3000, R4000, R5000, ASMACRO, Atlas, "At the core of the user experience.", BusBridge, CorExtend, CoreFPGA, CoreLV, EC, FastMIPS, JALGO, Malta, MDMX, MGB, PDtrace, the Pipeline, Pro Series, QuickMIPS, SEAD, SEAD-2, SmartMIPS, SOC-it, and YAMON are trademarks or registered trademarks of MIPS Technologies, Inc. in the United States and other countries.

All other trademarks referred to herein are the property of their respective owners.

Template: B1.14, Built with tags: 2B ARCH MIPS32

# Table of Contents

| Chapter 1 About This Book                                                          | 1  |

|------------------------------------------------------------------------------------|----|

| 1.1 Typographical Conventions                                                      |    |

| 1.1.1 Italic Text                                                                  |    |

| 1.1.2 Bold Text                                                                    |    |

| 1.1.3 Courier Text                                                                 |    |

| 1.2 UNPREDICTABLE and UNDEFINED                                                    |    |

| 1.2.1 UNPREDICTABLE                                                                |    |

| 1.2.2 UNDEFINED                                                                    |    |

| 1.2.3 UNSTABLE                                                                     |    |

| 1.3 Special Symbols in Pseudocode Notation                                         |    |

| 1.4 For More Information                                                           |    |

| Chapter 2 Guide to the Instruction Set                                             |    |

| 2.1 Understanding the Instruction Fields                                           |    |

| 2.1.1 Instruction Fields                                                           |    |

| 2.1.2 Instruction Descriptive Name and Mnemonic                                    | 9  |

| 2.1.3 Format Field                                                                 | 9  |

| 2.1.4 Purpose Field                                                                |    |

| 2.1.5 Description Field                                                            |    |

| 2.1.6 Restrictions Field                                                           |    |

| 2.1.7 Operation Field                                                              | 11 |

| 2.1.8 Exceptions Field                                                             | 11 |

| 2.1.9 Programming Notes and Implementation Notes Fields                            | 11 |

| 2.2 Operation Section Notation and Functions                                       |    |

| 2.2.1 Instruction Execution Ordering                                               |    |

| 2.2.2 Pseudocode Functions                                                         |    |

| Coprocessor General Register Access Functions 12                                   |    |

| Memory Operation Functions 14                                                      |    |

| Floating Point Functions 17                                                        |    |

| Miscellaneous Functions 20                                                         |    |

| 2.3 Op and Function Subfield Notation                                              |    |

| 2.4 FPU Instructions                                                               |    |

| Chapter 3 The MIPS® DSP Application Specific Extension to the MIPS32® Architecture |    |

| 3.1 Base Architecture Requirements                                                 |    |

| 3.2 Software Detection of the ASE                                                  |    |

| 3.3 Compliance and Subsetting                                                      |    |

| 3.4 Introduction to the MIPS® DSP ASE                                              |    |

| 3.5 DSP Applications and their Requirements                                        |    |

| 3.6 Fixed-Point Data Type                                                          |    |

| 3.7 Saturating Math                                                                |    |

| 3.8 Conventions Used in the Instruction Mnemonics                                  |    |

| 3.9 Effect of Endian-ness on Register SIMD Data                                    |    |

| 3.10 Additional Register State for the DSP ASE                                     |    |

| 3.11 Software Detection of the DSP ASE                                             |    |

| 3.12 Exception Table for the DSP ASE                                               |    |

| 3.13 DSP ASE Instructions that Read and Write the DSPControl Register              |    |

| 3.14 Arithmetic Exceptions                                                         |    |

| Chapter 4 MIPS® DSP ASE Instruction Summary                                        |    |

| 4.1 The MIPS® DSP ASE Instruction Summary                                          |    |

| Chapter 5 Instruction Encoding              |  |

|---------------------------------------------|--|

| 5.1 Instruction Bit Encoding                |  |

| ·                                           |  |

| Chapter 6 The MIPS® DSP ASE Instruction Set |  |

| 6.1 Compliance and Subsetting               |  |

| ABSQ_S.PH                                   |  |

| ABSQ_S.W                                    |  |

| ADDQ_S.W                                    |  |

| ADDQ[_S].PH                                 |  |

| ADDSC                                       |  |

| ADDU[_S].QB                                 |  |

| ADDWC                                       |  |

| BITREV                                      |  |

| BPOSGE32                                    |  |

| CMP.cond.PH                                 |  |

| CMPGU.cond.QB                               |  |

| CMPU.cond.QB                                |  |

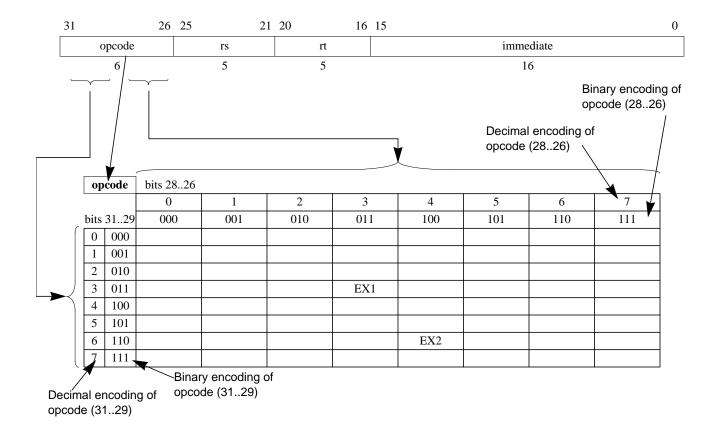

| DPAQ_S.W.PH                                 |  |

| DPAQ_SA.L.W                                 |  |

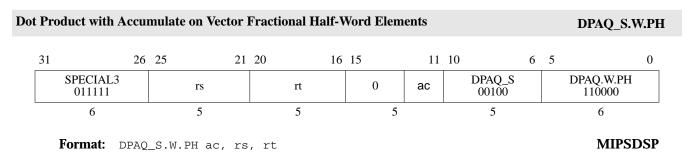

| DPAU.H.QBL                                  |  |

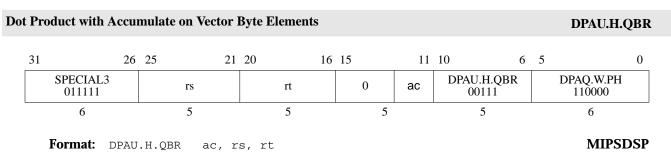

| DPAU.H.QBR                                  |  |

| DPSQ_SA.L.W                                 |  |

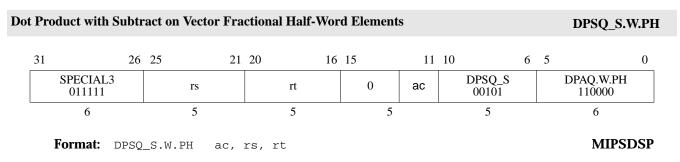

| DPSQ_S.W.PH                                 |  |

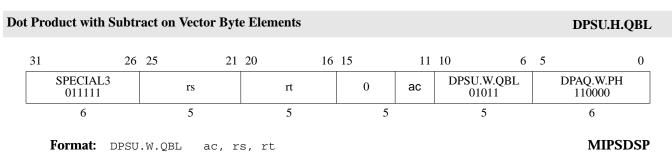

| DPSU.H.QBL                                  |  |

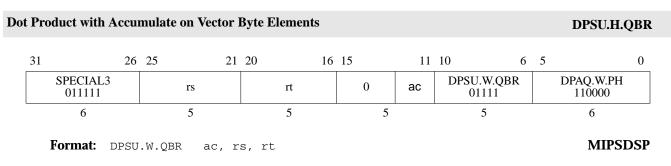

| DPSU.H.QBR                                  |  |

| EXTP                                        |  |

| EXTPDP                                      |  |

| EXTPDPV                                     |  |

| EXTPV                                       |  |

| EXTR[_R/RS].W                               |  |

| EXTR_S.H                                    |  |

| EXTRV[_R/RS].W                              |  |

| EXTRV_S.H                                   |  |

| INSV                                        |  |

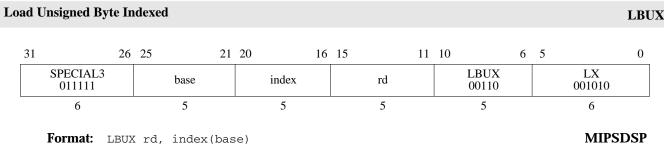

| LBUX                                        |  |

| LHX                                         |  |

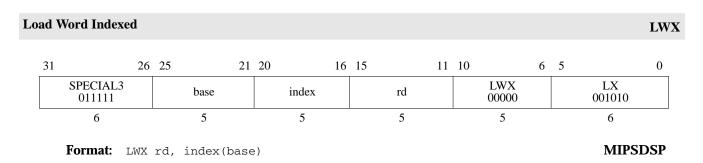

| LWX                                         |  |

| MAQ_S[A].W.PHL                              |  |

| MAQ_S[A].W.PHR                              |  |

| MFHI                                        |  |

| MFLO                                        |  |

| MODSUB                                      |  |

| MTHI                                        |  |

| MTHLIP                                      |  |

| MTLO                                        |  |

| MULEQ_S.W.PHL                               |  |

| MULEQ_S.W.PHR                               |  |

| MULEU_S.PH.QBL                              |  |

| MULEU_S.PH.QBR                              |  |

| MULQ_RS.PH                                  |  |

| MULSAQ_S.W.PH                               |  |

| PACKRL.PH                                   |  |

| PICK.PH                                     |  |

| PICK.QB                                     |  |

| PRECEQ.W.PHL                                |  |

| PRECEQ.W.PHR                                |  |

ii

| PRECEQU.PH.QBL                                                        | . 120 |

|-----------------------------------------------------------------------|-------|

| PRECEQU.PH.QBLA                                                       |       |

| PRECEQU.PH.QBR                                                        |       |

| PRECEQU.PH.QBRA                                                       |       |

| PRECEU.PH.QBL                                                         |       |

| PRECEU.PH.QBLA                                                        |       |

| PRECEU.PH.QBR                                                         |       |

| PRECEU.PH.QBRA                                                        |       |

| PRECRQ.PH.W                                                           |       |

| PRECRQ.QB.PH                                                          |       |

| PRECRQ_RS.PH.W                                                        |       |

| PRECRQU_S.QB.PH                                                       |       |

| RADDU.W.QB                                                            |       |

| RDDSP                                                                 |       |

| REPL.PH                                                               |       |

| REPL.QB                                                               |       |

| REPLV.PH                                                              |       |

| REPLV.QB                                                              |       |

| SHILO                                                                 |       |

| SHILOV                                                                |       |

| SHLL[_S].PH                                                           | 142   |

| SHLLV[_S].PH                                                          |       |

| SHLL.QB                                                               | 146   |

| SHLLV.QB                                                              | 147   |

| SHLL_S.W                                                              | 148   |

| SHLLV_S.W                                                             | 149   |

| SHRA[_R].PH                                                           | 150   |

| SHRAV[_R].PH                                                          | 151   |

| SHRA_R.W                                                              | 152   |

| SHRAV_R.W                                                             | 153   |

| SHRL.QB                                                               | 154   |

| SHRLV.QB                                                              | 155   |

| SUBQ[_S].PH                                                           |       |

| SUBQ_S.W                                                              |       |

| SUBU[_S].QB                                                           |       |

| WRDSP                                                                 | 161   |

| Appendix A Endian-Agnostic Reference to Register Elements             | 163   |

| A.1 Using Endian-Agnostic Instruction Names                           | 163   |

| A.2 Mapping Endian-Agnostic Instruction Names to DSP ASE Instructions |       |

|                                                                       |       |

| Appendix B Revision History                                           | 167   |

# List of Figures

| Figure 2-1: Example of Instruction Description                                                                                        |     |

|---------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 2-2: Example of Instruction Fields                                                                                             | 9   |

| Figure 2-3: Example of Instruction Descriptive Name and Mnemonic                                                                      | 9   |

| Figure 2-4: Example of Instruction Format                                                                                             |     |

| Figure 2-5: Example of Instruction Purpose                                                                                            |     |

| Figure 2-6: Example of Instruction Description                                                                                        |     |

| Figure 2-7: Example of Instruction Restrictions                                                                                       |     |

| Figure 2-8: Example of Instruction Operation                                                                                          |     |

| Figure 2-9: Example of Instruction Exception                                                                                          |     |

| Figure 2-10: Example of Instruction Programming Notes                                                                                 |     |

| Figure 2-11: COP_LW Pseudocode Function                                                                                               |     |

| Figure 2-12: COP_LD Pseudocode Function                                                                                               |     |

| Figure 2-13: COP_SW Pseudocode Function                                                                                               |     |

| Figure 2-14: COP_SD Pseudocode Function                                                                                               |     |

| Figure 2-15: CoprocessorOperation Pseudocode Function                                                                                 |     |

| Figure 2-16: AddressTranslation Pseudocode Function                                                                                   |     |

| Figure 2-17: LoadMemory Pseudocode Function                                                                                           |     |

| Figure 2-18: StoreMemory Pseudocode Function                                                                                          |     |

| Figure 2-19: Prefetch Pseudocode Function                                                                                             |     |

| Figure 2-20: SyncOperation Pseudocode Function                                                                                        |     |

| Figure 2-21: ValueFPR Pseudocode Function                                                                                             |     |

| Figure 2-22: StoreFPR Pseudocode Function                                                                                             |     |

| Figure 2-23: CheckFPException Pseudocode Function                                                                                     | 20  |

| Figure 2-24: FPConditionCode Pseudocode Function                                                                                      | 20  |

| Figure 2-25: SetFPConditionCode Pseudocode Function                                                                                   | 20  |

| Figure 2-26: SignalException Pseudocode Function                                                                                      |     |

| Figure 2-27: SignalDebugBreakpointException Pseudocode Function                                                                       |     |

| Figure 2-28: SignalDebugModeBreakpointException Pseudocode Function                                                                   |     |

| Figure 2-29: NullifyCurrentInstruction PseudoCode Function                                                                            |     |

| Figure 2-30: JumpDelaySlot Pseudocode Function                                                                                        |     |

| Figure 2-31: PolyMult Pseudocode Function                                                                                             |     |

| Figure 3-1: Computing the Value of a Fixed-Point (Q7) Number                                                                          |     |

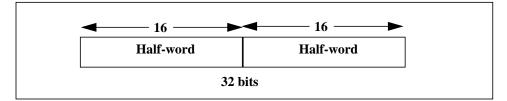

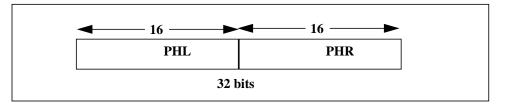

| Figure 3-2: A Paired-Half (PH) Representation in a GPR for the MIPS32® Architecture                                                   |     |

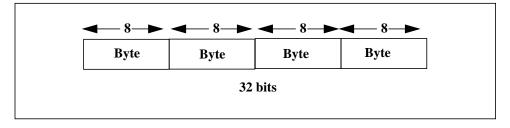

| Figure 3-3: A Quad-Byte (QB) Representation in a GPR for the MIPS32® Architecture                                                     |     |

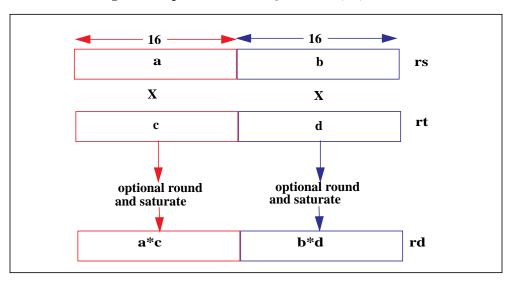

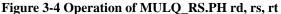

| Figure 3-4: Operation of MULQ_RS.PH rd, rs, rt                                                                                        |     |

| Figure 3-5: MIPS32® DSP ASE Control Register (DSPControl) Format                                                                      |     |

| Figure 3-6: Config3 Register Format                                                                                                   |     |

| Figure 3-7: Status Register Format                                                                                                    |     |

| Figure 5-1: Sample Bit Encoding Table                                                                                                 |     |

| Figure 5-1: Sample Bit Encoding Fable                                                                                                 |     |

| Figure 5-2: SPECIAL3 Encoding for the ABSQ_S.PH instruction sub-class without immediate field                                         |     |

| Figure 5-5. SPECIALS Encoding for the ABSQ_S.PH instruction sub-class without immediate field                                         |     |

|                                                                                                                                       |     |

| Figure 5-5: SPECIAL3 Encoding for the SHLL.QB instruction sub-class<br>Figure 5-6: SPECIAL3 Encoding for the LX instruction sub-class |     |

| Figure 5-6: SPECIALS Encoding for the DPAQ.W.PH instruction sub-class                                                                 |     |

|                                                                                                                                       |     |

| Figure 5-8: SPECIAL3 Encoding Example for the EXTR.W instruction sub-class type 1                                                     |     |

| Figure 5-9: SPECIAL3 Encoding Example for the EXTR.W instruction sub-class type 2                                                     |     |

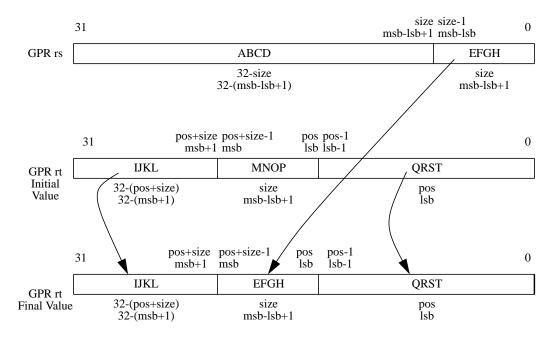

| Figure 5-10: SPECIAL3 Encoding Example for the EXTR.W instruction sub-class type 3<br>Figure 6-1: Operation of the INSV Instruction   |     |

| Figure 6-1: Operation of the INS V Instruction                                                                                        |     |

| Figure A-1. The Endlan-Independent FIL and FIK Elements in a OFK for the MIF552® Architecture                                         | 104 |

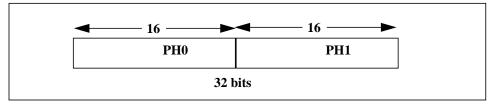

| Figure A-2: The Big-Endian PH0 and PH1 Elements in a GPR for the MIPS32® Architecture           | 164 |

|-------------------------------------------------------------------------------------------------|-----|

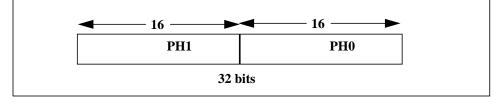

| Figure A-3: The Little-Endian PH0 and PH1 Elements in a GPR for the MIPS32® Architecture        | 164 |

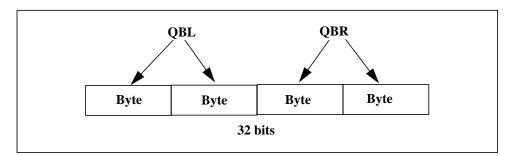

| Figure A-4: The Endian-Independent QBL and QBR Elements in a GPR for the MIPS32® Architecture   |     |

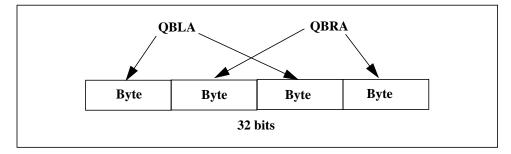

| Figure A-5: The Endian-Independent QBLA and QBRA Elements in a GPR for the MIPS32® Architecture | 165 |

# List of Tables

| Table 1-1: Symbols Used in Instruction Operation Statements                                               | 3  |

|-----------------------------------------------------------------------------------------------------------|----|

| Table 2-1: AccessLength Specifications for Loads/Stores                                                   | 16 |

| Table 3-1: Data Size of DSP Applications                                                                  |    |

| Table 3-2: The Value of a Fixed-Point Q31 Number                                                          | 24 |

| Table 3-3: The Limits of Q15 and Q31 Representations                                                      | 25 |

| Table 3-4: MIPS® DSP ASE Control Register (DSPControl) Field Descriptions                                 | 29 |

| Table 3-5: The Instructions that Set the ouflag bits in DSPControl                                        | 30 |

| Table 3-6: Cause Register ExcCode Field                                                                   |    |

| Table 3-7: Exception Table for the DSP ASE                                                                |    |

| Table 3-8: Instructions that Read/Write Fields in DSPControl                                              |    |

| Table 4-1: List of instructions in the MIPS32® DSP ASE in the Arithmetic sub-class                        | 33 |

| Table 4-2: List of instructions in the MIPS32® DSP ASE in the GPR-Based Shift sub-class                   | 35 |

| Table 4-3: List of instructions in the MIPS32® DSP ASE in the Multiply sub-class                          | 36 |

| Table 4-4: List of instructions in the MIPS32® DSP ASE in the Bit/ Manipulation sub-class                 | 39 |

| Table 4-5: List of instructions in the MIPS32® DSP ASE in the Compare-Pick sub-class                      | 39 |

| Table 4-6: List of instructions in the MIPS32® DSP ASE in the Accumulator and DSPControl Access sub-class | 40 |

| Table 4-7: List of instructions in the MIPS32 <sup>™</sup> DSP ASE in the Indexed-Load sub-class          | 42 |

| Table 4-8: List of instructions in the MIPS32® DSP ASE in the Branch sub-class                            | 42 |

| Table 5-1: Symbols Used in the Instruction Encoding Tables                                                | 44 |

| Table 5-2: MIPS32®DSP ASE Encoding of the Opcode Field                                                    | 44 |

| Table 5-3: MIPS32® SPECIAL3 Encoding of Function Field for DSP ASE Instructions                           |    |

| Table 5-4: MIPS32® REGIMM Encoding of rt Field                                                            |    |

| Table 5-5: MIPS32® ADDU.QB Encoding of the op Field                                                       | 45 |

| Table 5-6: MIPS32® CMPU.EQ.QB Encoding of the op Field                                                    | 46 |

| Table 5-7: MIPS32® ABSQ_S.PH Encoding of the op Field                                                     |    |

| Table 5-8: MIPS32® SHLL.QB Encoding of the op Field                                                       | 47 |

| Table 5-9: MIPS32® LX Encoding of the op Field                                                            |    |

| Table 5-10: MIPS32® DPAQ.W.PH Encoding of the op Field                                                    |    |

| Table 5-11: MIPS32® EXTR.W Encoding of the op Field                                                       | 49 |

# About This Book

The MIPS32® Architecture for Programmers VolumeIV-e comes as a multi-volume set.

- Volume I describes conventions used throughout the document set, and provides an introduction to the MIPS32® Architecture

- Volume II provides detailed descriptions of each instruction in the MIPS32® instruction set

- Volume III describes the MIPS32® Privileged Resource Architecture which defines and governs the behavior of the privileged resources included in a MIPS32® processor implementation

- Volume IV-a describes the MIPS16e<sup>™</sup> Application-Specific Extension to the MIPS32® Architecture

- Volume IV-b describes the MDMX<sup>™</sup> Application-Specific Extension to the MIPS32® Architecture and is not applicable to the MIPS32® document set

- Volume IV-c describes the MIPS-3D® Application-Specific Extension to the MIPS32® Architecture

- Volume IV-d describes the SmartMIPS®Application-Specific Extension to the MIPS32® Architecture

# **1.1 Typographical Conventions**

This section describes the use of *italic*, **bold** and courier fonts in this book.

# 1.1.1 Italic Text

- is used for emphasis

- is used for *bits, fields, registers*, that are important from a software perspective (for instance, address bits used by software, and programmable fields and registers), and various *floating point instruction formats*, such as *S*, *D*, and *PS*

- is used for the memory access types, such as cached and uncached

# 1.1.2 Bold Text

- represents a term that is being defined

- is used for **bits** and **fields** that are important from a hardware perspective (for instance, **register** bits, which are not programmable but accessible only to hardware)

- is used for ranges of numbers; the range is indicated by an ellipsis. For instance, **5..1** indicates numbers 5 through 1

- is used to emphasize UNPREDICTABLE and UNDEFINED behavior, as defined below.

# 1.1.3 Courier Text

Courier fixed-width font is used for text that is displayed on the screen, and for examples of code and instruction pseudocode.

# **1.2 UNPREDICTABLE and UNDEFINED**

The terms **UNPREDICTABLE** and **UNDEFINED** are used throughout this book to describe the behavior of the processor in certain cases. **UNDEFINED** behavior or operations can occur only as the result of executing instructions in a privileged mode (i.e., in Kernel Mode or Debug Mode, or with the CP0 usable bit set in the Status register). Unprivileged software can never cause **UNDEFINED** behavior or operations. Conversely, both privileged and unprivileged software can cause **UNPREDICTABLE** results or operations.

# **1.2.1 UNPREDICTABLE**

**UNPREDICTABLE** results may vary from processor implementation to implementation, instruction to instruction, or as a function of time on the same implementation or instruction. Software can never depend on results that are **UNPREDICTABLE**. **UNPREDICTABLE** operations may cause a result to be generated or not. If a result is generated, it is **UNPREDICTABLE**. **UNPREDICTABLE** operations may cause arbitrary exceptions.

**UNPREDICTABLE** results or operations have several implementation restrictions:

- Implementations of operations generating **UNPREDICTABLE** results must not depend on any data source (memory or internal state) which is inaccessible in the current processor mode

- UNPREDICTABLE operations must not read, write, or modify the contents of memory or internal state which is inaccessible in the current processor mode. For example, UNPREDICTABLE operations executed in user mode must not access memory or internal state that is only accessible in Kernel Mode or Debug Mode or in another process

- UNPREDICTABLE operations must not halt or hang the processor

# **1.2.2 UNDEFINED**

**UNDEFINED** operations or behavior may vary from processor implementation to implementation, instruction to instruction, or as a function of time on the same implementation or instruction. **UNDEFINED** operations or behavior may vary from nothing to creating an environment in which execution can no longer continue. **UNDEFINED** operations or behavior may cause data loss.

UNDEFINED operations or behavior has one implementation restriction:

• **UNDEFINED** operations or behavior must not cause the processor to hang (that is, enter a state from which there is no exit other than powering down the processor). The assertion of any of the reset signals must restore the processor to an operational state

# **1.2.3 UNSTABLE**

**UNSTABLE** results or values may vary as a function of time on the same implementation or instruction. Unlike **UNPREDICTABLE** values, software may depend on the fact that a sampling of an **UNSTABLE** value results in a legal transient value that was correct at some point in time prior to the sampling.

**UNSTABLE** values have one implementation restriction:

• Implementations of operations generating **UNSTABLE** results must not depend on any data source (memory or internal state) which is inaccessible in the current processor mode

# 1.3 Special Symbols in Pseudocode Notation

In this book, algorithmic descriptions of an operation are described as pseudocode in a high-level language notation resembling Pascal. Special symbols used in the pseudocode notation are listed in Table 1-1.

| Symbol                                   | Meaning                                                                                                                                                                                                                                                           |  |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <i>←</i>                                 | Assignment                                                                                                                                                                                                                                                        |  |

| =, ≠                                     | Tests for equality and inequality                                                                                                                                                                                                                                 |  |

|                                          | Bit string concatenation                                                                                                                                                                                                                                          |  |

| x <sup>y</sup>                           | A <i>y</i> -bit string formed by <i>y</i> copies of the single-bit value <i>x</i>                                                                                                                                                                                 |  |

| b#n                                      | A constant value $n$ in base $b$ . For instance 10#100 represents the decimal value 100, 2#100 represents the binary value 100 (decimal 4), and 16#100 represents the hexadecimal value 100 (decimal 256). If the "b#" prefix is omitted, the default base is 10. |  |

| Obn                                      | A constant value <i>n</i> in base 2. For instance 0b100 represents the binary value 100 (decimal 4).                                                                                                                                                              |  |

| 0xn                                      | A constant value <i>n</i> in base 16. For instance 0x100 represents the hexadecimal value 100 (decimal 256).                                                                                                                                                      |  |

| x <sub>yz</sub>                          | Selection of bits $y$ through $z$ of bit string $x$ . Little-endian bit notation (rightmost bit is 0) is used. If $y$ is less than $z$ , this expression is an empty (zero length) bit string.                                                                    |  |

| +, -                                     | 2's complement or floating point arithmetic: addition, subtraction                                                                                                                                                                                                |  |

| *,×                                      | 2's complement or floating point multiplication (both used for either)                                                                                                                                                                                            |  |

| div                                      | 2's complement integer division                                                                                                                                                                                                                                   |  |

| mod                                      | 2's complement modulo                                                                                                                                                                                                                                             |  |

| /                                        | Floating point division                                                                                                                                                                                                                                           |  |

| <                                        | 2's complement less-than comparison                                                                                                                                                                                                                               |  |

| > 2's complement greater-than comparison |                                                                                                                                                                                                                                                                   |  |

| ≤                                        | 2's complement less-than or equal comparison                                                                                                                                                                                                                      |  |

| 2                                        | 2's complement greater-than or equal comparison                                                                                                                                                                                                                   |  |

| nor                                      | Bitwise logical NOR                                                                                                                                                                                                                                               |  |

| xor                                      | Bitwise logical XOR                                                                                                                                                                                                                                               |  |

| and                                      | Bitwise logical AND                                                                                                                                                                                                                                               |  |

| or                                       | Bitwise logical OR                                                                                                                                                                                                                                                |  |

| GPRLEN                                   | The length in bits (32 or 64) of the CPU general-purpose registers                                                                                                                                                                                                |  |

| GPR[x]                                   | CPU general-purpose register x. The content of $GPR[0]$ is always zero. In Release 2 of the Architecture, $GPR[x]$ is a short-hand notation for $SGPR[SRSCtl_{CSS}, x]$ .                                                                                         |  |

| SGPR[s,x]                                | In Release 2 of the Architecture, multiple copies of the CPU general-purpose registers may be implemented. $SGPR[s,x]$ refers to GPR set <i>s</i> , register <i>x</i> .                                                                                           |  |

| FPR[x]                                   | Floating Point operand register <i>x</i>                                                                                                                                                                                                                          |  |

| FCC[CC]                                  | Floating Point condition code CC. <i>FCC[0]</i> has the same value as <i>COC[1]</i> .                                                                                                                                                                             |  |

| FPR[x]                                   | Floating Point (Coprocessor unit 1), general register <i>x</i>                                                                                                                                                                                                    |  |

MIPS32® Architecture for Programmers VolumeIV-e, Revision 1.00

I

| Symbol               | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CPR[z,x,s]           | Coprocessor unit <i>z</i> , general register <i>x</i> , select <i>s</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| CP2CPR[x]            | Coprocessor unit 2, general register <i>x</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| CCR[z,x]             | Coprocessor unit <i>z</i> , control register <i>x</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| CP2CCR[x]            | Coprocessor unit 2, control register <i>x</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| COC[z]               | Coprocessor unit <i>z</i> condition signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Xlat[x]              | Translation of the MIPS16e GPR number x into the corresponding 32-bit GPR number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| BigEndianMem         | Endian mode as configured at chip reset (0 $\rightarrow$ Little-Endian, 1 $\rightarrow$ Big-Endian). Specifies the endianness of the memory interface (see LoadMemory and StoreMemory pseudocode function descriptions), and the endianness of Kernel and Supervisor mode execution.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| BigEndianCPU         | The endianness for load and store instructions ( $0 \rightarrow$ Little-Endian, $1 \rightarrow$ Big-Endian). In User mode, this endianness may be switched by setting the <i>RE</i> bit in the <i>Status</i> register. Thus, BigEndianCPU may be computed as (BigEndianMem XOR ReverseEndian).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| ReverseEndian        | Signal to reverse the endianness of load and store instructions. This feature is available in User mode only, and is implemented by setting the <i>RE</i> bit of the <i>Status</i> register. Thus, ReverseEndian may be computed as ( $SR_{RE}$ and User mode).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| LLbit                | Bit of <b>virtual</b> state used to specify operation for instructions that provide atomic read-modify-write. <i>LLbit</i> is set when a linked load occurs and is tested by the conditional store. It is cleared, during other CPU operation, when a store to the location would no longer be atomic. In particular, it is cleared by exception return instructions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| I:,<br>I+n:,<br>I-n: | This occurs as a prefix to <i>Operation</i> description lines and functions as a label. It indicates the instruction time during which the pseudocode appears to "execute." Unless otherwise indicated, all effects of the current instruction appear to occur during the instruction time of the current instruction. No label is equivalent to a time label of <b>I</b> . Sometimes effects of an instruction appear to occur either earlier or later — that is, during the instruction time of another instruction. When this happens, the instruction operation is written in sections labeled with the instruction time, relative to the current instruction <b>I</b> , in which the effect of that pseudocode appears to occur. For example, an instruction may have a result that is not available until after the next instruction. Such an instruction has the portion of the instruction operation description that writes the result register in a section labeled <b>I+1</b> . The effect of pseudocode statements for the current instruction labelled <b>I+1</b> appears to occur "at the same time" |  |  |  |

|                      | as the effect of pseudocode statements labeled <b>I</b> for the following instruction. Within one pseudocode sequence, the effects of the statements take place in order. However, between sequences of statements for different instructions that occur "at the same time," there is no defined order. Programs must not depend on a particular order of evaluation between such sections.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| РС                   | The <i>Program Counter</i> value. During the instruction time of an instruction, this is the address of the instruction word. The address of the instruction that occurs during the next instruction time is determined by assigning a value to <i>PC</i> during an instruction time. If no value is assigned to <i>PC</i> during an instruction time by any pseudocode statement, it is automatically incremented by either 2 (in the case of a 16-bit MIPS16e instruction) or 4 before the next instruction time. A taken branch assigns the target address to the <i>PC</i> during the instruction time of the instruction in the branch delay slot.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                      | In the MIPS Architecture, the PC value is only visible indirectly, such as when the processor stores the restart address into a GPR on a jump-and-link or branch-and-link instruction, or into a Coprocessor 0 register on an exception. The PC value contains a full 32-bit address all of which are significant during a memory reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                      | In processors that implement the MIPS16e Application Specific Extension, the <i>ISA Mode</i> is a single-bit register that determines in which mode the processor is executing, as follows:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                      | Encoding Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| ISA Mode             | 0       The processor is executing 32-bit MIPS instructions         1       The processor is executing MIIPS16e instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                      | 1       The processor is executing MIIPS16e instructions         In the MIPS Architecture, the ISA Mode value is only visible indirectly, such as when the processor stores a combined value of the upper bits of PC and the ISA Mode into a GPR on a jump-and-link or branch-and-link instruction, or into a Coprocessor 0 register on an exception.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

# Table 1-1 Symbols Used in Instruction Operation Statements

I

| Symbol                                | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PABITS                                | The number of physical address bits implemented is represented by the symbol PABITS. As such, if 36 physical address bits were implemented, the size of the physical address space would be $2^{\text{PABITS}} = 2^{36}$ bytes.                                                                                                                                                                                                                 |  |  |

|                                       | Indicates whether the FPU has 32-bit or 64-bit floating point registers (FPRs). In MIPS32, the FPU has 32 32-bit FPRs in which 64-bit data types are stored in even-odd pairs of FPRs. In MIPS64, the FPU has 32 64-bit FPRs in which 64-bit data types are stored in any FPR.                                                                                                                                                                  |  |  |

| FP32RegistersMode                     | In MIPS32 implementations, <b>FP32RegistersMode</b> is always a 0. MIPS64 implementations have a compatibility mode in which the processor references the FPRs as if it were a MIPS32 implementation. In such a case <b>FP32RegisterMode</b> is computed from the FR bit in the <i>Status</i> register. If this bit is a 0, the processor operates as if it had 32 32-bit FPRs. If this bit is a 1, the processor operates with 32 64-bit FPRs. |  |  |

|                                       | The value of <b>FP32RegistersMode</b> is computed from the FR bit in the <i>Status</i> register.                                                                                                                                                                                                                                                                                                                                                |  |  |

| InstructionInBranchD<br>elaySlot      | Indicates whether the instruction at the Program Counter address was executed in the delay slot of a branch or jump. This condition reflects the <i>dynamic</i> state of the instruction, not the <i>static</i> state. That is, the value is false if a branch or jump occurs to an instruction whose PC immediately follows a branch or jump, but which is not executed in the delay slot of a branch or jump.                                 |  |  |

| SignalException(exce ption, argument) | Causes an exception to be signaled, using the exception parameter as the type of exception and the argument parameter as an exception-specific argument). Control does not return from this pseudocode function - the exception is signaled at the point of the call.                                                                                                                                                                           |  |  |

#### **Table 1-1 Symbols Used in Instruction Operation Statements**

# **1.4 For More Information**

Various MIPS RISC processor manuals and additional information about MIPS products can be found at the MIPS URL:

http://www.mips.com

I

Comments or questions on the MIPS32® Architecture or this document should be directed to

MIPS Architecture Group MIPS Technologies, Inc. 1225 Charleston Road Mountain View, CA 94043

or via E-mail to architecture@mips.com.

# Guide to the Instruction Set

This chapter provides a detailed guide to understanding the instruction descriptions, which are listed in alphabetical order in the tables at the beginning of the next chapter.

# 2.1 Understanding the Instruction Fields

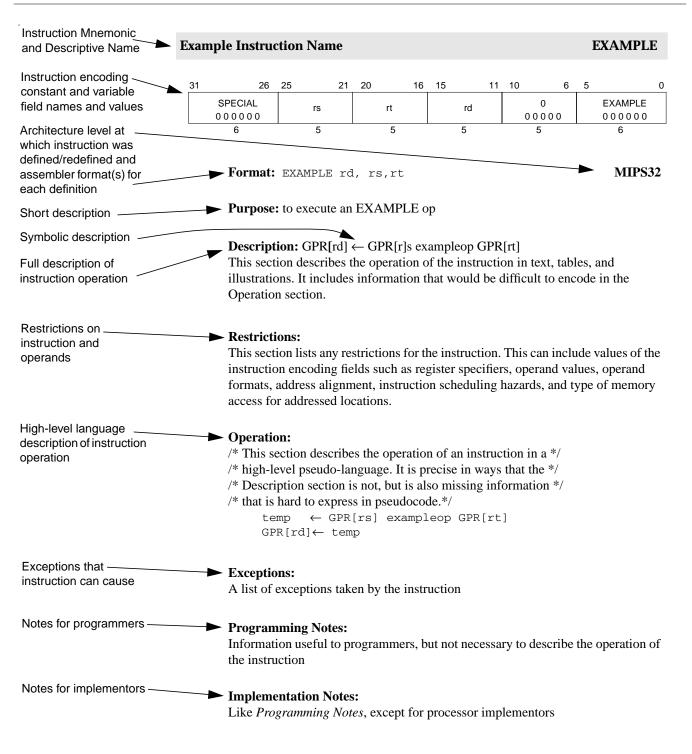

Figure 2-1 shows an example instruction. Following the figure are descriptions of the fields listed below:

- "Instruction Fields" on page 8

- "Instruction Descriptive Name and Mnemonic" on page 9

- "Format Field" on page 9

- "Purpose Field" on page 10

- "Description Field" on page 10

- "Restrictions Field" on page 10

- "Operation Field" on page 11

- "Exceptions Field" on page 11

- "Programming Notes and Implementation Notes Fields" on page 11

**Figure 2-1 Example of Instruction Description**

## 2.1.1 Instruction Fields

Fields encoding the instruction word are shown in register form at the top of the instruction description. The following rules are followed:

ADD

MIPS32

- The values of constant fields and the *opcode* names are listed in uppercase (SPECIAL and ADD in Figure 2-2). Constant values in a field are shown in binary below the symbolic or hexadecimal value.

- All variable fields are listed with the lowercase names used in the instruction description (rs, rt and rd in Figure 2-2).

- Fields that contain zeros but are not named are unused fields that are required to be zero (bits 10:6 in Figure 2-2). If such fields are set to non-zero values, the operation of the processor is **UNPREDICTABLE**.

| 31 26   | 25 21 | 20 16 | 15 11 | 10 6  | 5 0    |

|---------|-------|-------|-------|-------|--------|

| SPECIAL |       | at    | h     | 0     | ADD    |

| 000000  | rs    | п     | rd    | 00000 | 100000 |

| 6       | 5     | 5     | 5     | 5     | 6      |

#### **Figure 2-2 Example of Instruction Fields**

#### 2.1.2 Instruction Descriptive Name and Mnemonic

The instruction descriptive name and mnemonic are printed as page headings for each instruction, as shown in Figure 2-3.

Add Word

#### Figure 2-3 Example of Instruction Descriptive Name and Mnemonic

#### 2.1.3 Format Field

The assembler formats for the instruction and the architecture level at which the instruction was originally defined are given in the *Format* field. If the instruction definition was later extended, the architecture levels at which it was extended and the assembler formats for the extended definition are shown in their order of extension (for an example, see C.cond.fmt). The MIPS architecture levels are inclusive; higher architecture levels include all instructions in previous levels. Extensions to instructions are backwards compatible. The original assembler formats are valid for the extended architecture.

Format: ADD rd, rs, rt

#### **Figure 2-4 Example of Instruction Format**

The assembler format is shown with literal parts of the assembler instruction printed in uppercase characters. The variable parts, the operands, are shown as the lowercase names of the appropriate fields. The architectural level at which the instruction was first defined, for example "MIPS32" is shown at the right side of the page.

There can be more than one assembler format for each architecture level. Floating point operations on formatted data show an assembly format with the actual assembler mnemonic for each valid value of the *fmt* field. For example, the ADD.fmt instruction lists both ADD.S and ADD.D.

The assembler format lines sometimes include parenthetical comments to help explain variations in the formats (once again, see C.cond.fmt). These comments are not a part of the assembler format.

#### 2.1.4 Purpose Field

The *Purpose* field gives a short description of the use of the instruction.

#### **Purpose:**

To add 32-bit integers. If an overflow occurs, then trap.

#### **Figure 2-5 Example of Instruction Purpose**

#### 2.1.5 Description Field

If a one-line symbolic description of the instruction is feasible, it appears immediately to the right of the *Description* heading. The main purpose is to show how fields in the instruction are used in the arithmetic or logical operation.

```

Description: GPR[rd] ← GPR[rs] + GPR[rt]

```

The 32-bit word value in GPR rt is added to the 32-bit value in GPR rs to produce a 32-bit result.

- If the addition results in 32-bit 2's complement arithmetic overflow, the destination register is not modified and an Integer Overflow exception occurs

- If the addition does not overflow, the 32-bit result is placed into GPR rd

Figure 2-6 Example of Instruction Description

The body of the section is a description of the operation of the instruction in text, tables, and figures. This description complements the high-level language description in the *Operation* section.

This section uses acronyms for register descriptions. "GPR *rt*" is CPU general-purpose register specified by the instruction field *rt*. "FPR *fs*" is the floating point operand register specified by the instruction field *fs*. "CP1 register *fd*" is the coprocessor 1 general register specified by the instruction field *fd*. "*FCSR*" is the floating point *Control /Status* register.

# 2.1.6 Restrictions Field

The *Restrictions* field documents any possible restrictions that may affect the instruction. Most restrictions fall into one of the following six categories:

- Valid values for instruction fields (for example, see floating point ADD.fmt)

- ALIGNMENT requirements for memory addresses (for example, see LW)

- Valid values of operands (for example, see DADD)

- Valid operand formats (for example, see floating point ADD.fmt)

- Order of instructions necessary to guarantee correct execution. These ordering constraints avoid pipeline hazards for which some processors do not have hardware interlocks (for example, see MUL).

- Valid memory access types (for example, see LL/SC)

**Restrictions:**

None

Figure 2-7 Example of Instruction Restrictions

# 2.1.7 Operation Field

The *Operation* field describes the operation of the instruction as pseudocode in a high-level language notation resembling Pascal. This formal description complements the *Description* section; it is not complete in itself because many of the restrictions are either difficult to include in the pseudocode or are omitted for legibility.

#### **Operation:**

```

temp ← (GPR[rs]<sub>31</sub>||GPR[rs]<sub>31..0</sub>) + (GPR[rt]<sub>31</sub>||GPR[rt]<sub>31..0</sub>)

if temp<sub>32</sub> ≠ temp<sub>31</sub> then

SignalException(IntegerOverflow)

else

GPR[rd] ← temp

endif

```

#### Figure 2-8 Example of Instruction Operation

See Section 2.2, "Operation Section Notation and Functions" on page 12 for more information on the formal notation used here.

#### 2.1.8 Exceptions Field

The *Exceptions* field lists the exceptions that can be caused by *Operation* of the instruction. It omits exceptions that can be caused by the instruction fetch, for instance, TLB Refill, and also omits exceptions that can be caused by asynchronous external events such as an Interrupt. Although a Bus Error exception may be caused by the operation of a load or store instruction, this section does not list Bus Error for load and store instructions because the relationship between load and store instructions and external error indications, like Bus Error, are dependent upon the implementation.

#### **Exceptions:**

Integer Overflow

#### Figure 2-9 Example of Instruction Exception

An instruction may cause implementation-dependent exceptions that are not present in the *Exceptions* section.

#### 2.1.9 Programming Notes and Implementation Notes Fields

The *Notes* sections contain material that is useful for programmers and implementors, respectively, but that is not necessary to describe the instruction and does not belong in the description sections.

#### **Programming Notes:**

ADDU performs the same arithmetic operation but does not trap on overflow.

Figure 2-10 Example of Instruction Programming Notes

# 2.2 Operation Section Notation and Functions

In an instruction description, the *Operation* section uses a high-level language notation to describe the operation performed by each instruction. Special symbols used in the pseudocode are described in the previous chapter. Specific pseudocode functions are described below.

This section presents information about the following topics:

- "Instruction Execution Ordering" on page 12

- "Pseudocode Functions" on page 12

#### 2.2.1 Instruction Execution Ordering

Each of the high-level language statements in the *Operations* section are executed sequentially (except as constrained by conditional and loop constructs).

## 2.2.2 Pseudocode Functions

There are several functions used in the pseudocode descriptions. These are used either to make the pseudocode more readable, to abstract implementation-specific behavior, or both. These functions are defined in this section, and include the following:

- "Coprocessor General Register Access Functions" on page 12

- "Memory Operation Functions" on page 14

- "Floating Point Functions" on page 17

- "Miscellaneous Functions" on page 20

#### 2.2.2.1 Coprocessor General Register Access Functions

Defined coprocessors, except for CP0, have instructions to exchange words and doublewords between coprocessor general registers and the rest of the system. What a coprocessor does with a word or doubleword supplied to it and how a coprocessor supplies a word or doubleword is defined by the coprocessor itself. This behavior is abstracted into the functions described in this section.

#### COP\_LW