The revision list can be viewed directly by clicking the title page.

The revision list summarizes the locations of revisions and additions. Details should always be checked by referring to the relevant text.

SH-4A Software Manual

Renesas 32-Bit RISC Microcomputer SuperH™ RISC engine Family

Software Manua

Rev. 1.50 Revision Date: Oct. 29, 2004

RenesasTechnology www.renesas.com

## Keep safety first in your circuit designs!

Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party.

- 2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein.

- The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

- Please also pay attention to information published by Renesas Technology Corp. by various means, including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

- Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- 8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.

# **General Precautions on Handling of Product**

#### 1. Treatment of NC Pins

Note: Do not connect anything to the NC pins.

The NC (not connected) pins are either not connected to any of the internal circuitry or are they are used as test pins or to reduce noise. If something is connected to the NC pins, the operation of the LSI is not guaranteed.

## 2. Treatment of Unused Input Pins

Note: Fix all unused input pins to high or low level.

Generally, the input pins of CMOS products are high-impedance input pins. If unused pins are in their open states, intermediate levels are induced by noise in the vicinity, a pass-through current flows internally, and a malfunction may occur.

### 3. Processing before Initialization

Note: When power is first supplied, the product's state is undefined.

The states of internal circuits are undefined until full power is supplied throughout the chip and a low level is input on the reset pin. During the period where the states are undefined, the register settings and the output state of each pin are also undefined. Design your system so that it does not malfunction because of processing while it is in this undefined state. For those products which have a reset function, reset the LSI immediately after the power supply has been turned on.

#### 4. Prohibition of Access to Undefined or Reserved Addresses

Note: Access to undefined or reserved addresses is prohibited.

The undefined or reserved addresses may be used to expand functions, or test registers may have been be allocated to these addresses. Do not access these registers; the system's operation is not guaranteed if they are accessed.

# 5. Reading from/Writing to Reserved Bit of Each Register

Note: Treat the reserved bit of register used in each module as follows except in cases where the specifications for values which are read from or written to the bit are provided in the description.

The bit is always read as 0. The write value should be 0 or one, which has been read immediately before writing.

Writing the value, which has been read immediately before writing has the advantage of preventing the bit from being affected on its extended function when the function is assigned.

# Configuration of This Manual

This manual comprises the following items:

- 1. General Precautions on Handling of Product

- 2. Configuration of This Manual

- 3. Preface

- 4. Contents

- 5. Overview

- 6. Description of Functional Modules

- CPU and System-Control Modules

- On-Chip Peripheral Modules

The configuration of the functional description of each module differs according to the module. However, the generic style includes the following items:

- i) Feature

- ii) Input/Output Pin

- iii) Register Description

- iv) Operation

- v) Usage Note

When designing an application system that includes this LSI, take notes into account. Each section includes notes in relation to the descriptions given, and usage notes are given, as required, as the final part of each section.

- 7. List of Registers

- 8. Appendix

- 9. Index

# **Preface**

The SH-4A is a RISC (Reduced Instruction Set Computer) microcomputer which includes a Renesas Technology-original RISC CPU as its core.

Target Users: This manual was written for users who will be using the SH-4A in the design of

application systems. Users of this manual are expected to understand the

fundamentals of electrical circuits, logical circuits, microcomputers, and assembly/C

languages programming.

Objective: This manual was written to understand the instructions of the SH4A. For the

hardware functions, refer to corresponding hardware manual.

Notes on reading this manual:

In order to understand the overall functions of the chip

Read the manual according to the contents. This manual can be roughly categorized into parts on the CPU, system control functions, and instructions.

In order to understand the instructions

The instruction format and basic operation are explained in section 3, Instruction Set. For details on each instruction operation, read section 10, Instruction Descriptions.

Rules: Register name: The following notation is used for cases when the same or a

similar function, e.g. serial communication, is implemented

on more than one channel:

XXX\_N (XXX is the register name and N is the channel

number)

Bit order: The MSB is on the left and the LSB is on the right.

Number notation: Binary is B'xxxx, hexadecimal is H'xxxx, decimal is xxxx.

Signal notation: An overbar is added to a low-active signal: xxxx

Related Manuals: The latest versions of all related manuals are available from our web site.

Please ensure you have the latest versions of all documents you require.

http://www.renesas.com/

## **Abbreviations**

ALU Arithmetic Logic Unit Address Space Identifier **ASID** CPU Central Processing Unit FPU Floating Point Unit LRU Least Recently Used LSB Least Significant Bit MMU Memory Management Unit

Most Significant Bit MSB PC Program Counter

RISC Reduced Instruction Set Computer

TLB Translation Lookaside Buffer

# Contents

| Sect | tion 1 Overview                           | 1  |

|------|-------------------------------------------|----|

| 1.1  | Features                                  | 1  |

| 1.2  | Changes from SH-4 to SH-4A                | 4  |

| Sect | tion 2 Programming Model                  | 7  |

| 2.1  | Data Formats                              | 7  |

| 2.2  | Register Descriptions                     | 8  |

|      | 2.2.1 Privileged Mode and Banks           | 8  |

|      | 2.2.2 General Registers                   | 11 |

|      | 2.2.3 Floating-Point Registers            | 12 |

|      | 2.2.4 Control Registers                   | 14 |

|      | 2.2.5 System Registers                    | 16 |

| 2.3  | Memory-Mapped Registers                   | 19 |

| 2.4  | Data Formats in Registers                 | 20 |

| 2.5  | Data Formats in Memory                    | 20 |

| 2.6  | Processing States                         | 21 |

| 2.7  | Usage Notes                               | 22 |

|      | 2.7.1 Notes on Self-Modified Codes        | 22 |

| Sect | tion 3 Instruction Set                    | 23 |

| 3.1  | Execution Environment                     |    |

| 3.2  | Addressing Modes                          |    |

| 3.3  | Instruction Set                           |    |

| _    |                                           |    |

|      | tion 4 Pipelining                         |    |

| 4.1  | Pipelines                                 |    |

| 4.2  | Parallel-Executability                    |    |

| 4.3  | Issue Rates and Execution Cycles          | 56 |

| Sect | tion 5 Exception Handling                 | 65 |

| 5.1  | Summary of Exception Handling             | 65 |

| 5.2  | Register Descriptions                     | 65 |

|      | 5.2.1 TRAPA Exception Register (TRA)      |    |

|      | 5.2.2 Exception Event Register (EXPEVT)   | 67 |

|      | 5.2.3 Interrupt Event Register (INTEVT)   |    |

| 5.3  | Exception Handling Functions              |    |

|      | 5.3.1 Exception Handling Flow             |    |

|      | 5.3.2 Exception Handling Vector Addresses |    |

| 5.4  | Exception Types and Priorities            | 70 |

| 5.5  | Excep    | tion Flow                                                      | 72  |

|------|----------|----------------------------------------------------------------|-----|

|      | 5.5.1    | Exception Flow                                                 | 72  |

|      | 5.5.2    | Exception Source Acceptance                                    | 73  |

|      | 5.5.3    | Exception Requests and BL Bit                                  | 74  |

|      | 5.5.4    | Return from Exception Handling                                 | 74  |

| 5.6  | Descri   | iption of Exceptions                                           | 75  |

|      | 5.6.1    | Resets                                                         | 75  |

|      | 5.6.2    | General Exceptions                                             | 77  |

|      | 5.6.3    | Interrupts                                                     | 91  |

|      | 5.6.4    | Priority Order with Multiple Exceptions                        | 92  |

| 5.7  | Usage    | Notes                                                          | 94  |

| Sect | ion 6    | Floating-Point Unit (FPU)                                      | 97  |

| 6.1  |          | res                                                            |     |

| 6.2  |          | Formats                                                        |     |

| 0.2  | 6.2.1    | Floating-Point Format                                          |     |

|      | 6.2.2    | Non-Numbers (NaN)                                              |     |

|      | 6.2.3    | Denormalized Numbers                                           |     |

| 6.3  | Regist   | ter Descriptions                                               |     |

|      | 6.3.1    | Floating-Point Registers                                       |     |

|      | 6.3.2    | Floating-Point Status/Control Register (FPSCR)                 |     |

|      | 6.3.3    | Floating-Point Communication Register (FPUL)                   |     |

| 6.4  | Round    | ling                                                           | 108 |

| 6.5  | Floatii  | ng-Point Exceptions                                            | 109 |

|      | 6.5.1    | General FPU Disable Exceptions and Slot FPU Disable Exceptions | 109 |

|      | 6.5.2    | FPU Exception Sources                                          | 109 |

|      | 6.5.3    | FPU Exception Handling                                         | 110 |

| 6.6  | Graph    | ics Support Functions                                          | 111 |

|      | 6.6.1    | Geometric Operation Instructions                               | 111 |

|      | 6.6.2    | Pair Single-Precision Data Transfer                            | 112 |

| Sect | ion 7    | Memory Management Unit (MMU)                                   | 113 |

| 7.1  |          | iew of MMU                                                     |     |

|      | 7.1.1    | Address Spaces                                                 |     |

| 7.2  | Regist   | ter Descriptions                                               |     |

|      | 7.2.1    | Page Table Entry High Register (PTEH)                          | 122 |

|      | 7.2.2    | Page Table Entry Low Register (PTEL)                           |     |

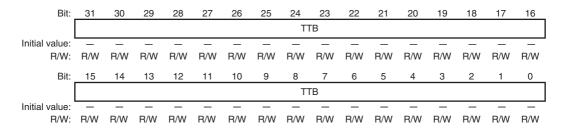

|      | 7.2.3    | Translation Table Base Register (TTB)                          |     |

|      | 7.2.4    | TLB Exception Address Register (TEA)                           |     |

|      | 7.2.5    | MMU Control Register (MMUCR)                                   | 125 |

|      | 7.2.6    | Physical Address Space Control Register (PASCR)                |     |

|      | 7.2.7    | Instruction Re-Fetch Inhibit Control Register (IRMCR)          |     |

| 7.3  | TLB F    | Functions                                                      |     |

| Rev. | 1.50, 10 | 0/04, page x of xx                                             |     |

|      |          | RENESAS                                                        |     |

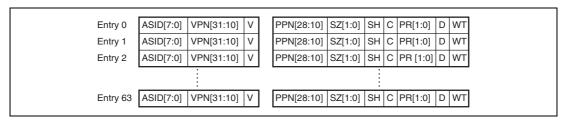

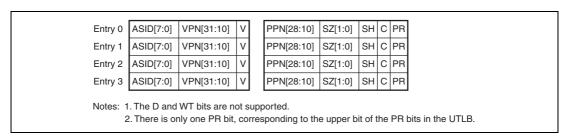

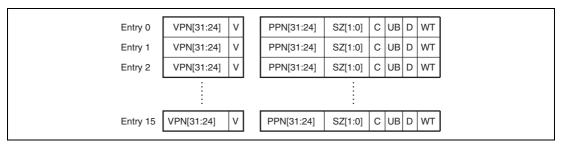

|      | 7.3.1  | Unified TLB (UTLB) Configuration                    |         |

|------|--------|-----------------------------------------------------|---------|

|      | 7.3.2  | Instruction TLB (ITLB) Configuration                |         |

|      | 7.3.3  | Address Translation Method                          | 134     |

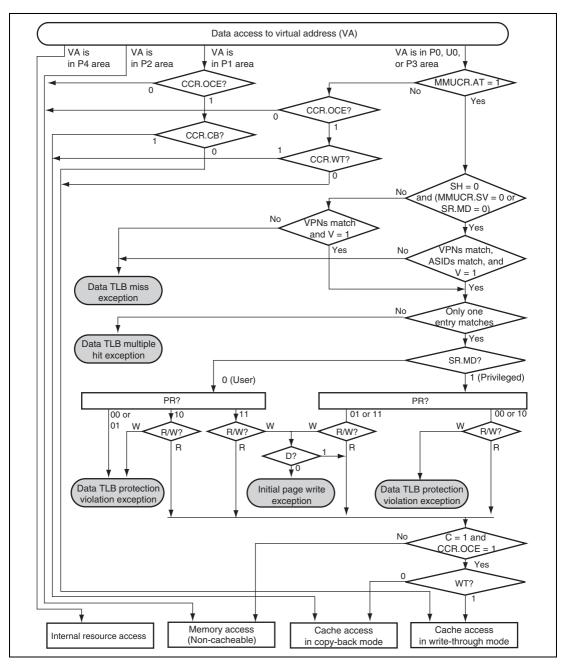

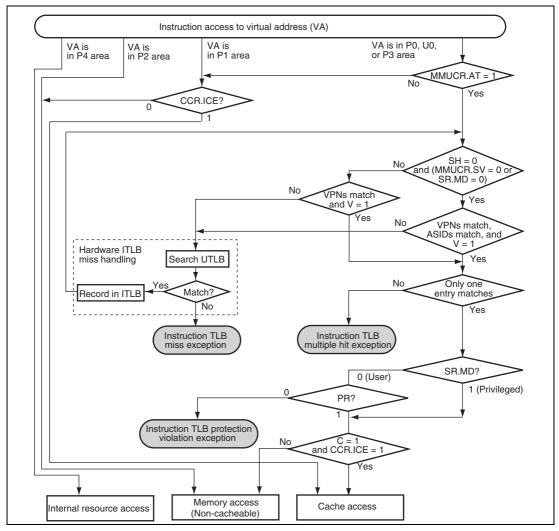

| 7.4  | MMU    | Functions                                           | 136     |

|      | 7.4.1  | MMU Hardware Management                             | 136     |

|      | 7.4.2  | MMU Software Management                             | 136     |

|      | 7.4.3  | MMU Instruction (LDTLB)                             | 137     |

|      | 7.4.4  | Hardware ITLB Miss Handling                         | 139     |

|      | 7.4.5  | Avoiding Synonym Problems                           | 139     |

| 7.5  | MMU    | Exceptions                                          | 140     |

|      | 7.5.1  | Instruction TLB Multiple Hit Exception              | 140     |

|      | 7.5.2  | Instruction TLB Miss Exception                      | 141     |

|      | 7.5.3  | Instruction TLB Protection Violation Exception      | 142     |

|      | 7.5.4  | Data TLB Multiple Hit Exception                     | 143     |

|      | 7.5.5  | Data TLB Miss Exception                             | 143     |

|      | 7.5.6  | Data TLB Protection Violation Exception             | 144     |

|      | 7.5.7  | Initial Page Write Exception                        | 145     |

| 7.6  | Memo   | ory-Mapped TLB Configuration                        | 146     |

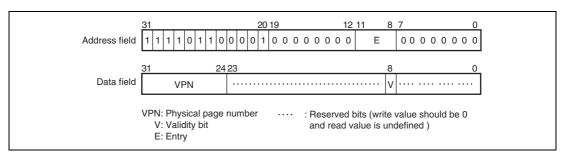

|      | 7.6.1  | ITLB Address Array                                  | 147     |

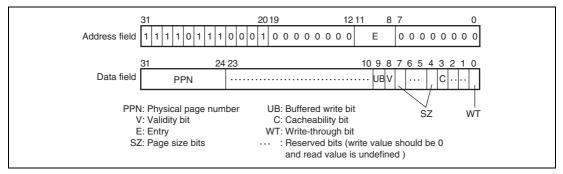

|      | 7.6.2  | ITLB Data Array                                     | 148     |

|      | 7.6.3  | UTLB Address Array                                  | 149     |

|      | 7.6.4  | UTLB Data Array                                     | 150     |

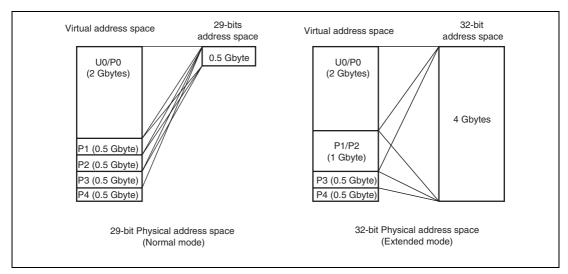

| 7.7  | 32-Bit | Address Extended Mode                               | 151     |

|      | 7.7.1  | Overview of 32-Bit Address Extended Mode            | 152     |

|      | 7.7.2  | Transition to 32-Bit Address Extended Mode          | 152     |

|      | 7.7.3  | Privileged Space Mapping Buffer (PMB) Configuration | 152     |

|      | 7.7.4  | PMB Function                                        | 154     |

|      | 7.7.5  | Memory-Mapped PMB Configuration                     | 154     |

|      | 7.7.6  | Notes on Using 32-Bit Address Extended Mode         | 156     |

| Soot | ion 8  | Caches                                              | 150     |

| 8.1  |        | res                                                 |         |

| 8.2  |        | er Descriptions                                     |         |

| 0.2  | 8.2.1  | Cache Control Register (CCR)                        |         |

|      | 8.2.2  | Queue Address Control Register 0 (QACR0)            |         |

|      | 8.2.3  | Queue Address Control Register 0 (QACR0)            |         |

|      | 8.2.4  | On-Chip Memory Control Register (RAMCR)             |         |

| 8.3  |        | nd Cache Operation                                  |         |

| 0.5  | 8.3.1  | Read Operation                                      |         |

|      | 8.3.2  | Prefetch Operation                                  |         |

|      | 8.3.3  | Write Operation                                     |         |

|      | 8.3.4  | Write-Back Buffer                                   |         |

|      | 8.3.5  | Write-Through Buffer                                |         |

|      | 0.5.5  |                                                     |         |

|      |        | Rev. 1.50, 10/04, page x                            | I OT XX |

|      | 8.3.6     | OC Two-Way Mode                                         | 173 |

|------|-----------|---------------------------------------------------------|-----|

| 8.4  | Instruct  | tion Cache Operation                                    | 173 |

|      | 8.4.1     | Read Operation                                          | 173 |

|      | 8.4.2     | Prefetch Operation                                      | 174 |

|      | 8.4.3     | IC Two-Way Mode                                         |     |

| 8.5  | Cache     | Operation Instruction                                   |     |

|      | 8.5.1     | Coherency between Cache and External Memory             |     |

|      | 8.5.2     | Prefetch Operation                                      |     |

| 8.6  | Memor     | y-Mapped Cache Configuration                            | 176 |

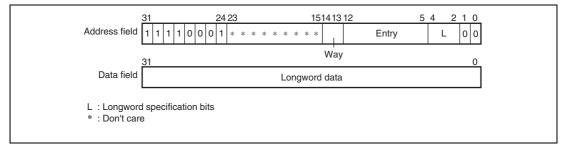

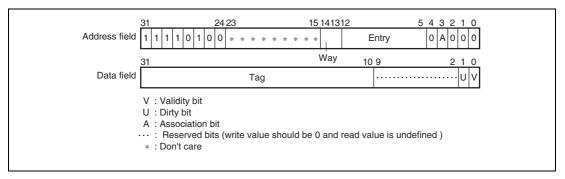

|      | 8.6.1     | IC Address Array                                        | 177 |

|      | 8.6.2     | IC Data Array                                           |     |

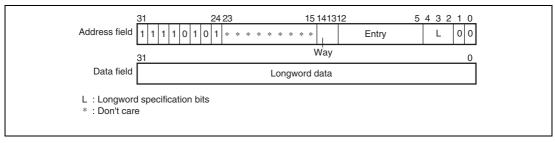

|      | 8.6.3     | OC Address Array                                        |     |

|      | 8.6.4     | OC Data Array                                           |     |

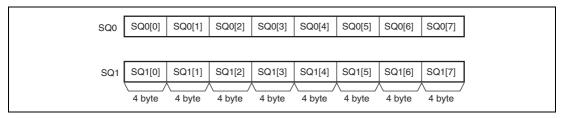

| 8.7  | Store Q   | Queues                                                  | 182 |

|      | 8.7.1     | SQ Configuration                                        | 182 |

|      | 8.7.2     | Writing to SQ                                           | 182 |

|      | 8.7.3     | Transfer to External Memory                             |     |

|      | 8.7.4     | Determination of SQ Access Exception                    | 184 |

|      | 8.7.5     | Reading from SQ                                         | 184 |

| 8.8  | Notes o   | on Using 32-Bit Address Extended Mode                   |     |

|      |           |                                                         |     |

| Sect | ion 9 ]   | L Memory                                                | 187 |

| 9.1  | Feature   | S                                                       | 187 |

| 9.2  | Registe   | er Descriptions                                         | 188 |

|      | 9.2.1     | On-Chip Memory Control Register (RAMCR)                 | 189 |

|      | 9.2.2     | L Memory Transfer Source Address Register 0 (LSA0)      | 190 |

|      | 9.2.3     | L Memory Transfer Source Address Register 1 (LSA1)      | 191 |

|      | 9.2.4     | L Memory Transfer Destination Address Register 0 (LDA0) | 193 |

|      | 9.2.5     | L Memory Transfer Destination Address Register 1 (LDA1) | 195 |

| 9.3  | Operati   | ion                                                     | 197 |

|      | 9.3.1     | Access from the CPU and FPU                             | 197 |

|      | 9.3.2     | Access from the SuperHyway Bus Master Module            | 197 |

|      | 9.3.3     | Block Transfer                                          | 197 |

| 9.4  | L Mem     | ory Protective Functions                                | 199 |

| 9.5  | Usage 1   | Notes                                                   | 200 |

|      | 9.5.1     | Page Conflict                                           | 200 |

|      | 9.5.2     | L Memory Coherency                                      | 200 |

|      | 9.5.3     | Sleep Mode                                              | 200 |

| 9.6  | Notes o   | on Using 32-Bit Address Extended Mode                   | 200 |

|      |           |                                                         |     |

| Sect |           | Instruction Descriptions                                |     |

| 10.1 |           | struction                                               |     |

|      | 10.1.1    | ADD (Add binary): Arithmetic Instruction                | 204 |

| Rev. | 1.50, 10/ | 04, page xii of xx                                      |     |

|      |           | RENESAS                                                 |     |

| 10.1.2 ADDC (Add with Carry): Arithmetic Instruction                          | 205      |

|-------------------------------------------------------------------------------|----------|

| 10.1.3 ADDV (Add with (V flag) Overflow Check): Arithmetic Instruction        | 206      |

| 10.1.4 AND (AND Logical): Logical Instruction                                 | 208      |

| 10.1.5 BF (Branch if False): Branch Instruction                               | 210      |

| 10.1.6 BF/S (Branch if False with Delay Slot): Branch Instruction             | 212      |

| 10.1.7 BRA (Branch): Branch Instruction                                       | 214      |

| 10.1.8 BRAF (Branch Far): Branch Instruction (Delayed Branch Instruction)     | 216      |

| 10.1.9 BT (Branch if True): Branch Instruction                                | 217      |

| 10.1.10 BT/S (Branch if True with Delay Slot): Branch Instruction             | 219      |

| 10.1.11 CLRMAC (Clear MAC Register): System Control Instruction               | 221      |

| 10.1.12 CLRS (Clear S Bit): System Control Instruction                        | 222      |

| 10.1.13 CLRT (Clear T Bit): System Control Instruction                        | 223      |

| 10.1.14 CMP/cond (Compare Conditionally): Arithmetic Instruction              | 224      |

| 10.1.15 DIV0S (Divide (Step 0) as Signed): Arithmetic Instruction             | 228      |

| 10.1.16 DIV0U (Divide (Step 0) as Unsigned): Arithmetic Instruction           | 229      |

| 10.1.17 DIV1 (Divide 1 Step): Arithmetic Instruction                          |          |

| 10.1.18 DMULS.L (Double-length Multiply as Signed): Arithmetic Instruction    | 235      |

| 10.1.19 DMULU.L (Double-length Multiply as Unsigned): Arithmetic Instruction  | 237      |

| 10.1.20 DT (Decrement and Test): Arithmetic Instruction                       | 239      |

| 10.1.21 EXTS (Extend as Signed): Arithmetic Instruction                       | 240      |

| 10.1.22 EXTU (Extend as Unsigned): Arithmetic Instruction                     | 242      |

| 10.1.23 ICBI (Instruction Cache Block Invalidate): Data Transfer Instruction  |          |

| 10.1.24 JMP (Jump): Branch Instruction                                        | 244      |

| 10.1.25 LDC (Load to Control Register): System Control Instruction            |          |

| 10.1.26 LDS (Load to System Register): System Control Instruction             | 249      |

| 10.1.27 LDTLB (Load PTEH/PTEL to TLB): System Control Instruction             |          |

| (Privileged Instruction)                                                      |          |

| 10.1.28 MAC.L (Multiply and Accumulate Long): Arithmetic Instruction          |          |

| 10.1.29 MAC.W (Multiply and Accumulate Word): Arithmetic Instruction          |          |

| 10.1.30 MOV (Move data): Data Transfer Instruction                            |          |

| 10.1.31 MOV (Move Constant Value): Data Transfer Instruction                  |          |

| 10.1.32 MOV (Move Global Data): Data Transfer Instruction                     |          |

| 10.1.33 MOV (Move Structure Data): Data Transfer Instruction                  |          |

| 10.1.34 MOVA (Move Effective Address): Data Transfer Instruction              |          |

| 10.1.35 MOVCA.L (Move with Cache Block Allocation): Data Transfer Instruction |          |

| 10.1.36 MOVCO (Move Conditional): Data Transfer Instruction                   |          |

| 10.1.37 MOVLI (Move Linked): Data Transfer Instruction                        |          |

| 10.1.38 MOVT (Move T Bit): Data Transfer Instruction                          |          |

| 10.1.39 MOVUA (Move Unaligned): Data Transfer Instruction                     |          |

| 10.1.40 MUL.L (Multiply Long): Arithmetic Instruction                         |          |

| 10.1.41 MULS.W (Multiply as Signed Word): Arithmetic Instruction              |          |

| 10.1.42 MULU.W (Multiply as Unsigned Word): Arithmetic Instruction            |          |

| 10.1.43 NEG (Negate): Arithmetic Instruction                                  | 286      |

| Roy 150 10/04 page vi                                                         | iii of v |

|      | 10.1.44 NEGC (Negate with Carry): Arithmetic Instruction                      | 287 |

|------|-------------------------------------------------------------------------------|-----|

|      | 10.1.45 NOP (No Operation): System Control Instruction                        | 288 |

|      | 10.1.46 NOT (Not-logical Complement): Logical Instruction                     | 289 |

|      | 10.1.47 OCBI (Operand Cache Block Invalidate): Data Transfer Instruction      | 290 |

|      | 10.1.48 OCBP (Operand Cache Block Purge): Data Transfer Instruction           | 291 |

|      | 10.1.49 OCBWB (Operand Cache Block Write Back): Data Transfer Instruction     | 292 |

|      | 10.1.50 OR (OR Logical): Logical Instruction                                  | 293 |

|      | 10.1.51 PREF (Prefetch Data to Cache): Data Transfer Instruction              | 296 |

|      | 10.1.52 PREFI (Prefetch Instruction Cache Block): Data Transfer Instruction   | 297 |

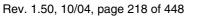

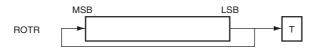

|      | 10.1.53 ROTCL (Rotate with Carry Left): Shift Instruction                     | 298 |

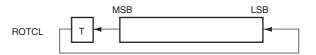

|      | 10.1.54 ROTCR (Rotate with Carry Right): Shift Instruction                    | 299 |

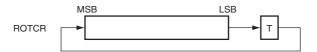

|      | 10.1.55 ROTL (Rotate Left): Shift Instruction                                 | 300 |

|      | 10.1.56 ROTR (Rotate Right): Shift Instruction                                | 301 |

|      | 10.1.57 RTE (Return from Exception): System Control Instruction               | 302 |

|      | 10.1.58 RTS (Return from Subroutine): Branch Instruction                      | 304 |

|      | 10.1.59 SETS (Set S Bit): System Control Instruction                          | 306 |

|      | 10.1.60 SETT (Set T Bit): System Control Instruction                          | 307 |

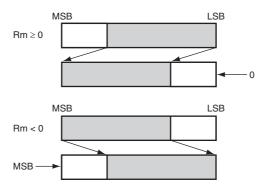

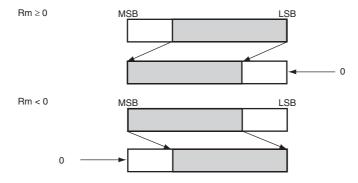

|      | 10.1.61 SHAD (Shift Arithmetic Dynamically): Shift Instruction                | 308 |

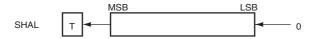

|      | 10.1.62 SHAL (Shift Arithmetic Left): Shift Instruction                       | 310 |

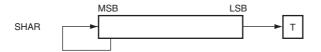

|      | 10.1.63 SHAR (Shift Arithmetic Right): Shift Instruction                      | 311 |

|      | 10.1.64 SHLD (Shift Logical Dynamically): Shift Instruction                   | 312 |

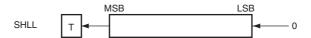

|      | 10.1.65 SHLL (Shift Logical Left ): Shift Instruction                         | 314 |

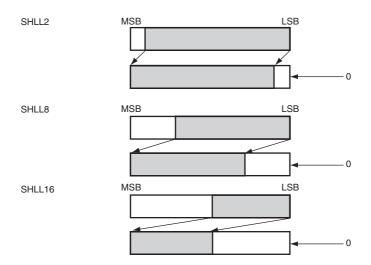

|      | 10.1.66 SHLLn (n bits Shift Logical Left): Shift Instruction                  | 315 |

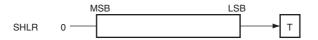

|      | 10.1.67 SHLR (Shift Logical Right): Shift Instruction                         | 317 |

|      | 10.1.68 SHLRn (n bits Shift Logical Right): Shift Instruction                 | 318 |

|      | 10.1.69 SLEEP (Sleep): System Control Instruction (Privileged Instruction)    | 320 |

|      | 10.1.70 STC (Store Control Register): System Control Instruction              |     |

|      | (Privileged Instruction)                                                      | 321 |

|      | 10.1.71 STS (Store System Register): System Control Instruction               | 325 |

|      | 10.1.72 SUB (Subtract Binary): Arithmetic Instruction                         | 327 |

|      | 10.1.73 SUBC (Subtract with Carry): Arithmetic Instruction                    | 328 |

|      | 10.1.74 SUBV (Subtract with (V flag) Underflow Check): Arithmetic Instruction | 329 |

|      | 10.1.75 SWAP (Swap Register Halves): Data Transfer Instruction                | 331 |

|      | 10.1.76 SYNCO (Synchronize Data Operation): Data Transfer Instruction         | 333 |

|      | 10.1.77 TAS (Test And Set): Logical Instruction                               | 334 |

|      | 10.1.78 TRAPA (Trap Always): System Control Instruction                       |     |

|      | 10.1.79 TST (Test Logical): Logical Instruction                               | 337 |

|      | 10.1.80 XOR (Exclusive OR Logical): Logical Instruction                       | 339 |

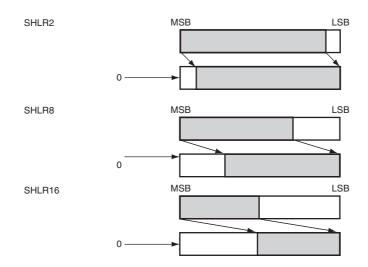

|      | 10.1.81 XTRCT (Extract): Data Transfer Instruction                            | 341 |

| 10.2 | CPU Instructions (FPU related)                                                | 342 |

|      | 10.2.1 BSR (Branch to Subroutine): Branch Instruction                         |     |

|      | (Delayed Branch Instruction)                                                  | 342 |

|      |                                                                               |     |

|      | 10.2.2  | BSRF (Branch to Subroutine Far): Branch Instruction                        |     |

|------|---------|----------------------------------------------------------------------------|-----|

|      |         | (Delayed Branch Instruction)                                               | 344 |

|      | 10.2.3  | JSR (Jump to Subroutine): Branch Instruction (Delayed Branch Instruction)  | 346 |

|      | 10.2.4  | LDC (Load to Control Register): System Control Instruction                 |     |

|      |         | (Privileged Instruction)                                                   | 348 |

|      | 10.2.5  | LDS (Load to FPU System register): System Control Instruction              | 349 |

|      | 10.2.6  | STC (Store Control Register): System Control Instruction                   |     |

|      |         | (Privileged Instruction)                                                   |     |

|      | 10.2.7  | STS (Store from FPU System Register): System Control Instruction           | 352 |

| 10.3 |         | struction                                                                  |     |

|      | 10.3.1  | FABS (Floating-point Absolute Value): Floating-Point Instruction           | 365 |

|      | 10.3.2  | FADD (Floating-point ADD): Floating-Point Instruction                      | 366 |

|      |         | FCMP (Floating-point Compare): Floating-Point Instruction                  | 369 |

|      | 10.3.4  | FCNVDS (Floating-point Convert Double to Single Precision):                |     |

|      |         | Floating-Point Instruction                                                 | 373 |

|      | 10.3.5  | FCNVSD (Floating-point Convert Single to Double Precision):                |     |

|      |         | Floating-Point Instruction                                                 |     |

|      | 10.3.6  | FDIV (Floating-point Divide): Floating-Point Instruction                   | 378 |

|      |         | FIPR (Floating-point Inner Product): Floating-Point Instruction            |     |

|      |         | FLDI0 (Floating-point Load Immediate 0.0): Floating-Point Instruction      |     |

|      |         | FLDI1 (Floating-point Load Immediate 1.0): Floating-Point Instruction      |     |

|      | 10.3.10 | FLDS (Floating-point Load to System register): Floating-Point Instruction  | 386 |

|      | 10.3.11 | FLOAT (Floating-point Convert from Integer): Floating-Point Instruction    | 387 |

|      |         | FMAC (Floating-point Multiply and Accumulate): Floating-Point Instruction. |     |

|      | 10.3.13 | FMOV (Floating-point Move): Floating-Point Instruction                     | 395 |

|      |         | FMOV (Floating-point Move Extension): Floating-Point Instruction           |     |

|      | 10.3.15 | FMUL (Floating-point Multiply): Floating-Point Instruction                 | 402 |

|      | 10.3.16 | FNEG (Floating-point Negate Value): Floating-Point Instruction             | 405 |

|      | 10.3.17 | FPCHG (Pr-bit Change): Floating-Point Instruction                          | 406 |

|      | 10.3.18 | FRCHG (FR-bit Change): Floating-Point Instruction                          | 407 |

|      | 10.3.19 | FSCA (Floating Point Sine And Cosine Approximate):                         |     |

|      |         | Floating-Point Instruction                                                 | 408 |

|      | 10.3.20 | FSCHG (Sz-bit Change): Floating-Point Instruction                          | 410 |

|      | 10.3.21 | FSQRT (Floating-point Square Root): Floating-Point Instruction             | 411 |

|      | 10.3.22 | FSRRA (Floating Point Square Reciprocal Approximate):                      |     |

|      |         | Floating-Point Instruction                                                 | 414 |

|      | 10.3.23 | FSTS (Floating-point Store System Register): Floating-Point Instruction    | 416 |

|      |         | FSUB (Floating-point Subtract): Floating-Point Instruction                 | 417 |

|      | 10.3.25 | FTRC (Floating-point Truncate and Convert to integer):                     |     |

|      |         | Floating-Point Instruction                                                 |     |

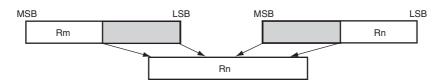

|      | 10.3.26 | FTRV (Floating-point Transform Vector): Floating-Point Instruction         | 423 |

| Sect | tion 11 List of Registers                                             | 427 |

|------|-----------------------------------------------------------------------|-----|

| 11.1 | Register Addresses                                                    |     |

|      | (by functional module, in order of the corresponding section numbers) | 428 |

| 11.2 | Register States in Each Operating Mode                                | 430 |

| App  | endix                                                                 | 431 |

| A.   | CPU Operation Mode Register (CPUOPM)                                  |     |

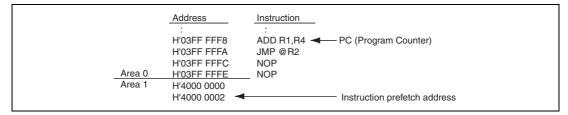

| B.   | Instruction Prefetching and Its Side Effects                          | 433 |

| C.   | Speculative Execution for Subroutine Return                           | 434 |

| D.   | Version Registers (PVR, PRR)                                          | 435 |

| Mai  | n Revisions and Additions in this Edition                             | 437 |

| Inde | ex                                                                    | 445 |

# Figures

| Section 1  | Overview                                           |     |

|------------|----------------------------------------------------|-----|

| Figure 2.1 | Data Formats                                       | 7   |

| Figure 2.2 | CPU Register Configuration in Each Processing Mode | 10  |

| Figure 2.3 | General Registers                                  | 11  |

| Figure 2.4 | Floating-Point Registers                           | 13  |

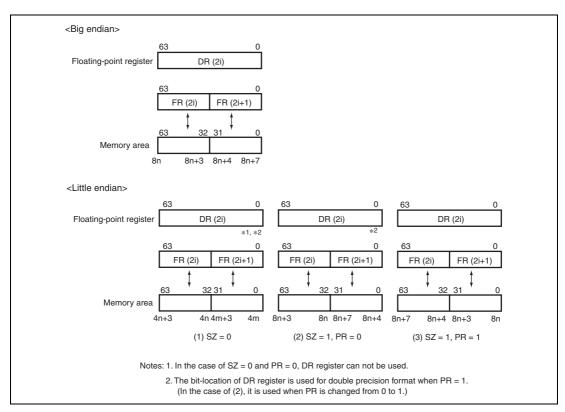

| Figure 2.5 | Relationship between SZ bit and Endian             | 18  |

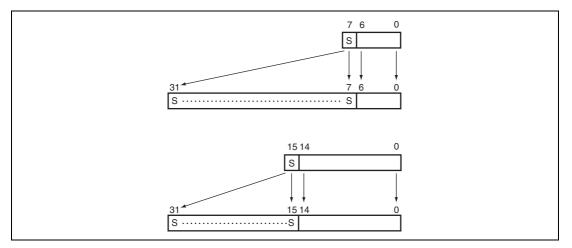

| Figure 2.6 | Formats of Byte Data and Word Data in Register     | 20  |

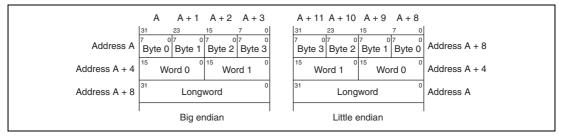

| Figure 2.7 | Data Formats in Memory                             | 21  |

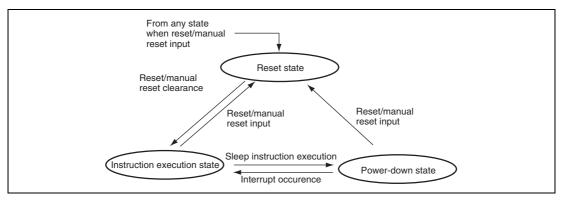

| Figure 2.8 | Processing State Transitions                       |     |

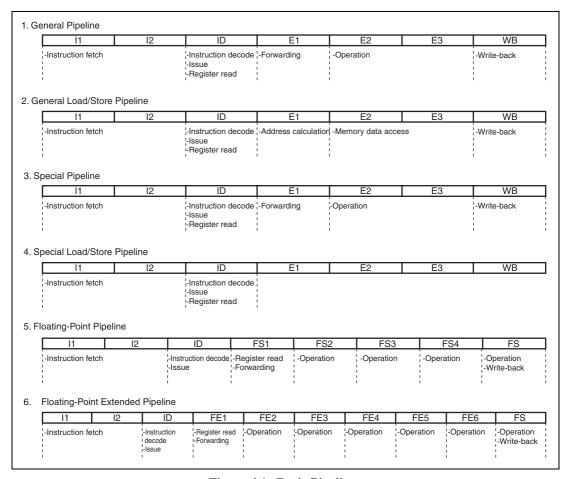

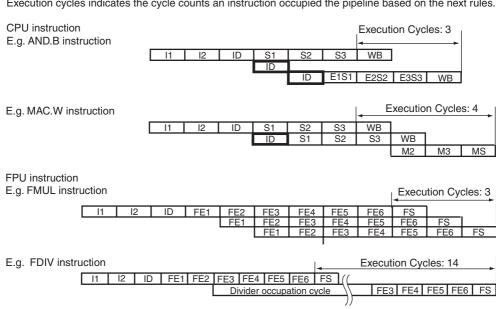

| Section 4  | Pipelining                                         |     |

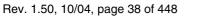

| Figure 4.1 | Basic Pipelines                                    | 43  |

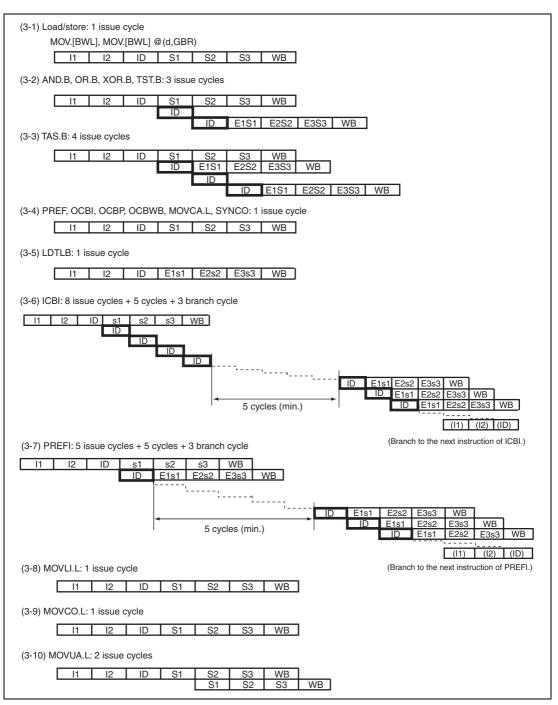

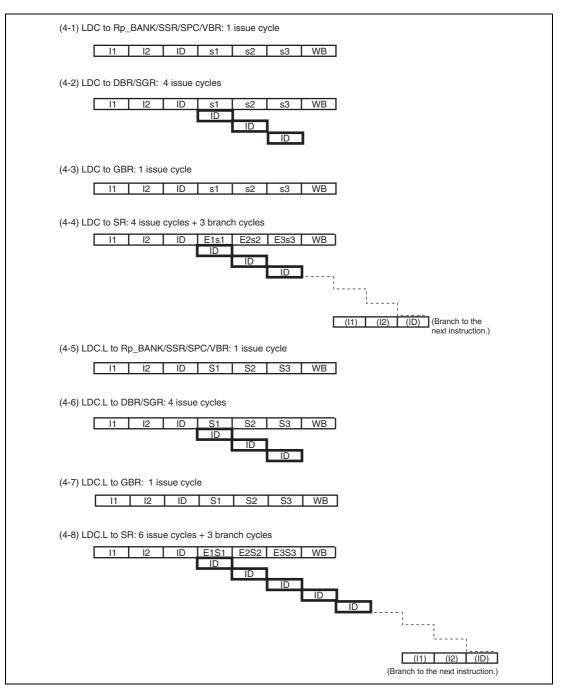

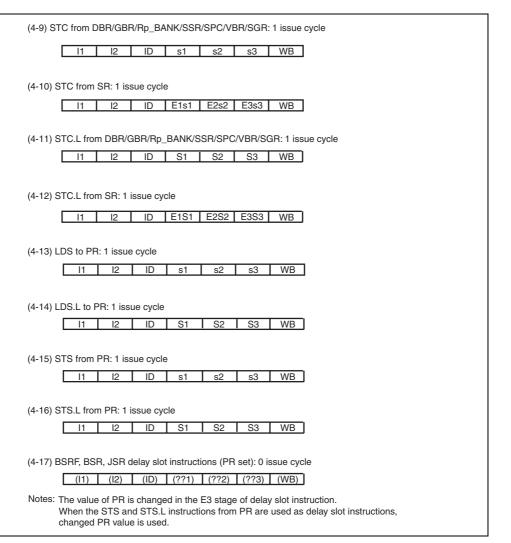

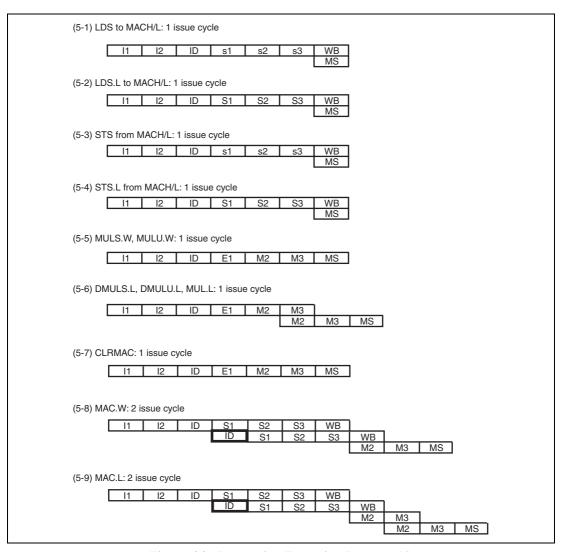

| Figure 4.2 | Instruction Execution Patterns (1)                 | 45  |

| Figure 4.2 | Instruction Execution Patterns (2)                 | 46  |

| Figure 4.2 | Instruction Execution Patterns (3)                 | 47  |

| Figure 4.2 | Instruction Execution Patterns (4)                 | 48  |

| Figure 4.2 | Instruction Execution Patterns (5)                 | 49  |

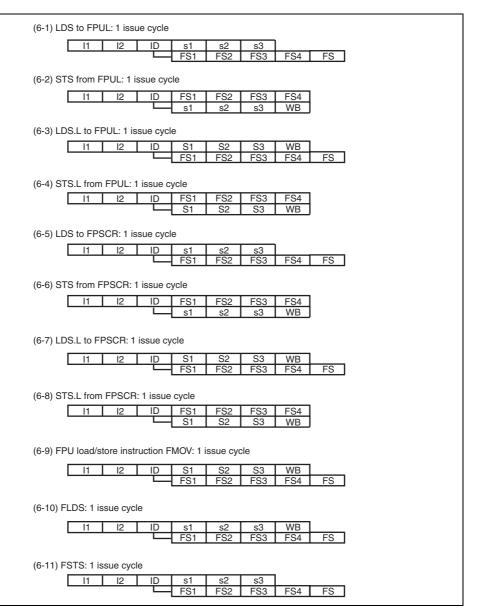

| Figure 4.2 | Instruction Execution Patterns (6)                 | 50  |

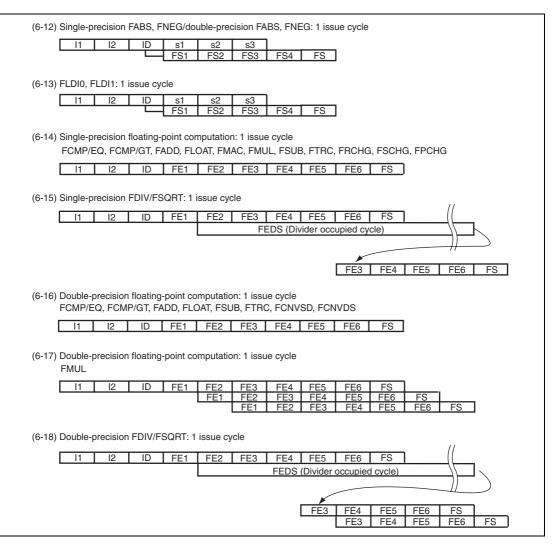

| Figure 4.2 | Instruction Execution Patterns (7)                 | 51  |

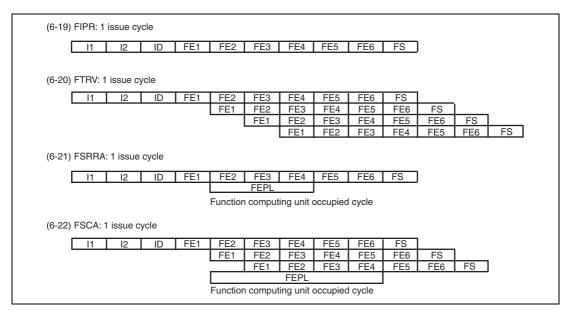

| Figure 4.2 | Instruction Execution Patterns (8)                 | 52  |

| Figure 4.2 | Instruction Execution Patterns (9)                 | 53  |

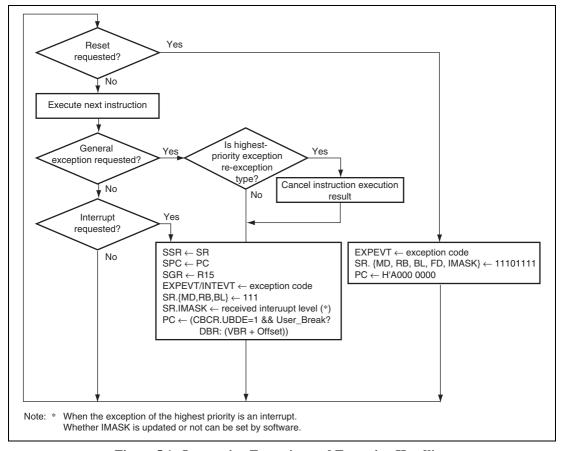

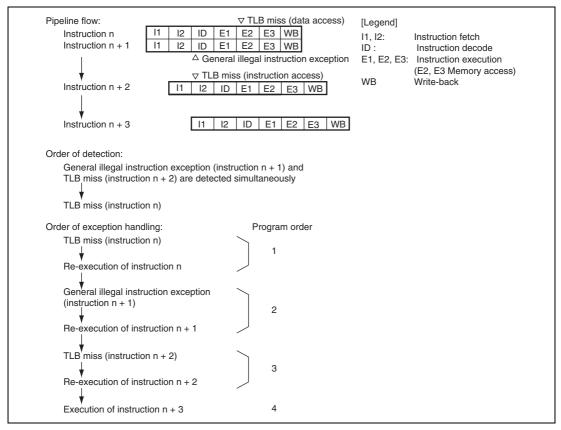

| Section 5  | Exception Handling                                 |     |

| Figure 5.1 | Instruction Execution and Exception Handling       | 72  |

| Figure 5.2 | Example of General Exception Acceptance Order      | 73  |

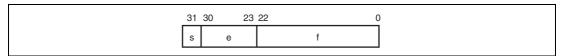

| Section 6  | Floating-Point Unit (FPU)                          |     |

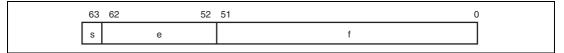

| Figure 6.1 | Format of Single-Precision Floating-Point Number   | 98  |

| Figure 6.2 | Format of Double-Precision Floating-Point Number   | 98  |

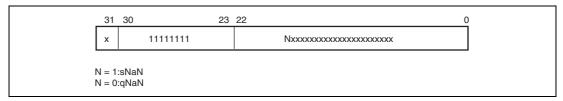

| Figure 6.3 | Single-Precision NaN Bit Pattern                   | 101 |

| Figure 6.4 | Floating-Point Registers                           | 104 |

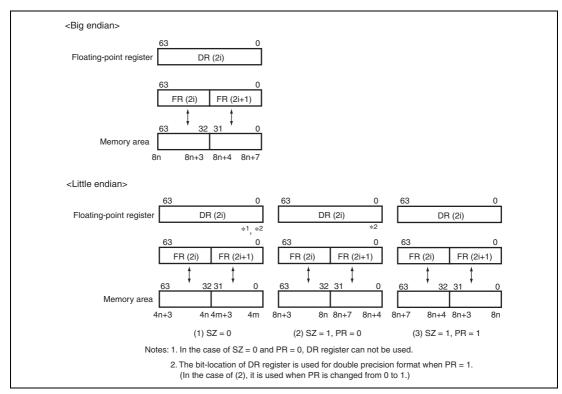

| Figure 6.5 | Relation between SZ Bit and Endian                 | 106 |

| Section 7  | Memory Management Unit (MMU)                       |     |

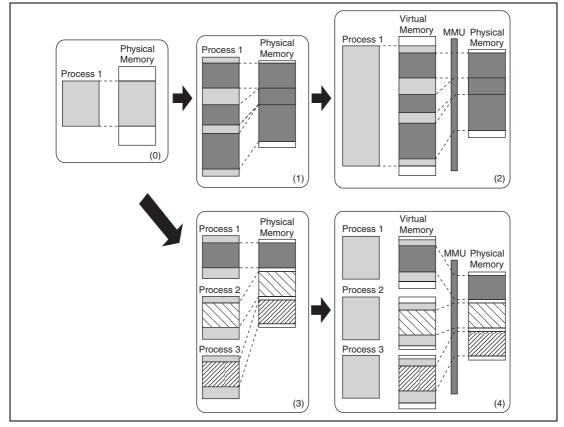

| Figure 7.1 | Role of MMU                                        |     |

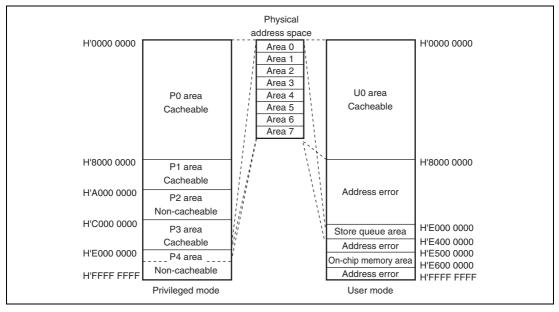

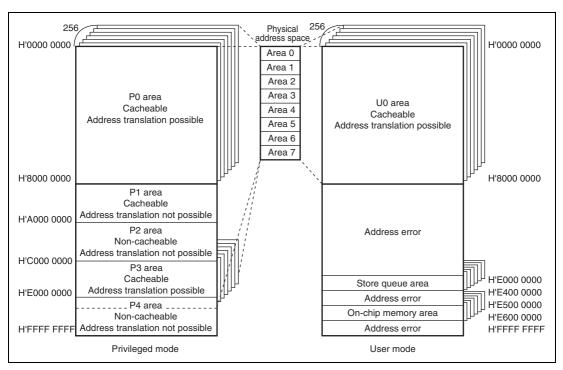

| Figure 7.2 | Virtual Address Space (AT in MMUCR= 0)             | 116 |

| Figure 7.3 | Virtual Address Space (AT in MMUCR= 1)             | 116 |

| Figure 7.4 | P4 Area                                            | 118 |

| Figure 7.5 | Physical Address Space                             | 119 |

| Figure 7.6 |                                                    | 131 |

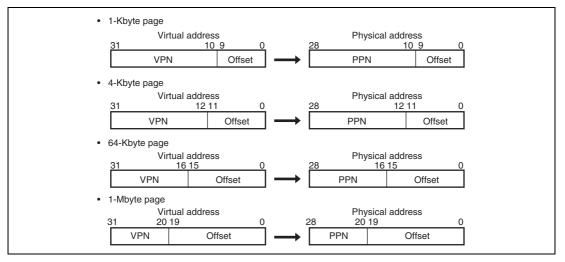

| Figure 7.7 | Relationship between Page Size and Address Format  | 133 |

| Figure 7.8 | ITLB Configuration                                 | 133 |

| rigule 1.9                                                                                     | Flowchart of Memory Access Using UTLB.                                                                                                                                                         | 134                      |

|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Figure 7.10                                                                                    | Flowchart of Memory Access Using ITLB                                                                                                                                                          | 135                      |

| Figure 7.11                                                                                    | Operation of LDTLB Instruction                                                                                                                                                                 | 138                      |

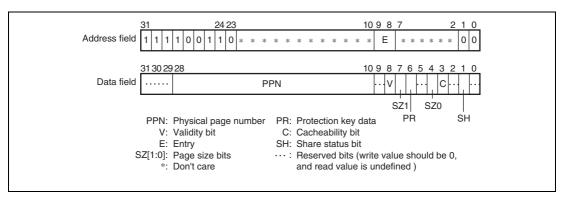

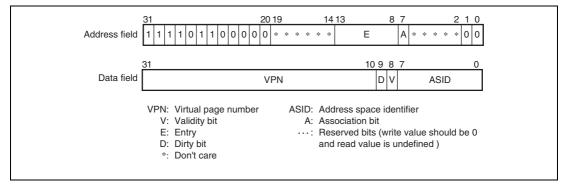

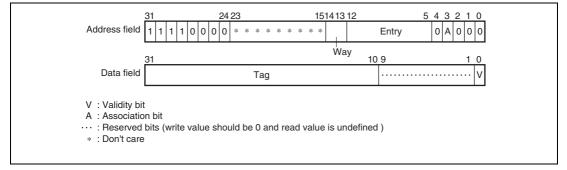

| Figure 7.12                                                                                    | Memory-Mapped ITLB Address Array                                                                                                                                                               | 147                      |

| Figure 7.13                                                                                    | Memory-Mapped ITLB Data Array                                                                                                                                                                  | 148                      |

| Figure 7.14                                                                                    | Memory-Mapped UTLB Address Array                                                                                                                                                               | 150                      |

| Figure 7.15                                                                                    | Memory-Mapped UTLB Data Array                                                                                                                                                                  | 151                      |

| Figure 7.16                                                                                    | Physical Address Space (32-Bit Address Extended Mode)                                                                                                                                          | 151                      |

| Figure 7.17                                                                                    | PMB Configuration                                                                                                                                                                              | 152                      |

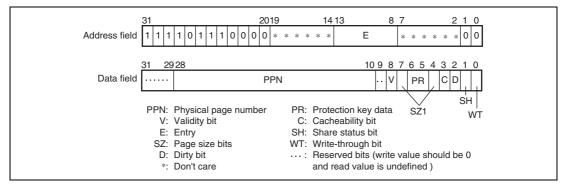

| Figure 7.18                                                                                    | Memory-Mapped PMB Address Array                                                                                                                                                                | 155                      |

| Figure 7.19                                                                                    | Memory-Mapped PMB Data Array                                                                                                                                                                   | 156                      |

| Section 8                                                                                      | Caches                                                                                                                                                                                         |                          |

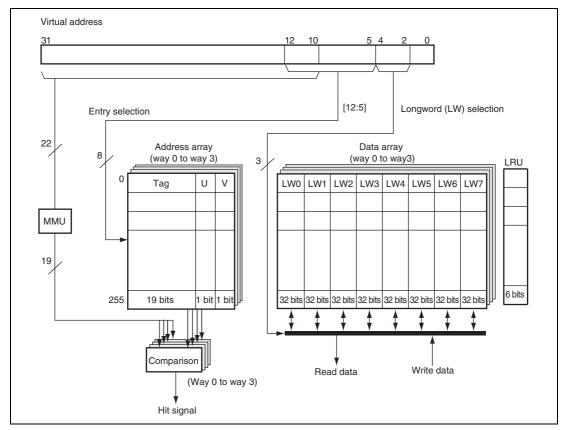

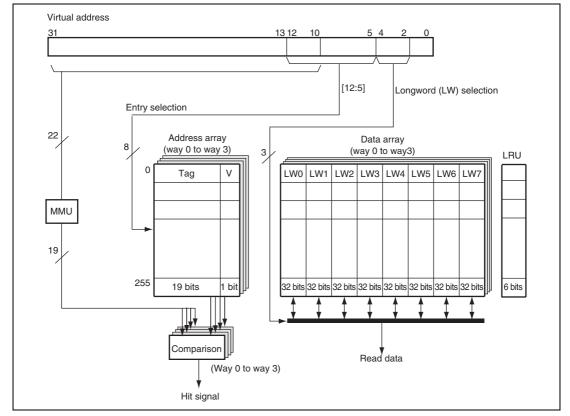

| Figure 8.1                                                                                     | Configuration of Operand Cache (OC)                                                                                                                                                            | 160                      |

| Figure 8.2                                                                                     |                                                                                                                                                                                                |                          |

| 1 15410 0.2                                                                                    | Configuration of Instruction Cache (IC)                                                                                                                                                        | 161                      |

| -                                                                                              | Configuration of Instruction Cache (IC)                                                                                                                                                        |                          |

| Figure 8.3                                                                                     | - · · · · · · · · · · · · · · · · · · ·                                                                                                                                                        | 172                      |

| Figure 8.3<br>Figure 8.4                                                                       | Configuration of Write-Back Buffer                                                                                                                                                             | 172<br>172               |

| Figure 8.3<br>Figure 8.4<br>Figure 8.5                                                         | Configuration of Write-Back Buffer                                                                                                                                                             | 172<br>172<br>178        |

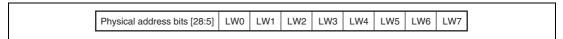

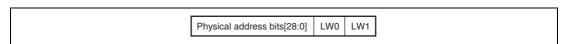

| Figure 8.3<br>Figure 8.4<br>Figure 8.5<br>Figure 8.6                                           | Configuration of Write-Back Buffer  Configuration of Write-Through Buffer  Memory-Mapped IC Address Array                                                                                      | 172<br>172<br>178<br>179 |

| Figure 8.3<br>Figure 8.4<br>Figure 8.5<br>Figure 8.6<br>Figure 8.7                             | Configuration of Write-Back Buffer Configuration of Write-Through Buffer Memory-Mapped IC Address Array Memory-Mapped IC Data Array                                                            | 172<br>178<br>179<br>180 |

| Figure 8.3<br>Figure 8.4<br>Figure 8.5<br>Figure 8.6<br>Figure 8.7<br>Figure 8.8               | Configuration of Write-Back Buffer Configuration of Write-Through Buffer Memory-Mapped IC Address Array Memory-Mapped IC Data Array Memory-Mapped OC Address Array                             |                          |

| Figure 8.3<br>Figure 8.4<br>Figure 8.5<br>Figure 8.6<br>Figure 8.7<br>Figure 8.8<br>Figure 8.9 | Configuration of Write-Back Buffer Configuration of Write-Through Buffer Memory-Mapped IC Address Array Memory-Mapped IC Data Array Memory-Mapped OC Address Array Memory-Mapped OC Data Array |                          |

| Figure 8.3<br>Figure 8.4<br>Figure 8.5<br>Figure 8.6<br>Figure 8.7<br>Figure 8.8<br>Figure 8.9 | Configuration of Write-Back Buffer Configuration of Write-Through Buffer Memory-Mapped IC Address Array Memory-Mapped IC Data Array Memory-Mapped OC Address Array Memory-Mapped OC Data Array |                          |

# **Tables**

| Section 1  | Overview                                            |     |

|------------|-----------------------------------------------------|-----|

| Table 1.1  | Features                                            | 1   |

| Table 1.2  | Changes from SH-4 to SH-4A                          | 4   |

| Section 2  | Programming Model                                   |     |

| Table 2.1  | Initial Register Values                             | 9   |

| Table 2.2  | Bit Allocation for FPU Exception Handling           | 19  |

| Section 3  | Instruction Set                                     |     |

| Table 3.1  | Execution Order of Delayed Branch Instructions      | 23  |

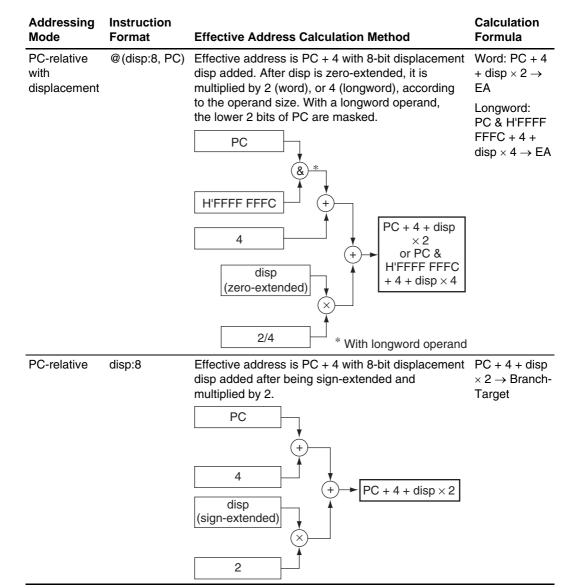

| Table 3.2  | Addressing Modes and Effective Addresses            | 25  |

| Table 3.3  | Notation Used in Instruction List                   | 29  |

| Table 3.4  | Fixed-Point Transfer Instructions                   | 31  |

| Table 3.5  | Arithmetic Operation Instructions                   | 33  |

| Table 3.6  | Logic Operation Instructions                        | 35  |

| Table 3.7  | Shift Instructions                                  | 36  |

| Table 3.8  | Branch Instructions                                 | 37  |

| Table 3.9  | System Control Instructions                         | 37  |

| Table 3.10 | Floating-Point Single-Precision Instructions        | 40  |

| Table 3.11 | Floating-Point Double-Precision Instructions        | 41  |

| Table 3.12 | Floating-Point Control Instructions                 | 41  |

| Table 3.13 | Floating-Point Graphics Acceleration Instructions   | 42  |

| Section 4  | Pipelining                                          |     |

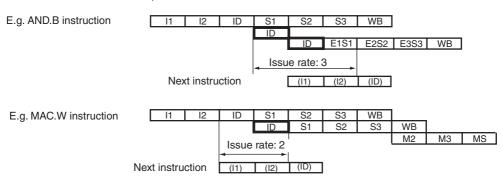

| Table 4.1  | Representations of Instruction Execution Patterns   | 44  |

| Table 4.2  | Instruction Groups                                  | 54  |

| Table 4.3  | Combination of Preceding and Following Instructions | 55  |

| Table 4.4  | Issue Rates and Execution Cycles                    | 57  |

| Section 5  | <b>Exception Handling</b>                           |     |

| Table 5.1  | Register Configuration                              | 65  |

| Table 5.2  | States of Register in Each Operating Mode           | 65  |

| Table 5.3  | Exceptions                                          | 70  |

| Section 6  | Floating-Point Unit (FPU)                           |     |

| Table 6.1  | Floating-Point Number Formats and Parameters        | 99  |

| Table 6.2  | Floating-Point Ranges                               | 100 |

| Table 6.3  | Bit Allocation for FPU Exception Handling           | 107 |

| Section 7  | Memory Management Unit (MMU)                        |     |

| Table 7.1  | Register Configuration                              |     |

| Table 7.2  | Register States in Each Processing State            | 121 |

| Section 8 | Caches                                            |     |

|-----------|---------------------------------------------------|-----|

| Table 8.1 | Cache Features                                    | 159 |

| Table 8.2 | Store Queue Features                              | 159 |

| Table 8.3 | Register Configuration                            | 162 |

| Table 8.4 | Register States in Each Processing State          | 162 |

| Section 9 | L Memory                                          |     |

| Table 9.1 | L Memory Addresses                                | 187 |

| Table 9.2 | Register Configuration                            | 188 |

| Table 9.3 | Register Status in Each Processing State          | 188 |

| Table 9.4 | Protective Function Exceptions to Access L Memory | 199 |

| Appendix  |                                                   |     |

| Table D.1 | Register Configuration                            | 435 |

# Section 1 Overview

## 1.1 Features

The SH-4A is a 32-bit RISC (reduced instruction set computer) microprocessor that is upward compatible with the SH-1, SH-2, SH-3, and SH-4 microcomputers at instruction set code level. Its 16-bit fixed-length instruction set enables program code size to be reduced by almost 50% compared with 32-bit instructions. The features of the SH-4A are listed in table 1.1.

#### Table 1.1 Features

| Item | Features                                                                                                                 |

|------|--------------------------------------------------------------------------------------------------------------------------|

| CPU  | Renesas Technology original architecture                                                                                 |

|      | 32-bit internal data bus                                                                                                 |

|      | General-register files:                                                                                                  |

|      | <ul> <li>Sixteen 32-bit general registers (eight 32-bit shadow registers)</li> </ul>                                     |

|      | <ul> <li>Seven 32-bit control registers</li> </ul>                                                                       |

|      | Four 32-bit system registers                                                                                             |

|      | <ul> <li>RISC-type instruction set (upward compatible with the SH-1, SH-2, SH-3,<br/>and SH-4 microcomputers)</li> </ul> |

|      | <ul> <li>Instruction length: 16-bit fixed length for improved code efficiency</li> </ul>                                 |

|      | <ul> <li>Load/store architecture</li> </ul>                                                                              |

|      | <ul> <li>Delayed branch instructions</li> </ul>                                                                          |

|      | <ul> <li>Instructions executed with conditions</li> </ul>                                                                |

|      | <ul> <li>Instruction set based on the C language</li> </ul>                                                              |

|      | <ul> <li>Super scalar which executes two instructions simultaneously including the<br/>FPU</li> </ul>                    |

|      | <ul> <li>Instruction execution time: Two instructions per cycle (max)</li> </ul>                                         |

|      | Virtual address space: 4 Gbytes                                                                                          |

|      | <ul> <li>Space identifier ASID: 8 bits, 256 virtual address spaces</li> </ul>                                            |

|      | On-chip multiplier                                                                                                       |

|      | Seven-stage pipeline                                                                                                     |

| Item                               | Features                                                                                                                   |  |  |  |  |  |  |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Floatingpoint unit                 | On-chip floating-point coprocessor                                                                                         |  |  |  |  |  |  |

| (FPU)                              | • Supports single-precision (32 bits) and double-precision (64 bits)                                                       |  |  |  |  |  |  |

|                                    | Supports IEEE754-compliant data types and exceptions                                                                       |  |  |  |  |  |  |

|                                    | Two rounding modes: Round to Nearest and Round to Zero                                                                     |  |  |  |  |  |  |

|                                    | Handling of denormalized numbers: Truncation to zero or interrupt<br>generation for IEEE754 compliance                     |  |  |  |  |  |  |

|                                    | Floating-point registers: 32 bits × 16 words × 2 banks                                                                     |  |  |  |  |  |  |

|                                    | (single-precision $\times$ 16 words or double-precision $\times$ 8 words) $\times$ 2 banks                                 |  |  |  |  |  |  |

|                                    | 32-bit CPU-FPU floating-point communication register (FPUL)                                                                |  |  |  |  |  |  |

|                                    | Supports FMAC (multiply-and-accumulate) instruction                                                                        |  |  |  |  |  |  |

|                                    | Supports FDIV (divide) and FSQRT (square root) instructions                                                                |  |  |  |  |  |  |

|                                    | Supports FLDI0/FLDI1 (load constant 0/1) instructions                                                                      |  |  |  |  |  |  |

|                                    | Instruction execution times                                                                                                |  |  |  |  |  |  |

|                                    | <ul> <li>Latency (FADD/FSUB): 3 cycles (single-precision), 5 cycles (double-precision)</li> </ul>                          |  |  |  |  |  |  |

|                                    | <ul> <li>Latency (FMAC/ FMUL): 5 cycles (single-precision), 7 cycles (double-precision)</li> </ul>                         |  |  |  |  |  |  |

|                                    | <ul> <li>Pitch (FADD/FSUB): 1 cycle (single-precision/double-precision)</li> </ul>                                         |  |  |  |  |  |  |

|                                    | <ul> <li>Pitch (FMAC/FMUL): 1 cycle (single-precision), 3 cycles (double-precision)</li> </ul>                             |  |  |  |  |  |  |

|                                    | Note: FMAC is supported for single-precision only.                                                                         |  |  |  |  |  |  |

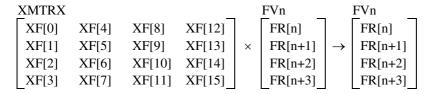

|                                    | • 3-D graphics instructions (single-precision only):                                                                       |  |  |  |  |  |  |

|                                    | <ul> <li>4-dimensional vector conversion and matrix operations (FTRV): 4 cycles<br/>(pitch), 8 cycles (latency)</li> </ul> |  |  |  |  |  |  |

|                                    | <ul> <li>4-dimensional vector (FIPR) inner product: 1 cycle (pitch), 5 cycles<br/>(latency)</li> </ul>                     |  |  |  |  |  |  |

|                                    | Ten-stage pipeline                                                                                                         |  |  |  |  |  |  |

| Memory<br>management<br>unit (MMU) | 4 Gbytes of physical address space, 256 address space identifiers (address space identifier ASID: 8 bits)                  |  |  |  |  |  |  |

| unit (iviivio)                     | Supports single virtual memory mode and multiple virtual memory mode                                                       |  |  |  |  |  |  |

|                                    | • Supports multiple page sizes: 1 Kbyte, 4 Kbytes, 64 Kbytes, or 1 Mbyte                                                   |  |  |  |  |  |  |

|                                    | 4-entry full associative TLB for instructions                                                                              |  |  |  |  |  |  |

|                                    | 64-entry full associative TLB for instructions and operands                                                                |  |  |  |  |  |  |

|                                    | <ul> <li>Supports software selection of replacement method and random-counter<br/>replacement algorithms</li> </ul>        |  |  |  |  |  |  |

|                                    | Contents of TLB are directly accessible through address mapping                                                            |  |  |  |  |  |  |

| ltem         | Features                                                                                                   |

|--------------|------------------------------------------------------------------------------------------------------------|

| Cache memory | Instruction cache (IC)                                                                                     |

|              | <ul> <li>4-way set associative</li> </ul>                                                                  |

|              | <ul> <li>32-byte block length</li> </ul>                                                                   |

|              | Operand cache (OC)                                                                                         |

|              | <ul> <li>4-way set associative</li> </ul>                                                                  |

|              | <ul> <li>32-byte block length</li> </ul>                                                                   |

|              | <ul> <li>Selectable write method (copy-back or write-through)</li> </ul>                                   |

|              | <ul> <li>Storage queue (32 bytes × 2 entries)</li> </ul>                                                   |

|              | Note: For the size of instruction cash and operand cash, see corresponding hardware manual on the product. |

| L memory     | Two independent read/write ports                                                                           |

|              | <ul> <li>8-/16-/32-/64-bit access from the CPU</li> </ul>                                                  |

|              | <ul> <li>8-/16-/32-/64-bit and 16-/32-byte access from the external devices</li> </ul>                     |

|              | Note: For the size of L memory, see the hardware manual of the target product.                             |

# 1.2 Changes from SH-4 to SH-4A

Table 1.2 summarizes the changes from SH-4 to SH-4A based on the sections and sub-sections in this manual.

Table 1.2 Changes from SH-4 to SH-4A

| Section No. and Name    | Sub-<br>section                | Sub-section<br>Name                                  | Changes                                                                                          |  |  |

|-------------------------|--------------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|--|

| 1. Overview             | _                              | _                                                    | Modified entirely                                                                                |  |  |

|                         |                                |                                                      | (Detailed differences are described in the following sections).                                  |  |  |

| 2. Programming<br>Model | 2.2                            | Register<br>Descriptions                             | The operations in SZ=1 and PR=1 are added to the floating point status/control register (FPSCR). |  |  |

| 3. Instruction Set      | 3.3                            | Instruction Set                                      | 9 instructions are added as CPU instructions.                                                    |  |  |

|                         |                                |                                                      | 3 instructions are added as FPU instructions.                                                    |  |  |

| 4. Pipelining           | 4.1                            | Pipelines                                            | The number of stages in the pipeline is changed from five to seven.                              |  |  |

|                         | 4.2 Parallel-<br>Executability |                                                      | 9 instructions are added as CPU instructions.                                                    |  |  |

|                         |                                |                                                      | 3 instructions are added as FPU instructions.                                                    |  |  |

|                         |                                |                                                      | Instruction group and parallel execution combinations are modified.                              |  |  |

|                         | 4.3                            | Execution Cycles                                     | The number of execution cycles is modified.                                                      |  |  |

| 5. Exception Handling   | _                              | _                                                    | _                                                                                                |  |  |

| 6. FPU                  | 6.3.2                          | Floating-Point<br>Status/Control<br>Register (FPSCR) | Operations in SZ = 1 and PR = 1 and each endian are added                                        |  |  |

|                         | 6.5                            | Floating-Point<br>Exceptions                         | Specification of FPU exception detection condition with FPU exception enabled is changed.        |  |  |

| Section No. and<br>Name | Sub-<br>section | Sub-section<br>Name                                                        | Changes                                                                                                                                |  |  |  |  |

|-------------------------|-----------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7. Memory               | 7.1.1           | Address Spaces                                                             | Area P4 configuration is modified.                                                                                                     |  |  |  |  |

| Management Unit         |                 |                                                                            | On-chip RAM space is deleted.                                                                                                          |  |  |  |  |

|                         | 7.2             | Register<br>Descriptions                                                   | The page table entry assist register (PTEA) is deleted.                                                                                |  |  |  |  |

|                         |                 |                                                                            | A physical address space control register is added.                                                                                    |  |  |  |  |

|                         | 7.2.6           | Physical Address<br>Space Control<br>Register (PASCR)                      | Newly added                                                                                                                            |  |  |  |  |

|                         | 7.2.7           | Instruction Re-<br>Fetch Inhibit<br>Control Register<br>(IRMCR)            | Newly added.                                                                                                                           |  |  |  |  |

|                         | 7.3             | TLB Functions                                                              | Space attribute bits (SA [2:0]) and timing control bit (TC) are deleted from the TLB.                                                  |  |  |  |  |

|                         | 7.4.5           | Avoiding Synonym<br>Problems                                               | The corresponding bits are modified according to the cache size change and the index mode deletion.                                    |  |  |  |  |

|                         | 7.5.1,<br>7.5.4 | Instruction TLB Multiple Hit Exception and Data TLB Multiple Hit Exception | Multiple hits during the UTLB search caused by ITLB mishandling are changed to be handled as a TLB multiple hit instruction exception. |  |  |  |  |

|                         | 7.6             | Memory-Mapped<br>TLB Configuration                                         | Data array 2 in the ITLB and UTLB is deleted.                                                                                          |  |  |  |  |

|                         | 7.6.3           | UTLB Address<br>Array                                                      | Associative writes to the UTLB address array are changed to not generate data TLB multiple hit exceptions.                             |  |  |  |  |

|                         |                 |                                                                            | Memory allocated addresses are changed from H'F6000000–H'F6FFFFF to H'F6000000–H'F60FFFFF.                                             |  |  |  |  |

|                         | 7.6.4           | UTLB Data Array                                                            | Memory allocated addresses are changed from H'F7000000–H'F77FFFFF to H'F7000000–H'F70FFFFF.                                            |  |  |  |  |

|                         | 7.7             | 32-Bit Address<br>Extended Mode                                            | Newly added.                                                                                                                           |  |  |  |  |

| Section No. and<br>Name      | Sub-<br>section | Sub-section<br>Name                                  | Changes                                                                                                                       |

|------------------------------|-----------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| 8. Caches                    | 8.1             | Features                                             | Instruction cache capacity is changed to 32 Kbytes.                                                                           |

|                              |                 |                                                      | The caching method is changed to a 4-way set-associative method.                                                              |

|                              | 8.2             | Register<br>Descriptions                             | An on-chip memory control register is added.                                                                                  |

|                              | 8.2.1           | Cache Control                                        | Modified.                                                                                                                     |

|                              |                 | Register (CCR)                                       | (Descriptions in CCR are modified.)                                                                                           |

|                              | 8.2.4           | On-Chip Memory<br>Control Register<br>(RAMCR)        | Newly added.                                                                                                                  |

|                              | 8.3             | Operand Cache<br>Operation                           | RAM mode and OC index mode are deleted.                                                                                       |

|                              | 8.3.6           | OC Two-Way<br>Mode                                   | Newly added.                                                                                                                  |

|                              | 8.4             | Instruction Cache<br>Operation                       | IC index mode is deleted.                                                                                                     |

|                              | 8.4.3           | IC Two-Way Mode                                      | Newly added.                                                                                                                  |

|                              | 8.5.1           | Coherency<br>between Cache<br>and External<br>Memory | The ICBI, PREFI, and SYNCO instructions are added.                                                                            |

|                              | 8.6             | Memory-Mapped<br>Cache<br>Configuration              | The entry bits and the way bits are modified according to the size modification and changed into 4-way set associative cache. |

|                              | 8.8             | Notes on Using<br>32-Bit Address<br>Extended Mode    | Newly added.                                                                                                                  |

| 9. L Memory                  | _               | _                                                    | Newly added.                                                                                                                  |

| 10. Instruction Descriptions | _               | _                                                    | 9 instructions are added as CPU instructions.                                                                                 |

|                              |                 |                                                      | 3 instructions are added as FPU instructions.                                                                                 |

# Section 2 Programming Model

The programming model of the SH-4A is explained in this section. The SH-4A has registers and data formats as shown below.

# 2.1 Data Formats

The data formats supported in the SH-4A are shown in figure 2.1.

Figure 2.1 Data Formats

# 2.2 Register Descriptions

## 2.2.1 Privileged Mode and Banks

**Processing Modes:** This LSI has two processing modes, user mode and privileged mode. This LSI normally operates in user mode, and switches to privileged mode when an exception occurs or an interrupt is accepted. There are four kinds of registers—general registers, system registers, control registers, and floating-point registers—and the registers that can be accessed differ in the two processing modes.

**General Registers:** There are 16 general registers, designated R0 to R15. General registers R0 to R7 are banked registers which are switched by a processing mode change.

### · Privileged mode

In privileged mode, the register bank bit (RB) in the status register (SR) defines which banked register set is accessed as general registers, and which set is accessed only through the load control register (LDC) and store control register (STC) instructions.

When the RB bit is 1 (that is, when bank 1 is selected), the 16 registers comprising bank 1 general registers R0\_BANK1 to R7\_BANK1 and non-banked general registers R8 to R15 can be accessed as general registers R0 to R15. In this case, the eight registers comprising bank 0 general registers R0\_BANK0 to R7\_BANK0 are accessed by the LDC/STC instructions. When the RB bit is 0 (that is, when bank 0 is selected), the 16 registers comprising bank 0 general registers R0\_BANK0 to R7\_BANK0 and non-banked general registers R8 to R15 can be accessed as general registers R0 to R15. In this case, the eight registers comprising bank 1 general registers R0\_BANK1 to R7\_BANK1 are accessed by the LDC/STC instructions.

#### User mode

In user mode, the 16 registers comprising bank 0 general registers R0\_BANK0 to R7\_BANK0 and non-banked general registers R8 to R15 can be accessed as general registers R0 to R15. The eight registers comprising bank 1 general registers R0\_BANK1 to R7\_BANK1 cannot be accessed.