# IEEE Standard for Property Specification Language (PSL)

## **IEEE Computer Society**

Sponsored by the Design Automation Standards Committee

and the IEEE Standards Association Corporate Advisory Group

IEEE 3 Park Avenue New York, NY 10016-5997, USA

6 April 2010

IEEE Std 1850™-2010

(Revision of IEEE Std1850-2005)

(Revision of IEEE Std1850-2005)

## IEEE Standard for Property Specification Language (PSL)

Sponsor

**Design Automation Standards Committee** of the **IEEE Computer Society**

and the IEEE Standards Association Corporate Advisory Group

Approved 25 March 2010 IEEE-SA Standards Board

Grateful acknowledgment is made to Accellera Organization, Inc. for the permission to use the following source material:

Accellera Property Specification Language Reference Manual (version 1.1), Accellera

GDL: General Description Language, Accellera, Mar. 2005

Abstract: The IEEE Property Specification Language (PSL) is defined. PSL is a formal notation for specification of electronic system behavior, compatible with multiple electronic system design languages, including IEEE Std 1076™ (VHDL®), IEEE Std 1354 (Verilog®), IEEE Std 1666™ (SystemC®), and IEEE Std 1800™ (SystemVerilog®), thereby enabling a common specification and verification flow for multi-language and mixed-language designs. PSL captures design intent in a form suitable for simulation, formal verification, formal analysis, and hybrid verification tools. PSL enhances communication among architects, designers, and verification engineers to increase productivity throughout the design and verification process. The primary audiences for this standard are the implementors of tools supporting the language and advanced users of the language.

**Keywords:** ABV, assertion, assertion-based verification, assumption, cover, model checking, property, PSL, specification, temporal logic, verification

The Institute of Electrical and Electronics Engineers, Inc. 3 Park Avenue, New York, NY 10016-5997, USA

Copyright © 2010 by the Institute of Electrical and Electronics Engineers, Inc. All rights reserved. Published 6 April 2010. Printed in the United States of America.

IEEE, 802, and POSIX are registered trademarks in the U.S. Patent & Trademark Office, owned by The Institute of Electrical and Electronics Engineers, Incorporated.

VHDL and Verilog are both registered trademarks of Cadence Design Systems, Inc.

SystemVerilog is a registered trademark of Accellera Organization, Inc.

SystemC is a registered trademark of Synopsys, Inc.

PDF: ISBN 978-0-7381-6255-3 STD96063 Print: ISBN 978-0-7381-6256-0 STDPD96063

IEEE prohibits discrimination, harassment, and bullying. For more information, visit <a href="http://www.ieee.org/web/aboutus/whatis/policies/p9-26.html">http://www.ieee.org/web/aboutus/whatis/policies/p9-26.html</a>.

No part of this publication may be reproduced in any form, in an electronic retrieval system or otherwise, without the prior written permission of the publisher.

**IEEE Standards** documents are developed within the IEEE Societies and the Standards Coordinating Committees of the IEEE Standards Association (IEEE-SA) Standards Board. The IEEE develops its standards through a consensus development process, approved by the American National Standards Institute, which brings together volunteers representing varied viewpoints and interests to achieve the final product. Volunteers are not necessarily members of the Institute and serve without compensation. While the IEEE administers the process and establishes rules to promote fairness in the consensus development process, the IEEE does not independently evaluate, test, or verify the accuracy of any of the information or the soundness of any judgments contained in its standards.

Use of an IEEE Standard is wholly voluntary. The IEEE disclaims liability for any personal injury, property or other damage, of any nature whatsoever, whether special, indirect, consequential, or compensatory, directly or indirectly resulting from the publication, use of, or reliance upon this, or any other IEEE Standard document.

The IEEE does not warrant or represent the accuracy or content of the material contained herein, and expressly disclaims any express or implied warranty, including any implied warranty of merchantability or fitness for a specific purpose, or that the use of the material contained herein is free from patent infringement. IEEE Standards documents are supplied "AS IS."

The existence of an IEEE Standard does not imply that there are no other ways to produce, test, measure, purchase, market, or provide other goods and services related to the scope of the IEEE Standard. Furthermore, the viewpoint expressed at the time a standard is approved and issued is subject to change brought about through developments in the state of the art and comments received from users of the standard. Every IEEE Standard is subjected to review at least every five years for revision or reaffirmation, or every ten years for stabilization. When a document is more than five years old and has not been reaffirmed, or more than ten years old and has not been stabilized, it is reasonable to conclude that its contents, although still of some value, do not wholly reflect the present state of the art. Users are cautioned to check to determine that they have the latest edition of any IEEE Standard.

In publishing and making this document available, the IEEE is not suggesting or rendering professional or other services for, or on behalf of, any person or entity. Nor is the IEEE undertaking to perform any duty owed by any other person or entity to another. Any person utilizing this, and any other IEEE Standards document, should rely upon the advice of a competent professional in determining the exercise of reasonable care in any given circumstances.

Interpretations: Occasionally questions may arise regarding the meaning of portions of standards as they relate to specific applications. When the need for interpretations is brought to the attention of IEEE, the Institute will initiate action to prepare appropriate responses. Since IEEE Standards represent a consensus of concerned interests, it is important to ensure that any interpretation has also received the concurrence of a balance of interests. For this reason, IEEE and the members of its societies and Standards Coordinating Committees are not able to provide an instant response to interpretation requests except in those cases where the matter has previously received formal consideration. A statement, written or oral, that is not processed in accordance with the IEEE-SA Standards Board Operations Manual shall not be considered the official position of IEEE or any of its committees and shall not be considered to be, nor be relied upon as, a formal interpretation of the IEEE. At lectures, symposia, seminars, or educational courses, an individual presenting information on IEEE standards shall make it clear that his or her views should be considered the personal views of that individual rather than the formal position, explanation, or interpretation of the IEEE. Comments for revision of IEEE Standards are welcome from any interested party, regardless of membership affiliation with IEEE. Suggestions for changes in documents should be in the form of a proposed change of text, together with appropriate supporting comments. Recommendations to change the status of a stabilized standard should include a rationale as to why a revision or withdrawal is required.

Comments and recommendations on standards, and requests for interpretations should be addressed to:

Secretary, IEEE-SA Standards Board 445 Hoes Lane Piscataway, NJ 08854 USA

Authorization to photocopy portions of any individual standard for internal or personal use is granted by the Institute of Electrical and Electronics Engineers, Inc., provided that the appropriate fee is paid to Copyright Clearance Center. To arrange for payment of licensing fee, please contact Copyright Clearance Center, Customer Service, 222 Rosewood Drive, Danvers, MA 01923 USA; +1 978 750 8400. Permission to photocopy portions of any individual standard for educational classroom use can also be obtained through the Copyright Clearance Center.

## Introduction

This introduction is not part of IEEE Std 1850-2010, IEEE Standard for Property Specification Language (PSL).

IEEE Std 1850 Property Specification Language (PSL) is based upon the Accellera Property Specification Language (Accellera PSL), a language for formal specification of electronic system behavior, which was developed by Accellera, a consortium of Electronic Design Automation (EDA), semiconductor, and system companies. IEEE Std 1850 PSL 2010 refines IEEE Std 1850 PSL 2005 by providing extensions for improved verification IP reuse (e.g., the vpkg type of vunit) and interaction between the assertions and the simulation environment (local variables), and by addressing minor technical issues. The formal semantics were updated to reflect these changes.

#### Notice to users

## Laws and regulations

Users of these documents should consult all applicable laws and regulations. Compliance with the provisions of this standard does not imply compliance to any applicable regulatory requirements. Implementers of the standard are responsible for observing or referring to the applicable regulatory requirements. IEEE does not, by the publication of its standards, intend to urge action that is not in compliance with applicable laws, and these documents may not be construed as doing so.

## Copyrights

This document is copyrighted by the IEEE. It is made available for a wide variety of both public and private uses. These include both use, by reference, in laws and regulations, and use in private self-regulation, standardization, and the promotion of engineering practices and methods. By making this document available for use and adoption by public authorities and private users, the IEEE does not waive any rights in copyright to this document.

## **Updating of IEEE documents**

Users of IEEE standards should be aware that these documents may be superseded at any time by the issuance of new editions or may be amended from time to time through the issuance of amendments, corrigenda, or errata. An official IEEE document at any point in time consists of the current edition of the document together with any amendments, corrigenda, or errata then in effect. In order to determine whether a given document is the current edition and whether it has been amended through the issuance of amendments, corrigenda, or errata, visit the IEEE Standards Association website at <a href="http://ieeexplore.ieee.org/xpl/standards.jsp">http://ieeexplore.ieee.org/xpl/standards.jsp</a>, or contact the IEEE at the address listed previously.

For more information about the IEEE Standards Association or the IEEE standards development process, visit the IEEE-SA website at http://standards.ieee.org.

#### **Errata**

Errata, if any, for this and all other standards can be accessed at the following URL: http://standards.ieee.org/reading/ieee/updates/errata/index.html. Users are encouraged to check this URL for errata periodically.

Copyright ©2010 IEEE. All rights reserved.

#### Interpretations

Current interpretations can be accessed at the following URL: http://standards.ieee.org/reading/ieee/interp/index.html.

#### **Patents**

Attention is called to the possibility that implementation of this amendment may require use of subject matter covered by patent rights. By publication of this standard, no position is taken with respect to the existence or validity of any patent rights in connection therewith. The IEEE is not responsible for identifying Essential Patent Claims for which a license may be required, for conducting inquiries into the legal validity or scope of Patents Claims or determining whether any licensing terms or conditions provided in connection with submission of a Letter of Assurance, if any, or in any licensing agreements are reasonable or non-discriminatory. Users of this amendment are expressly advised that determination of the validity of any patent rights, and the risk of infringement of such rights, is entirely their own responsibility. Further information may be obtained from the IEEE Standards Association.

## **Participants**

At the time this standard was submitted to the IEEE-SA for approval, the IEEE P1850 PSL Working Group had the following membership:

Harry Foster, Accellera, Chair Sitvanit Ruah, IBM, Co-Chair N. S. Subramanian, Cadence, Secretary Anne Lustig-Picus, IBM, Editor Hanan Singer, IBM, Editor

Mohamed-Lyes Benalycherif, ST-Ericsson

Surrendra Dudani, Synopsys

Johan Mårtensson, Jasper DA

Avigail Orni, IBM

Dana Fisman, IBM

Dmitry Pidan, IBM

Sandeep Gupta, Cadence

Joseph Lu, Altera

Sami Maisnemi, Nokia

Erich Marschner, Cadence

Johan Mårtensson, Jasper DA

Avigail Orni, IBM

Dmitry Pidan, IBM

Tej Singh, Mentor Graphics

Richard Wallace, Northrop Grumman

Yaron Wolfsthal, IBM

The following members of the entity balloting committee voted on this standard. Balloters may have voted for approval, disapproval, or abstention.

Accelera IBM Mentor Graphics Cadence Design Synopsys The working group gratefully acknowledges the contributions of the following organizations and participants. Without their assistance and dedication, the initial standard would not have been completed.

| Organization         | Participant                  |

|----------------------|------------------------------|

| Accellera            | Harry Foster, Chair          |

| Altraverifica Ltd.   | Adriana Maggiore             |

| Cadence              | Sandeep Gupta                |

|                      | Makarand Joshi               |

|                      | Erich Marschner              |

|                      | N. S. Subramanian, Secretary |

|                      | Stephen Ward                 |

| IBM                  | Cindy Eisner                 |

|                      | Dana Fisman                  |

|                      | Anne Lustig-Picus, Editor    |

|                      | Avigail Orni                 |

|                      | Dmitry Pidan                 |

|                      | Sitvanit Ruah, Co-chair      |

|                      | Hanan Singer, Editor         |

|                      | Yaron Wolfsthal              |

| Infineon             | Klaus Winkelmann             |

| Intel                | Alex Levin                   |

| Jasper DA            | Johan Alfredsson             |

|                      | Johan Mårtensson             |

| Mentor Graphics      | Stephen Bailey               |

|                      | Andrew Seawright             |

|                      | Tej Singh                    |

| Nokia                | Jari Kalinainen              |

|                      | Sami Maisnemi                |

| Northrop Grumman     | Richard Wallace              |

| Novas Software, Inc. | Bassam Tabbara               |

| NVidia               | Joseph Lu                    |

| Phillips             | Sylvain Boucher              |

| ST Microelectronics  | Mohamed-Lyes Benalycherif    |

|                      | Andrea Fedeli                |

| Sun Microsystems     | Tom Thatcher                 |

| Synopsys             | Surrendra Dudani             |

When the IEEE-SA Standards Board approved this standard on 25 March 2010, it had the following membership:

Robert M. Grow, Chair Richard H. Hulett, Vice Chair Steve M. Mills, Past Chair Judith Gorman, Secretary

John Barr Karen Bartleson Victor Berman Ted Burse Richard DeBlasio Andy Drozd Mark Epstein Alexander Gelman Jim Hughes Young Kyun Kim Joseph L. Koepfinger\* John Kulick David J. Law Ted Olsen Glenn Parsons Ronald C. Petersen Narayanan Ramachandran Jon Walter Rosdahl Sam Sciacca

Also included are the following nonvoting IEEE-SA Standards Board liaisons:

Howard L. Wolfman, TAB Representative Michael Janezic, NIST Representative Satish K. Aggarwal, NRC Representative

Michelle Turner

IEEE Standards Program Manager, Document Development

Michael Kipness

IEEE Standards Program Manager, Technical Program Development

<sup>\*</sup>Member Emeritus

## **Contents**

| 1. | Ove           | erview.                                  |                                            | 1  |  |

|----|---------------|------------------------------------------|--------------------------------------------|----|--|

|    | 1.1           | Scope                                    | 2                                          | 1  |  |

|    |               |                                          | ose                                        |    |  |

|    |               | 1.2.1                                    | Background                                 |    |  |

|    |               | 1 2 2                                    | e                                          |    |  |

|    |               | 1.2.3                                    |                                            |    |  |

|    | 1 3           |                                          | 2                                          |    |  |

|    | 1.5           | 1.3.1                                    |                                            |    |  |

|    |               |                                          | Functional specification                   |    |  |

| 2. | Nor           | mative                                   | references                                 | 7  |  |

| 3. | Def           | Definitions, acronyms, and abbreviations |                                            |    |  |

|    | 3 1           | Defin                                    | itions                                     | Q  |  |

|    |               |                                          |                                            |    |  |

|    |               |                                          | nyms and abbreviationsal terms             |    |  |

|    | 3.3           | Specia                                   | ai ternis                                  | 12 |  |

| 4. | Org           | anizati                                  | on                                         | 15 |  |

|    | 4.1           | Abstra                                   | act structure                              | 15 |  |

|    |               | 4.1.1                                    | Layers                                     |    |  |

|    |               | 4.1.2                                    | Flavors                                    |    |  |

|    | 4.2           | Lexic                                    | al structure                               | 16 |  |

|    |               | 4.2.1                                    | Identifiers                                | 16 |  |

|    |               | 4.2.2                                    |                                            |    |  |

|    |               | 4.2.3                                    |                                            |    |  |

|    |               | 4.2.4                                    | 1                                          |    |  |

|    |               | 4.2.5                                    |                                            |    |  |

|    | 4.3 Syntax    |                                          |                                            |    |  |

|    |               | 4.3.1                                    |                                            |    |  |

|    |               |                                          | HDL dependencies                           |    |  |

|    | 4.4 Semantics |                                          |                                            |    |  |

|    | 7.7           | 4.4.1                                    | Clocked vs. unclocked evaluation           |    |  |

|    |               | 4.4.2                                    |                                            |    |  |

|    |               | 4.4.3                                    |                                            |    |  |

|    |               | 4.4.4                                    | Simple subset                              |    |  |

|    |               | 4.4.5                                    | Finite-length vs. infinite-length behavior |    |  |

|    |               | 4.4.5                                    | The concept of strength                    |    |  |

| 5. | Boo           | olean la                                 | ıyer                                       |    |  |

|    |               |                                          | •                                          |    |  |

|    | 5.1           |                                          | ession type classes                        |    |  |

|    |               | 5.1.1                                    | Bit expressions                            |    |  |

|    |               | 5.1.2                                    | Boolean expressions                        |    |  |

|    |               | 5.1.3                                    | BitVector expressions                      |    |  |

|    |               | 5.1.4                                    | - · · · - · · · · · · · · · · · · · · ·    |    |  |

|    |               | 5.1.5                                    | String expressions                         |    |  |

|    | 5.2           |                                          | ession forms                               |    |  |

|    |               | 5.2.1                                    | HDL expressions                            | 36 |  |

|       |                | 5.2.2              | PSL expressions                                                           |     |

|-------|----------------|--------------------|---------------------------------------------------------------------------|-----|

|       |                | 5.2.3              | Built-in functions                                                        |     |

|       |                | 5.2.4              | Union expressions                                                         | 45  |

|       | 5.3            | Clock              | expressions                                                               | 45  |

|       | 5.4            | Defau              | lt clock declaration                                                      | 47  |

| 6.    | Ten            | nporal l           | ayer                                                                      | 49  |

|       | 6.1            | Seque              | ntial expressions                                                         | 50  |

|       |                | 6.1.1              | Sequential Extended Regular Expressions (SEREs)                           | 50  |

|       |                | 6.1.2              | Sequences                                                                 |     |

|       | 6.2            | Proper             | rties                                                                     |     |

|       |                | 6.2.1              | FL properties                                                             |     |

|       |                | 6.2.2              | Optional Branching Extension (OBE) properties                             |     |

|       |                | 6.2.3              | Replicated properties                                                     |     |

|       | 6.3            |                    | variables                                                                 |     |

|       |                |                    | dural blocks                                                              |     |

|       |                |                    | rty and sequence declarations                                             |     |

|       | 0.5            | 6.5.1              | *                                                                         |     |

|       |                | 6.5.2              |                                                                           |     |

|       |                | • • • • •          |                                                                           |     |

|       |                | 6.5.3              | Instantiation                                                             | 107 |

| 7.    | Ver            | Verification layer |                                                                           |     |

|       | 7.1            | Verifi             | cation directives                                                         | 111 |

|       |                | 7.1.1              | assert                                                                    | 111 |

|       |                | 7.1.2              | assume                                                                    | 112 |

|       |                | 7.1.3              | restrict                                                                  | 113 |

|       |                | 7.1.4              | restrict!                                                                 | 113 |

|       |                | 7.1.5              | cover                                                                     | 115 |

|       |                | 7.1.6              | fairness and strong_fairness                                              |     |

|       | 7.2            |                    | cation units                                                              |     |

|       | ,              | 7.2.1              | Verification unit binding.                                                |     |

|       |                | 7.2.2              | Verification unit instantiation                                           |     |

|       |                | 7.2.3              | Verification unit inheritance                                             |     |

|       |                | 7.2.3              | Overriding assignments                                                    |     |

|       |                |                    |                                                                           |     |

| 8.    | Modeling layer |                    |                                                                           | 129 |

|       | 8.1            | Intege             | r ranges                                                                  | 129 |

|       |                | _                  | ures                                                                      |     |

| 9.    | Sco            | pe and             | visibility rules                                                          | 131 |

|       | 9 1            | Imme               | diate scope                                                               | 131 |

|       |                |                    | ded scope                                                                 |     |

|       |                |                    | and indirect name references                                              |     |

|       |                |                    |                                                                           |     |

| Annex | A (r           | ormati             | ve) Syntax rule summary                                                   |     |

| Annex | В (1           | normati            | ive) Formal Syntax and Semantics of IEEE Std 1850 Property Specific (PSL) |     |

|       |                |                    |                                                                           |     |

| Annex | : C (i         | nformat            | tive) Bibliography                                                        | 167 |

## IEEE Standard for Property Specification Language (PSL)

IMPORTANT NOTICE: This standard is not intended to ensure safety, security, health, or environmental protection in all circumstances. Implementers of the standard are responsible for determining appropriate safety, security, environmental, and health practices or regulatory requirements.

This IEEE document is made available for use subject to important notices and legal disclaimers. These notices and disclaimers appear in all publications containing this document and may be found under the heading "Important Notice" or "Important Notices and Disclaimers Concerning IEEE Documents." They can also be obtained on request from IEEE or viewed at <a href="http://standards.ieee.org/IPR/disclaimers.html">http://standards.ieee.org/IPR/disclaimers.html</a>.

## 1. Overview

#### 1.1 Scope

This standard defines the property specification language (PSL), which formally describes electronic system behavior. This standard specifies the syntax and semantics for PSL and also clarifies how PSL interfaces with various standard electronic system design languages.

## 1.2 Purpose

The purpose of this standard is to provide a well-defined language for formal specification of electronic system behavior, one that is compatible with multiple electronic system design languages, including IEEE Std 1076™ (VHDL®), <sup>1</sup> IEEE Std 1364™ (Verilog®), IEEE Std 1800™ (SystemVerilog®), and IEEE Std 1666™ (SystemC®), to facilitate a common specification and verification flow for multi-language and mixed-language designs.

This standard creates an updated IEEE standard based upon IEEE Std 1850-2005. The updated standard will refine IEEE standard, addressing errata, minor technical issues, and proposed extensions specifically related to property reuse and improved simulation usability.

Copyright © 2010 IEEE. All rights reserved.

1

<sup>&</sup>lt;sup>1</sup>Information on references can be found in Clause 2.

#### 1.2.1 Background

The complexity of Very Large Scale Integration (VLSI) has grown to such a degree that traditional approaches have begun to reach their limitations, and verification costs have reached 60%–70% of development resources. The need for advanced verification methodology, with improved observability of design behavior and improved controllability of the verification process, has become critical. Over the last decade, a methodology based on the notion of "properties" has been identified as a powerful verification paradigm that can assure enhanced productivity, higher design quality, and, ultimately, faster time to market and higher value to engineers and end-users of electronics products. Properties, as used in this context, are concise, declarative, expressive, and unambiguous specifications of desired system behavior that are used to guide the verification process. IEEE 1850 PSL is a standard language for specifying electronic system behavior using properties. PSL facilitates property-based verification using both simulation and formal verification, thereby enabling a productivity boost in functional verification.

#### 1.2.2 Motivation

Ensuring that a design's implementation satisfies its specification is the foundation of hardware verification. Key to the design and verification process is the act of specification. Yet historically, the process of specification has consisted of creating a natural language description of a set of design requirements. This form of specification is both ambiguous and, in many cases, unverifiable due to the lack of a standard machine-executable representation. Furthermore, ensuring that all functional aspects of the specification have been adequately *verified* (that is, covered) is problematic.

The IEEE PSL was developed to address these shortcomings. It gives the design architect a standard means of specifying design properties using a concise syntax with clearly-defined formal semantics. Similarly, it enables the RTL implementer to capture design intent in a verifiable form, while enabling the verification engineer to validate that the implementation satisfies its specification through *dynamic* (that is, simulation) and *static* (that is, formal) verification means. Furthermore, it provides a means to measure the quality of the verification process through the creation of functional coverage models built on formally specified properties. In addition, it provides a standard means for hardware designers and verification engineers to create a rigorous and machine-executable design specification.

#### 1.2.3 Goals

PSL was specifically developed to fulfill the following general hardware functional specification requirements:

- Easy to learn, write, and read

- Concise syntax

- Rigorously well-defined formal semantics

- Expressive power, permitting specifications of a large class of real-world design properties

- Known efficient underlying algorithms in simulation, as well as formal verification

## 1.3 Usage

PSL is a language for the formal specification of hardware. It is used to describe properties that are required to hold in the design under verification. PSL provides a means to write specifications that are both easy to read and mathematically precise. It is intended to be used for functional specification on the one hand and as input to functional verification tools on the other. Thus, a PSL specification is an executable specification of a hardware design.

#### 1.3.1 Functional specification

PSL can be used to capture requirements regarding the overall behavior of a design, as well as assumptions about the environment in which the design is expected to operate. PSL can also capture internal behavioral requirements and assumptions that arise during the design process. Both enable more effective functional verification and reuse of the design.

One important use of PSL is for documentation, either in place of or along with an English specification. A PSL specification can describe simple invariants (for example, signals read\_enable and write\_enable are never asserted simultaneously) as well as multi-cycle behavior (for example, correct behavior of an interface with respect to a bus protocol or correct behavior of pipelined operations).

A PSL specification consists of assertions regarding properties of a design under a set of assumptions. A property is built from three kinds of elements: Boolean expressions, which describe behavior over one cycle; sequential expressions, which can describe multi-cycle behavior; and temporal operators, which describe temporal relationships among Boolean expressions and sequences. For example, consider the following Verilog Boolean expression:

```

ena || enb

```

This expression describes a cycle in which at least one of the signals ena and enb are asserted. The PSL sequential expression

```

{req; ack; !cancel}

```

describes a sequence of cycles, such that req is asserted in the first cycle, ack is asserted in the second cycle, and cancel is deasserted in the third cycle. The following property, obtained by applying the temporal operators always and | => to these expressions,

```

always {req;ack;!cancel} |=> (ena || enb)

```

means that always (that is, in every cycle), if the sequence {req;ack;!cancel} occurs, then either ena or enb is asserted one cycle after the sequence ends. Adding the directive assert as follows:

```

assert always {req;ack;!cancel} |=> (ena || enb);

```

completes the specification, indicating that this property is expected to hold in the design and that this expectation needs to be verified.

#### 1.3.2 Functional verification

PSL can also be used as input to verification tools, for both verification by simulation, as well as formal verification using a model checker or a theorem prover. Each of these is discussed in the subclauses that follow.

#### 1.3.2.1 Simulation

A PSL specification can also be used to automatically generate checks of simulated behavior. This can be done, for example, by directly integrating the checks in the simulation tool; by interpreting PSL properties in a testbench automation tool that drives the simulator; by generating HDL monitors that are simulated alongside the design; or by analyzing the traces produced during simulation.

For instance, the following PSL property:

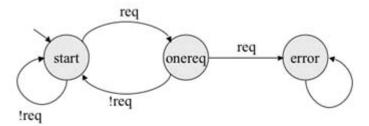

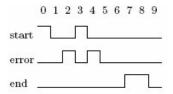

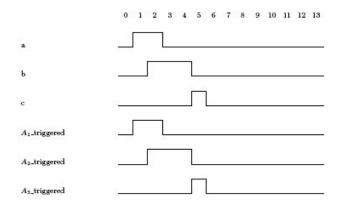

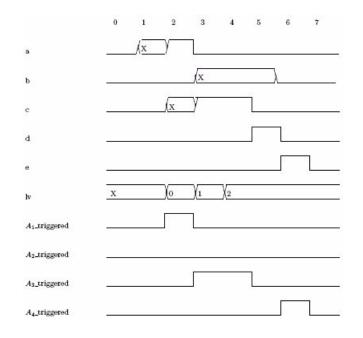

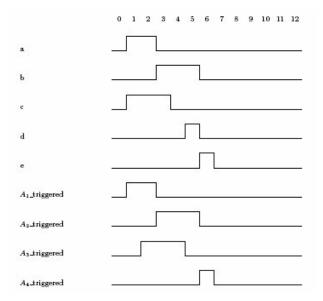

states that signal req is a pulsed signal, i.e., if it is high in some cycle, then it is low in the following cycle. Such a property can be easily checked using a simulation checker written in some HDL that has the functionality of the finite state machine (FSM) shown in Figure 1.

Figure 1—A simple (deterministic) FSM that checks Property 1

For properties more complicated than the property shown in Figure 1, manually writing a corresponding checker is painstaking and error-prone, and maintaining a collection of such checkers for a constantly changing design under development is a time-consuming task. Instead, a PSL specification can be used as input to a tool that automatically generates simulatable checkers.

Although in principle, all PSL properties can be checked for finite paths in simulation, the implementation of the checks is often significantly simpler for a subset called the *simple subset* of PSL. Informally, in this subset, composition of temporal properties is restricted to ensure that time *moves forward* from left to right through a property, as it does in a timing diagram. (See 4.4.4 for the formal definition of the simple subset.) For example, the property

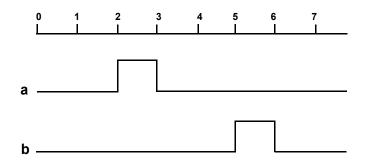

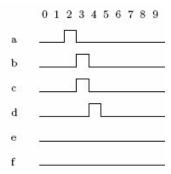

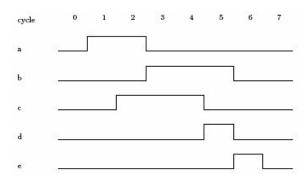

which states that, if a is asserted, then b is asserted three cycles later, belongs to the simple subset, because a appears to the left of b in the property and also appears to the left of b in the timing diagram of any behavior that is not a violation of the property. Figure 2 shows an example of such a timing diagram.

Figure 2—A trace that satisfies Property 2

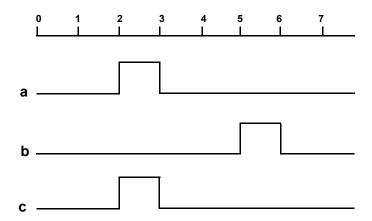

An example of a property that is not in this subset is the property

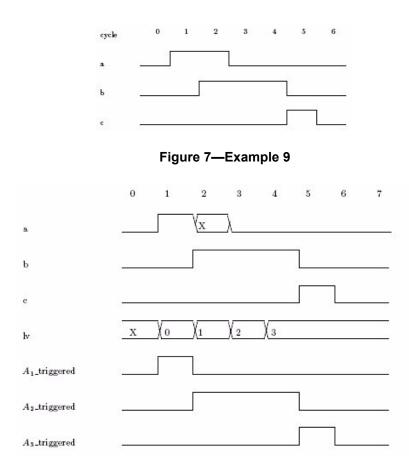

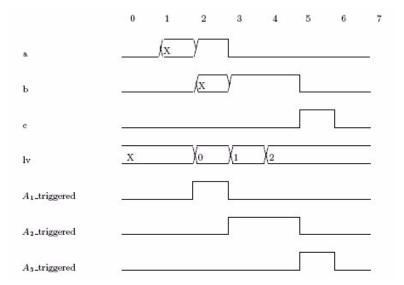

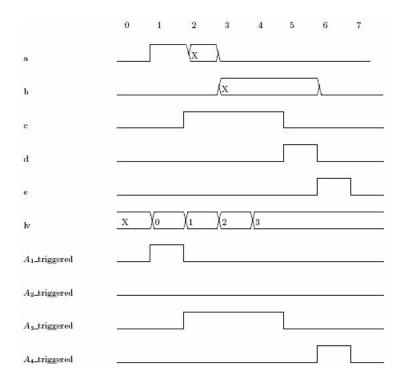

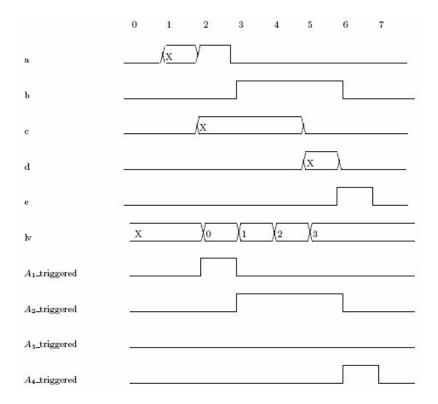

which states that, if a is asserted and b is asserted three cycles later, then c is asserted (in the same cycle as a). This property does not belong to the simple subset, because although c appears to the right of a and b in

the property, it appears to the left of b in a timing diagram that is not a violation of the property. Figure 3 shows an example of such a timing diagram.

Figure 3—A trace that satisfies Property 3

## 1.3.2.2 Formal verification

PSL is an extension of the standard temporal logics Linear-Time Temporal Logic (LTL) and Computation Tree Logic (CTL). A specification in the PSL Foundation Language (respectively, the PSL Optional Branching Extension) can be *compiled down* to a formula of pure LTL (respectively, CTL), possibly with some auxiliary HDL code, known as a *satellite*.

## 2. Normative references

The following referenced documents are indispensable for the application of this document (i.e., they must be understood and used, so each referenced document is cited in text and its relationship to this document is explained). For dated references, only the edition cited applies. For undated referenced, the latest edition of the referenced document (including any amendments or corrigenda) applies.

"General Description Language," Accellera, Napa, CA, Mar. 2005.<sup>2</sup>

IEC/IEEE 62142 (IEEE Std 1364.1), Standard for Verilog Register Transfer Level Synthesis.<sup>3</sup>

IEEE Std 1076<sup>™</sup>, IEEE Standard VHDL Language Reference Manual.<sup>4, 5</sup>

IEEE Std 1076.6™, IEEE Standard for VHDL Register Transfer Level (RTL) Synthesis.

IEEE Std 1364<sup>™</sup>, IEEE Standard for Verilog Hardware Description Language.

IEEE Std 1666™, IEEE Standard for the SystemC Language.

IEEE Std 1800™, IEEE Standard for the SystemVerilog Language.

<sup>&</sup>lt;sup>2</sup>This document is available from the IEEE Standards World Wide Web site, at http://standards.ieee.org/downloads/1850/1850-2005/gdl.pdf.

<sup>&</sup>lt;sup>3</sup>IEC publications are available from the Sales Department of the International Electrotechnical Commission, Case Postale 131, 3, rue de Varembé, CH-1211, Genève 20, Switzerland/Suisse (http://www.iec.ch/). IEC publications are also available in the United States from the Sales Department, American National Standards Institute, 11 West 42nd Street, 13th Floor, New York, NY 10036, USA.

<sup>&</sup>lt;sup>4</sup>IEEE publications are available from the Institute of Electrical and Electronics Engineers, 445 Hoes Lane, P.O. Box 1331, Piscataway, NJ 08855-1331, USA (http://standards.ieee.org/).

<sup>&</sup>lt;sup>5</sup>The IEEE standards or products referred to in this standard are trademarks of the Institute of Electrical and Electronics Engineers, Inc.

## 3. Definitions, acronyms, and abbreviations

For the purposes of this document, the following terms and definitions apply. *The IEEE Standards Dictionary: Glossary of Terms & Definitions* should be referenced for terms not defined in this clause. <sup>6</sup>

## 3.1 Definitions

This subclause defines the terms used in this standard.

**assertion:** A statement that a given property is required to hold and a directive to functional verification tools to verify that it does hold.

**assumption:** A statement that the design is constrained by the given property and a directive to functional verification tools to consider only paths on which the given property holds.

asynchronous property: A property whose clock context is equivalent to True.

behavior: A path.

**Boolean (expression):** An expression that yields a logical value.

**checker:** An auxiliary process (usually constructed as a finite state machine) that monitors simulation of a design and reports errors when asserted properties do not hold. A checker may be represented in the same HDL code as the design or in some other form that can be linked with a simulation of the design.

**completes:** A term used to identify the last cycle of a path that satisfies a sequential expression or property.

**computation path:** A succession of states of the design, such that the design can actually transition from each state on the path to its successor.

**constraint:** A condition (usually on the input signals) that limits the set of behaviors to be considered. A constraint may represent real requirements (e.g., clocking requirements) on the environment in which the design is used, or it may represent artificial limitations (e.g., mode settings) imposed in order to partition the functional verification task.

count: A number or range.

**coverage:** A measure of the occurrence of certain behavior during (typically dynamic) functional verification and, therefore, a measure of the completeness of the (dynamic) functional verification process.

cycle: An evaluation cycle.

**describes:** A term used to identify the set of behaviors for which Boolean expression, sequential expression, or property holds.

**design:** A model of a piece of hardware, described in some hardware description language (HDL). A design typically involves a collection of inputs, outputs, state elements, and combinational functions that compute next state and outputs from current state and inputs.

design behavior: A computation path for a given design.

<sup>&</sup>lt;sup>6</sup>The IEEE Standards Dictionary: Glossary of Terms & Definitions is available at http://shop.ieee.org/.

**dynamic verification:** A verification process such as simulation, in which a property is checked over individual, finite design behaviors that are typically obtained by dynamically exercising the design through a finite number of evaluation cycles. Generally, dynamic verification supports no inference about whether the property holds for a behavior over which the property has not yet been checked.

**evaluation:** The process of exercising a design by iteratively applying values to its inputs, computing its next state and output values, advancing time, and assigning to the state variables and outputs their next values.

**evaluation cycle:** One iteration of the evaluation process. At an evaluation cycle, the state of the design is recomputed (and may change).

extension (of a given path): A path that starts with precisely the succession of states in the given path.

False: An interpretation of certain values of certain data types in an HDL. In the SystemVerilog and Verilog flavors, the single bit values 1'b0, 1'bx, and 1'bz are interpreted as the logical value False. In the VHDL flavor, the values STD.Standard.Boolean'(False) and STD.Standard.Bit'('0'), as well as the values IEEE.std\_logic\_1164.std\_logic'('L'), IEEE.std\_logic\_1164.std\_logic'('L'), IEEE.std\_logic\_1164.std\_logic'('X') and IEEE.std\_logic\_1164.std\_logic'('Z') are all interpreted as the logical value False. In the SystemC flavor, the value 'false' of type bool and any integer literal with a numeric value of 0 are interpreted as the logical value False. In the GDL flavor, the Boolean value 'false' and bit value OB are both interpreted as the logical value False.

**finite range:** A range with a finite high bound.

**formal verification:** A functional verification process in which analysis of a design and a property yields a logical inference about whether the property holds for all behaviors of the design. If a property is declared true by a formal verification tool, no simulation can show it to be false. If the property does not hold for all behaviors, then the formal verification process should provide a specific counterexample to the property, if possible.

**functional verification:** The process of confirming that, for a given design and a given set of constraints, a property that is required to hold in that design actually does hold under those constraints.

**holds:** A term used to talk about the meaning of a Boolean expression, sequential expression, or property.

**holds tightly:** A term used to talk about the meaning of a sequential expression. Sequential expressions are evaluated over finite paths (behavior).

**liveness property:** A property that specifies an eventuality that is unbounded in time. Loosely speaking, a liveness property claims that "something good" eventually happens. More formally, a liveness property is a property for which any finite path can be extended to a path satisfying the property. For example, the property "whenever signal req is asserted, signal ack is asserted some time in the future" is a liveness property.

**logic type:** An HDL data type that includes values that are interpreted as logical values. A logic type may also include values that are not interpreted as logical values. Such a logic type usually represents a multi-valued logic.

**logical value:** A value in the set {*True, False*}.

**model checking:** A type of formal verification.

**number:** A non-negative integer value, and a statically computable expression yielding such a value.

**occurs:** A term used to indicate that a Boolean expression holds in a given cycle.

occurrence (of a Boolean expression): A cycle in which the Boolean expression holds.

**path:** A succession of states of the design, whether or not the design can actually transition from one state on the path to its successor.

**positive count:** A positive number or a positive range.

**positive number:** A number that is greater than zero (0).

**positive range:** A range with a low bound that is greater than zero (0).

**prefix (of a given path):** A path of which the given path is an extension.

**property:** A collection of logical and temporal relationships between and among subordinate Boolean expressions, sequential expressions, and other properties that in aggregate represent a set of behaviors.

range: A series of consecutive numbers, from a low bound to a high bound, inclusive, such that the low bound is less than or equal to the high bound. In particular, this includes the case in which the low bound is equal to the high bound. Also, a pair of statically computable integer expressions specifying such a series of consecutive numbers, where the left expression specifies the low bound of the series, and the right expression specifies the high bound of the series. A range may describe a set of values or a variable number of cycles or event repetitions.

**restriction:** A statement that the design is constrained by the given sequential expression and a directive to functional verification tools to consider only paths on which the given sequential expression holds.

**safety property:** A property that specifies an invariant over the states in a design. The invariant is not necessarily limited to a single cycle, but it is bounded in time. Loosely speaking, a safety property claims that "something bad" does not happen. More formally, a safety property is a property for which any path violating the property has a finite prefix such that every extension of the prefix violates the property. For example, the property, "whenever signal req is asserted, signal ack is asserted within 3 cycles" is a safety property.

**sequence:** A sequential expression that may be used directly within a property or directive.

**sequential expression:** A finite series of terms that represent a set of behaviors.

sequential extended regular expression: A form of sequential expression, and a component of a sequence.

**starts:** A term used to identify the first cycle of a path that satisfies a sequential expression.

**strictly before:** Before, and not in the same cycle as.

**strong operator:** A temporal operator, the non-negated use of which usually creates a liveness property.

**temporal expression:** An expression that involves one or more temporal operators.

**temporal operator:** An operator that represents a temporal (i.e., time-oriented) relationship between its operands.

terminating condition: A Boolean expression, the occurrence of which causes a property to complete.

terminating property: A property that, when it holds, causes another property to complete.

**True:** An interpretation of certain values of certain data types in an HDL. In the SystemVerilog and Verilog flavors, the single bit value 1'b1 is interpreted as the logical value *True*. In the VHDL flavor, the values STD.Standard.Boolean' (True), STD.Standard.Bit'('1'),

IEEE.std\_logic\_1164.std\_logic'('1'), and IEEE.std\_logic\_1164.std\_logic'('H') interpreted as the logical value *True*. In the SystemC flavor, the value 'true' of type bool and any integer literal with a non-zero numeric value are interpreted as the logical value *True*. In the GDL flavor, the Boolean value 'true' and bit value 1B are both interpreted as the logical value *True*.

**unknown value:** A value of a (multi-valued) logic type, other than 0 or 1.

weak operator: A temporal operator, the non-negated use of which does not create a liveness property.

## 3.2 Acronyms and abbreviations

This subclause lists the acronyms and abbreviations used in this standard.

ABV assertion-based verification BNF extended Backus-Naur Form

cpp C pre-processor

CTL computation tree logic

EDA electronic design automation

FL Foundation Language FSM finite state machine

GDL General Description Language

HDL hardware description language

iff if and only if

LTL linear-time temporal logic

PSL Property Specification Language

OBE Optional Branching Extension

RTL Register Transfer Level

SERE Sequential Extended Regular Expression

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

## 3.3 Special terms

The following terms are used in the definition of this standard.

When presenting requirements, options, and recommendations regarding the implementation and use of PSL, the following terms are used:

- can: Used for statements of possibility and capability. In the context of this standard, describes a possible use of PSL to express a given specification, or a possible application of a PSL specification in the design and verification of electronic systems.

- may: Used to indicate a course of action permissible within the limits of the standard. In the context of this standard, typically describes a non-mandatory feature of PSL syntax or semantics, the use of which in a given PSL specification is up to the author of that specification. Also used to identify

- permissible implementation approaches in a verification tool supporting the standard, as well as permissible decisions that can be made when implementing a design according to a given PSL specification.

- shall: Used to indicate mandatory requirements to be followed strictly in order to conform to the standard and from which no deviation is permitted. In the context of this standard, describes a mandatory feature of PSL syntax or semantics that must be present in a given PSL specification, or in the negative form, a syntactic structure or semantic relationship that must not be present, for that specification to be in conformance with the standard.

- should: Used to indicate that among several possibilities, one is recommended as particularly suitable, without mentioning or excluding others; or that a certain course of action is preferred but not necessarily required; or that (in the negative form) a certain course of action is deprecated but not prohibited. In the context of this standard, describes a feature of PSL syntax that is recommended but not mandatory, or (in the negative form) that is not recommended but not prohibited.

When explaining the requirements and options imposed by a PSL specification on the behavior of a design or a design's environment, if that design or environment is to satisfy the PSL specification, the following term is used:

— **is required to:** Used to indicate that the functionality or behavior described by a PSL specification is mandatory for the system to which the specification pertains. This phrase is typically used to state that a design or its environment must function in a manner that is consistent with the specification.

## 4. Organization

#### 4.1 Abstract structure

PSL consists of four layers, which partition the language with respect to functionality. PSL also comes in five flavors, which partition the language with respect to HDL compatibility. Each of these is explained in detail in the following subclauses.

## 4.1.1 Layers

PSL consists of four layers: Boolean, temporal, verification, and modeling.

## 4.1.1.1 Boolean layer

The Boolean layer is used to build expressions that are, in turn, used by the other layers. Although it contains expressions of many types, it is known as the *Boolean layer* because it is the *supplier* of Boolean expressions to the heart of the language—the temporal layer. Boolean layer expressions are evaluated in a single evaluation cycle.

## 4.1.1.2 Temporal layer

The temporal layer is the heart of the language; it is used to describe properties of the design. It is known as the *temporal layer* because, in addition to simple properties, such as "signals a and b are mutually exclusive," it can also describe properties involving complex temporal relations between signals, such as, "if signal c is asserted, then signal d shall be asserted before signal e is asserted, but no more than eight clock cycles later." Temporal expressions are evaluated over a series of evaluation cycles.

#### 4.1.1.3 Verification layer

The verification layer is used to tell the verification tools what to do with the properties described by the temporal layer. For example, the verification layer contains directives that tell a tool to verify that a property holds or to check that a specified sequence is covered by some test case.

#### 4.1.1.4 Modeling layer

The modeling layer is used to model the behavior of design inputs (for tools, such as formal verification tools, which do not use test cases) and to model auxiliary hardware that is not part of the design, but is needed for verification.

#### 4.1.2 Flavors

PSL comes in five *flavors*: one for each of the hardware description languages SystemVerilog, Verilog, VHDL, SystemC, and GDL. The syntax of each flavor conforms to the syntax of the corresponding HDL in a number of specific areas—a given flavor of PSL is compatible with the corresponding HDL's syntax in those areas.

#### 4.1.2.1 SystemVerilog flavor

In the SystemVerilog flavor, all expressions of the Boolean layer, as well as modeling layer code, are written in SystemVerilog syntax (see IEEE Std 1800). The SystemVerilog flavor also has limited influence on the syntax of the temporal layer. For example, ranges of the temporal layer are specified using the SystemVerilog-style syntax i:j.

## 4.1.2.2 Verilog flavor

In the Verilog flavor, all expressions of the Boolean layer, as well as modeling layer code, are written in Verilog syntax (see IEC/IEEE 62142). The Verilog flavor also has limited influence on the syntax of the temporal layer. For example, ranges of the temporal layer are specified using the Verilog-style syntax i:j.

#### 4.1.2.3 VHDL flavor

In the VHDL flavor, all expressions of the Boolean layer, as well as modeling layer code, are written in VHDL syntax (see IEEE Std 1076). The VHDL flavor also has some influence on the syntax of the temporal layer. For example, ranges of the temporal layer are specified using the VHDL-style syntax i to j.

## 4.1.2.4 SystemC flavor

In the SystemC flavor, all expressions of the Boolean layer, as well as modeling layer code, are written in SystemC syntax (see IEEE Std 1666). The SystemC flavor also has limited influence on the syntax of the temporal layer. For example, ranges of the temporal layer are specified using the syntax i:j.

#### 4.1.2.5 GDL flavor

In the GDL flavor, all expressions of the Boolean layer, as well as modeling layer code, are written in GDL syntax (see "General Description Language"). The GDL flavor also has some influence on the syntax of the temporal layer. For example, ranges of the temporal layer are specified using the GDL-style syntax i..j.

#### 4.2 Lexical structure

This subclause defines the identifiers, keywords, operators, macros, and comments used in PSL.

#### 4.2.1 Identifiers

Identifiers in PSL consist of an alphabetic character, followed by zero or more alphanumeric characters; each subsequent alphanumeric character may optionally be preceded by a single underscore character.

Example

```

mutex

Read_Transaction

L_123

```

PSL identifiers are case-sensitive in the SystemVerilog, Verilog, and SystemC flavors and case-insensitive in the VHDL and GDL flavors.

## 4.2.2 Keywords

Keywords are reserved identifiers in PSL, so an HDL name that is a PSL keyword cannot be referenced directly, by its simple name, in an HDL expression used in a PSL property. However, such an HDL name can be referenced indirectly, using a hierarchical name or qualified name as allowed by the underlying HDL.

The keywords used in PSL are shown in Table 1.

## Table 1—Keywords

| $\mathbf{A}_{-}$           | E                                         | next!            | rose               |

|----------------------------|-------------------------------------------|------------------|--------------------|

| AF                         | EF                                        | next a           |                    |

| AG                         | EG                                        | next a!          | sequence           |

| AX                         | EX                                        | next_e           | stable             |

| abort                      | ended                                     | next e!          | string             |

| always<br>and <sup>a</sup> | eventually!                               | next_event       | strong             |

| assert                     | eventuany.                                | next_event!      | sync abort         |

| assume                     | F                                         |                  | sync_abort         |

| async_abort                | _                                         | next_event_a     | to <sup>e</sup>    |

|                            | fairness                                  | next_event_a!    | 10                 |

| before                     | fell                                      | next_event_e     | **                 |

| before!                    | for                                       | next_event_e!    | U                  |

| before!_                   | forall                                    | nondet           | union              |

| before_<br>bit             |                                           | nondet_vector    | until              |

| bitvector                  | $\mathbf{G}$                              | not <sup>c</sup> | until!             |

| boolean                    |                                           | numeric          | until!             |

| Dooreum                    | hdltype                                   |                  | until <sup>—</sup> |

| clock                      | J. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. | onehot           |                    |

| const                      | in                                        | onehot0          | vmode              |

| countones                  | inf                                       | or <sup>d</sup>  | vpkg               |

| cover                      | inherit                                   |                  | vprop              |

|                            | is <sup>b</sup>                           | property         | vunit              |

| default                    |                                           | prev             | vuiiit             |

| deludit                    | isunknown                                 | Pici             | ***                |

|                            |                                           | report           | W                  |

|                            | mutable                                   | restrict         | within             |

|                            |                                           | restrict!        |                    |

|                            | never                                     | 1 CSUI ICL.      | X                  |

|                            | next                                      |                  | <b>X!</b>          |

|                            |                                           |                  |                    |

**and** is a keyword only in the VHDL flavor; see the flavor macro AND OP (4.3.2.6).

## 4.2.3 Operators

## 4.2.3.1 HDL operators

For a given flavor of PSL, the operators of the underlying HDL have the highest precedence. In particular, this includes logical, relational, and arithmetic operators of the HDL. The HDL's logical operators for negation, conjunction, and disjunction of Boolean values may be used in PSL for negation, conjunction, and disjunction of properties as well. In such applications, those operators have their usual precedence and associativity, as if the PSL properties that are operands produced Boolean values of a type appropriate to the logical operators native to the HDL.

## 4.2.3.2 Foundation Language (FL) operators

Various operators are available in PSL. Each operator has a precedence relative to other operators. In general, operators with a higher relative precedence are associated with their operands before operators with a lower relative precedence. If two operators with the same precedence appear in sequence, then the operators are associated with their operands according to the associativity of the operators. Left-associative

bis is a keyword only in the VHDL flavor; see the flavor macro DEF\_SYM (4.3.2.9).

**cnot** is a keyword only in the VHDL flavor; see the flavor macro NOT\_OP (4.3.2.6).

**dor** is a keyword only in the VHDL flavor; see the flavor macro OR\_O₱ (4.3.2.6).

**eto** is a keyword only in the VHDL flavor; see the flavor macro RANGE SYM (4.3.2.7).

operators are associated with operands in left-to-right order of appearance in the text; right-associative operators are associated with operands in right-to-left order of appearance in the text.

Table 2—FL operator precedence and associativity

| Operator class                  | Associativity | Operators                       |

|---------------------------------|---------------|---------------------------------|

| (highest precedence)            |               |                                 |

| HDL operators                   |               |                                 |

| Union operator                  | left          | union                           |

| Clocking operator               | left          | <b>@</b>                        |

| SERE repetition operators       | left          | [*] [+] [=] [->]                |

| Sequence within operator        | left          | within                          |

| Sequence AND operators          | left          | & &&                            |

| Sequence OR operator            | left          | 1                               |

| Sequence fusion operator        | left          | :                               |

| Sequence concatenation operator | left          | ;                               |

| FL termination operator         | left          | abort async_abort<br>sync_abort |

| FL occurrence operators         | right         | next* eventually!<br>X X! F     |

| FL bounding operators           | right         | U W until* before*              |

| Sequence implication operators  | right         | ->  =>                          |

| Boolean implication operators   | right         | -> <->                          |

| FL invariance operators         | right         | always never                    |

| (lowest precedence)             |               | G                               |

NOTE—The notation next\* represents the *next* family of operators, which includes the operators next, next!, next\_a, next\_a!, next\_e, next\_e!, next\_event, next\_event!, next\_event\_a!, and next\_event\_e!. The notation until\* represents the *until* family of operators, which includes the operators until!, until!, and until!\_. The notation before\* represents the *before* family of operators, which includes the operators before, before!, before\_, and before!\_.

#### 4.2.3.2.1 Union operator

For any flavor of PSL, the FL operator with the next highest precedence after the HDL operators is that used to indicate a non-deterministic expression:

union union operator

The union operator is left-associative.

## 4.2.3.2.2 Clocking operator

For any flavor of PSL, the FL operator with the next highest precedence is the clocking operator, which is used to associate a clock expression with a property or sequence:

@ clock event

The clocking operator is left-associative.

<sup>&</sup>lt;sup>7</sup>Notes in text, tables, and figures are given for information only and do not contain requirements needed to implement the standard.

#### 4.2.3.2.3 SERE repetition operators

For any flavor of PSL, the FL operators with the next highest precedence are the repetition operators, which are used to construct Sequential Extended Regular Expressions (SEREs). These operators are as follows:

| [*]   | consecutive repetition     |

|-------|----------------------------|

| [+]   | consecutive repetition     |

| [= ]  | non-consecutive repetition |

| [-> ] | goto repetition            |

SERE repetition operators are left-associative.

#### 4.2.3.2.4 Sequence within operator

For any flavor of PSL, the FL operator with the next highest precedence is the sequence within operator, which is used to describe behavior in which one sequence occurs during the course of another, or within a time-bounded interval:

```

within sequence within operator

```

The sequence within operator is left-associative.

#### 4.2.3.2.5 Sequence conjunction operators

For any flavor of PSL, the FL operators with the next highest precedence are the sequence conjunction operators, which are used to describe behavior consisting of parallel paths. These operators are as follows:

```

a non-length-matching sequence conjunctionlength-matching sequence conjunction

```

Sequence conjunction operators are left-associative.

#### 4.2.3.2.6 Sequence disjunction operator

For any flavor of PSL, the FL operator with the next highest precedence is the sequence disjunction operator, which is used to describe behavior consisting of alternative paths:

sequence disjunction

The sequence disjunction operator is left-associative.

## 4.2.3.2.7 Sequence fusion operator

For any flavor of PSL, the FL operator with the next highest precedence is the sequence fusion operator, which is used to describe behavior in which a later sequence starts in the same cycle in which an earlier sequence completes:

sequence fusion

The sequence fusion operator is left-associative.

#### 4.2.3.2.8 Sequence concatenation operator

For any flavor of PSL, the FL operator with the next highest precedence is the sequence concatenation operator, which is used to describe behavior in which one sequence is followed by another:

; sequence concatenation

The sequence concatenation operator is left-associative.

#### 4.2.3.2.9 FL termination operators

For any flavor of PSL, the FL operators with the next highest precedence are the FL termination operators, which are used to describe behavior in which a condition causes both current and future obligations to be canceled:

```

sync_abort immediate termination of current and future obligations, synchronous with the clock async_abort immediate termination of current and future obligations, independent of the clock abort equivalent to async_abort

```

The FL termination operators are left-associative.

## 4.2.3.2.10 FL occurrence operators

For any flavor of PSL, the FL operators with the next highest precedence are those used to describe behavior in which an operand holds in the future. These operators are as follows:

```

eventually! the right operand holds at some time in the indefinite future

next* the right operand holds at some specified future time or range of future times

```

FL occurrence operators are right-associative.

## 4.2.3.2.11 Bounding operators

For any flavor of PSL, the FL operators with the next highest precedence are those used to describe behavior in which one property holds in some cycle or in all cycles before another property holds. These operators are as follows:

```

until* the left operand holds at every time until the right operand holds before* the left operand holds at some time before the right operand holds

```

FL bounding operators are right-associative.

## 4.2.3.2.12 Suffix implication operators

For any flavor of PSL, the FL operators with the next highest precedence are those used to describe behavior consisting of a property that holds at the end of a given sequence. These operators are as follows:

```

| -> overlapping suffix implication

| => non-overlapping suffix implication

```

The suffix implication operators are right-associative.

NOTE—The FL Property  $\{r\}$  (f) is an alternative form for (and has the same semantics as) the FL Property  $\{r\}$  |-> f.

#### 4.2.3.2.13 Logical implication operators

For any flavor of PSL, the FL operators with the next highest precedence are those used to describe behavior consisting of a Boolean, a sequence, or a property that holds if another Boolean, sequence, or property holds. These operators are as follows:

-> logical IF implication <-> logical IFF implication

The logical IF and logical IFF implication operators are right-associative.

## 4.2.3.2.14 FL invariance operators

For any flavor of PSL, the FL operators with the next highest precedence are those used to describe behavior in which a property does or does not hold, globally. These operators are as follows:

always the right operand holds, globally

never the right operand does NOT hold, globally

FL occurrence operators are right-associative.

## 4.2.3.3 Optional Branching Extension (OBE) operators

Table 3—OBE operator precedence and associativity

| Operator class                | Associativity | Opera          | Operators        |  |

|-------------------------------|---------------|----------------|------------------|--|

| (highest precedence)          |               |                |                  |  |

| HDL operators                 |               |                |                  |  |

| OBE occurrence operators      | left          | AX AG AF A [U] | EX EG EF<br>E[U] |  |

| Boolean implication operators | right         | ->             | <->              |  |

| (lowest precedence)           |               |                |                  |  |

## 4.2.3.3.1 OBE occurrence operators

For any flavor of PSL, the OBE operators with the next highest precedence after the HDL operators are those used to specify when a subordinate property is required to hold, if the parent property is to hold. These operators include the following:

| AX   | on all paths, at the next state on each path                    |

|------|-----------------------------------------------------------------|

| AG   | on all paths, at all states on each path                        |

| AF   | on all paths, at some future state on each path                 |

| EX   | on some path, at the next state on the path                     |

| EG   | on some path, at all states on the path                         |

| EF   | on some path, at some future state on the path                  |

| A[U] | on all paths, in every state up to a certain state on each path |

| E[U] | on some path, in every state up to a certain state on that path |

The OBE occurrence operators are left-associative.

#### 4.2.3.3.2 OBE implication operators

For any flavor of PSL, the OBE operators with the next highest precedence are those used to describe behavior consisting of a Boolean or a property that holds if another Boolean or property holds. These operators are:

```

-> logical IF implication

<-> logical IFF implication

```

The logical IF and logical IFF implication operators are right-associative.

#### 4.2.4 Macros

PSL provides macro processing capabilities that facilitate the definition of properties. SystemC, VHDL, and GDL flavors support cpp pre-processing directives (e.g., #define, #ifdef, #else, #include, and #undef). SystemVerilog and Verilog flavors support Verilog compiler directives (e.g., `define, `ifdef, `else, `include, and `undef). All flavors also support PSL macros %for and %if, which can be used to conditionally or iteratively generate PSL statements. The cpp or Verilog compiler directives shall be interpreted first, and PSL %if and %for macros shall be interpreted second.

#### 4.2.4.1 The %for construct

The %for construct replicates a piece of text a number of times, usually with each replication particularized via parameter substitution. The syntax of the %for construct is as follows:

The replicator name var is any legal PSL identifier name. It shall not be the same as any other identifier (variable, unit name, design signal etc.) except another non-enclosing PSL replicator var. The replication expressions expr1 and expr2 shall be statically computed expressions resulting in a legal PSL range. A replication item item is any legal PSL alphanumeric string or previously defined cpp style macro.

In the first case, the text inside the \*for-\*end pairs will be replicated expr2-expr1+1 times (assuming that expr2>=expr1). In the second case, the text will be replicated according to the number of items in the list. During each replication of the text, the loop variable value is substituted into the text as follows. Suppose the loop variable is called ii. Then the current value of the loop variable may be accessed from the loop body using the following three methods:

a) The current value of the loop variable can be accessed using simply ii if ii is a separate token in the text. For instance:

```

%for ii in 0..3 do

define aa(ii) := ii > 2;

%end

```

is equivalent to:

```

define aa(0) := 0 > 2;

define aa(1) := 1 > 2;

define aa(2) := 2 > 2;

define aa(3) := 3 > 2;

```

b) If ii is part of an identifier, the value of ii may be accessed using  $\{i\}$  as follows:

```

%for ii in 0..3 do

define aa%{ii} := ii > 2;

%end

```

which is equivalent to:

```

define aa0 := 0 > 2;

define aa1 := 1 > 2;

define aa2 := 2 > 2;

define aa3 := 3 > 2;

```

c) If ii needs to be used as part of an expression, it may be accessed as follows:

```

%for ii in 1..4 do

define aa%{ii-1} := %{ii-1} > 2;

%end

```

The above is equivalent to:

```

define aa0 := 0 > 2;

define aa1 := 1 > 2;

define aa2 := 2 > 2;

define aa3 := 3 > 2;

```

The following operators may be used in pre-processor expressions:

#### 4.2.4.2 The %if construct