DS120-1 (v1.2) October 18, 2004

## **XC9500 In-System Programmable CPLD Automotive IQ Family**

### **Product Specification**

### **Features**

- System frequency up to 55 MHz

- Guaranteed to meet full electrical specifications over  $T_{\Delta}$  $= -40 \text{ to } +125^{\circ}\text{C}$

- 5V in-system programmable

- Endurance of 10,000 program/erase cycles

- Enhanced pin-locking architecture

- Flexible 36V 18 Function Block

- 90 product terms drive any or all of 18 macrocells within Function Block

- Global and product term clocks, output enables, set and reset signals

- Extensive IEEE Std 1149.1 boundary-scan (JTAG)

- Programmable power reduction mode in each macrocell

- Slew rate control on individual outputs

- User programmable ground pin capability

- Extended pattern security features for design protection

- High-drive 24 mA outputs

- 3.3V or 5V I/O capability

- CMOS 5V Fast FLASH™ technology

- Supports parallel programming of multiple XC9500 devices

- Refer to XC9500 Family data sheet [September 15, 1999 (version 5.0)] for architecture description

- Refer to XC9536 data sheet [December 4, 1998 (version 5.0)] and XC9572XL data sheet [December 4, 1998 (version 3.0)] for pin tables

## **Family Overview**

The XC9500 CPLD Automotive IQ family provides advanced in-system programming and test capabilities for high performance, general purpose logic integration. All devices are in-system programmable for a minimum of 10,000 program/erase cycles. Extensive IEEE 1149.1 (JTAG) boundary-scan support is also included on all family members.

As shown in Table 1, logic density of the XC9500 devices ranges from 800 to 1,600 usable gates with 36 and 72 registers, respectively. Multiple package options and associated I/O capacity are shown in Table 2. The XC9500 family is fully pin-compatible allowing easy design migration across multiple density options in a given package footprint.

The XC9500 architectural features address the requirements of in-system programmability. Enhanced pin-locking capability avoids costly board rework. An expanded JTAG instruction set allows version control of programming patterns and in-system debugging. In-system programming throughout the full device operating range and a minimum of 10,000 program/erase cycles provide worry-free reconfigurations and system field upgrades.

Advanced system features include output slew rate control and user-programmable ground pins to help reduce system noise. I/Os may be configured for 3.3V or 5V operation. All outputs provide 24 mA drive.

Table 1: XC9500 Device Automotive Family

|                                          | XC9536 | XC9572 |

|------------------------------------------|--------|--------|

| Macrocelis                               | 36     | 72     |

| Usable Gates                             | 800    | 1,600  |

| Registers                                | 36     | 72     |

| T <sub>PD</sub> (ns)                     | 5      | 7.5    |

| T <sub>SU</sub> (ns)                     | 3.5    | 4.5    |

| T <sub>CO</sub> (ns)                     | 4.0    | 4.5    |

| f <sub>CNT</sub> (MHz) <sup>(1)</sup>    | 100    | 125    |

| f <sub>SYSTEM</sub> (MHz) <sup>(2)</sup> | 100    | 83.3   |

#### Notes:

- f<sub>CNT</sub> = Operating frequency for 16-bit counters.

- f<sub>SYSTEM</sub> = Internal operating frequency for general purpose system designs spanning multiple FBs.

Table 2: Available Packages and Device I/O Pins (not including dedicated JTAG pins)

|              | XC9536 | XC9572 |

|--------------|--------|--------|

| 44-Pin VQFP  | 34     | -      |

| 100-Pin TQFP | -      | 72     |

© 2003 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at http://www.xilinx.com/legal.htm. All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

### **Absolute Maximum Ratings**

| Symbol                               | Description                                       | Value                         | Units |

|--------------------------------------|---------------------------------------------------|-------------------------------|-------|

| V <sub>CC</sub>                      | Supply voltage relative to GND                    | -0.5 to 7.0                   | V     |

| V <sub>IN</sub>                      | Input voltage relative to GND                     | -0.5 to V <sub>CC</sub> + 0.5 | V     |

| V <sub>TS</sub>                      | V <sub>TS</sub> Voltage applied to 3-state output |                               | V     |

| T <sub>J</sub>                       | T <sub>J</sub> Junction temperature               |                               | °C    |

| T <sub>A</sub> Operating temperature |                                                   | -40°C to +125°C               | °C    |

| T <sub>STG</sub>                     | T <sub>STG</sub> Storage temperature (ambient)    |                               | °C    |

#### Notes:

### **Recommended Operation Conditions**

| Symbol            | Parameter                                                    | Min | Max                      | Units |  |

|-------------------|--------------------------------------------------------------|-----|--------------------------|-------|--|

| $V_{CCINT}$       | Supply voltage for internal logic and input buffers          | 4.5 | 5.5                      | V     |  |

| V <sub>CCIO</sub> | Supply voltage for output drivers for 5V operation           | 4.5 | 5.5                      | V     |  |

|                   | Supply voltage for output drivers for 3.3 voperation 3.0 3.6 |     |                          |       |  |

| $V_{IL}$          | Low-level input voltage                                      | 0   | 0.80                     | V     |  |

| V <sub>IH</sub>   | High-level input voltage                                     | 2.0 | V <sub>CCINT</sub> + 0.5 | V     |  |

| V <sub>O</sub>    | Output voltage 0 V <sub>CCIO</sub>                           |     |                          |       |  |

| Quality a         | and Reliability Characteristics                              | 4   |                          |       |  |

|                   |                                                              |     |                          |       |  |

## **Quality and Reliability Characteristics**

| Symbol          | Parameter                        | Min Max | Units  |

|-----------------|----------------------------------|---------|--------|

| T <sub>DR</sub> | Data Retention                   | 20      | Years  |

| N <sub>PE</sub> | Program/Erase Cycles (Endurance) | 10,000  | Cycles |

## **DC Characteristic Over Recommended Operating Conditions**

| Symbol          | Parameter                            | Test Conditions                                 |        | Min     | wax   | Units |

|-----------------|--------------------------------------|-------------------------------------------------|--------|---------|-------|-------|

| $V_{OH}$        | Output high voltage for 5V outputs   | $I_{OH} = -4.0 \text{ mA}, V_{CC} = \text{Min}$ |        | 2.4     | -     | V     |

|                 | Output high voltage for 3.3V outputs | $I_{OH} = -3.2 \text{ mA}, V_{CC} = \text{Min}$ |        | 2.4     | -     | V     |

| V <sub>OL</sub> | Output low voltage for 5V outputs    | $I_{OL}$ = 24 mA, $V_{CC}$ = Min                |        | -       | 0.5   | V     |

|                 | Output low voltage for 3.3V outputs  | I <sub>OL</sub> = 10 mA, V <sub>CC</sub> = Min  |        | -       | 0.4   | V     |

| I <sub>IL</sub> | Input leakage current                | $V_{CC} = Max. V_{IN} = GND \text{ or } V_{CC}$ |        | -       | ±10   | μΑ    |

| I <sub>IH</sub> | I/O high-Z leakage current           | $V_{CC} = Max, V_{IN} = GND \text{ or } V_{CC}$ |        | -       | ±10   | μΑ    |

| C <sub>IN</sub> | I/O capacitance                      | V <sub>IN</sub> = GND, f = 1.0 MHz              |        | -       | 10    | pF    |

| I <sub>CC</sub> | Operating supply current             | V <sub>I</sub> = GND, No load                   | XC9536 | 30 (Тур | ical) | mA    |

|                 | (low power mode, active)             | f = 1.0 MHz XC9572                              |        | 65 (Typ | ical) |       |

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those listed under Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time may affect device reliability.

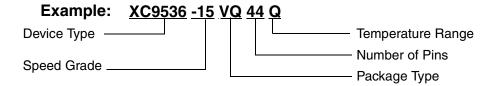

# **Ordering Information**

| Device Ordering<br>Number | Speed<br>(pin-to-pin<br>delay) | Pkg.<br>Symbol | No. of<br>Pins | Package Type                    | Operating<br>Range <sup>(1)</sup> |

|---------------------------|--------------------------------|----------------|----------------|---------------------------------|-----------------------------------|

| XC9536-15VQ44Q            | 15 ns                          | VQ44           | 44-pin         | Thin Quad Flat Pack (VQFP)      | Q                                 |

| XC9572-15TQ100Q           | 15 ns                          | TQ100          | 100-pin        | Very Thin Quad Flat Pack (TQFP) | Q                                 |

#### Notes:

1. Q = Automotive:  $T_A = -40^{\circ}$  to  $+125^{\circ}$ C

### **Revision History**

The following table shows the revision history for this document.

| Date | Version  | Revision                                                                    |

|------|----------|-----------------------------------------------------------------------------|

| 1.0  | 11/26/02 | Initial Xilinx release.                                                     |

| 1.1  | 02/03/03 | Added reference to XC9500, XC9536, and XC9572 data sheets.                  |

| 1.2  | 10/18/04 | Added "Not to be used in new designs" watermark; moved to "Mature Products" |

|      |          | 905/9/25                                                                    |