# Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC User Guide

UG194 (v1.10) February 14, 2011

Xilinx is disclosing this user guide, manual, release note, and/or specification (the "Documentation") to you solely for use in the development of designs to operate with Xilinx hardware devices. You may not reproduce, distribute, republish, download, display, post, or transmit the Documentation in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Xilinx expressly disclaims any liability arising out of your use of the Documentation. Xilinx reserves the right, at its sole discretion, to change the Documentation without notice at any time. Xilinx assumes no obligation to correct any errors contained in the Documentation, or to advise you of any corrections or updates. Xilinx expressly disclaims any liability in connection with technical support or assistance that may be provided to you in connection with the Information.

THE DOCUMENTATION IS DISCLOSED TO YOU "AS-IS" WITH NO WARRANTY OF ANY KIND. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DOCUMENTATION, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NONINFRINGEMENT OF THIRD-PARTY RIGHTS. IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOSS OF DATA OR LOST PROFITS, ARISING FROM YOUR USE OF THE DOCUMENTATION.

© 2006–2011 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners.

## **Revision History**

| Date     | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 09/06/06 | 1.0     | Initial Xilinx release on CD.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 10/13/06 | 1.1     | Added further descriptions and figures to "SGMII RX Elastic Buffer" in Chapter 6.                                                                                                                                                                                                                                                                                                                                                                              |

| 03/06/07 | 1.2     | Modified RGMII IDELAY placement and inputs in Figure 6-3, Figure 6-4, Figure 6-6 through Figure 6-10, and Figure 6-12 through Figure 6-17.                                                                                                                                                                                                                                                                                                                     |

| 08/08/07 | 1.3     | <ul> <li>Chapter 1: Minor grammatical edits in "Preamble" and "Model Considerations."</li> <li>Chapter 2: Modified description of EMAC#_LTCHECK_DISABLE in Table 2-17.</li> <li>Chapter 3:</li> <li>Added "Standard Conditions" and "1000BASE-X/SGMII Specific Conditions" sections.</li> <li>Added new paragraph to "Enabled."</li> <li>Modified paragraph in "Receiving a PAUSE Control Frame."</li> <li>Chapter 4:</li> <li>Modified Figure 4-1.</li> </ul> |

The following table shows the revision history for this document.

| Date     | Version  | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 08/08/07 | 1.3      | Edited text in "Clocking Requirements."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| (cont'd) | (cont'd) | Minor grammatical edits in paragraph above Table 4-16, and "Ethernet MAC Configuration and Address Filter Access."                                                                                                                                                                                                                                                                                                                                                                                                         |

|          |          | Chapter 6:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|          |          | • Added IDELAY elements to GMII_RX_CLK and GMII_RXD[7:0] lines in Figure 6-6 to Figure 6-10.                                                                                                                                                                                                                                                                                                                                                                                                                               |

|          |          | • Added description of fixed-mode IDELAYs to "Gigabit Media Independent Interface (GMII)."                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|          |          | • Added IDELAY elements to RGMII_RXC lines between IBUFG and BUFG in Figure 6-12 to Figure 6-17.                                                                                                                                                                                                                                                                                                                                                                                                                           |

|          |          | Modified description of IDELAY in "Reduced Gigabit Media Independent Interface (RGMII)."                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|          |          | • Modified speed data in Table 6-2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          |          | • Modified Ethernet MAC connections in Figure 6-36 and Figure 6-37.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 03/31/08 | 1.4      | • Updated the following: Table 3-4, Figure 6-3, Figure 6-4, Figure 6-6, Figure 6-7, Figure 6-10, Figure 6-12, Figure 6-13, Figure 6-15, Figure 6-17, Figure 6-20, Figure 6-21, Figure 6-22 (and notes), Figure 6-34, Figure 6-35, Figure 6-36, Figure 6-39, and Figure 6-40.                                                                                                                                                                                                                                               |

|          |          | • Updated the following sections: "Ethernet Communications Port for an Embedded<br>Processor," "RocketIO Serial Transceiver Signals," "Statistics Registers/Counters,"<br>"GMII Clock Management for 1 Gb/s Only," "GMII Clock Management for Tri-Speed<br>Operation Using Clock Enables," "16-Bit Data Client," "RocketIO Serial Transceiver<br>Logic Using the RX Elastic Buffer in FPGA Logic," "SGMII Clock Management (LXT<br>and SXT Devices)," "1000BASE-X PCS/PMA (16-Bit Data Client) Mode," and "Host<br>Clock." |

|          |          | Added LXT device information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|          |          | • Added Figure 6-23, Figure 6-24, Figure 6-36, and Figure 6-37.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 06/06/08 | 1.5      | Chapter 2: Updated Table 2-16.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|          |          | Chapter 3:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|          |          | • Updated "Client-Supplied FCS Passing," page 53, "Frame Collisions - Half-Duplex 10/100 Mb/s Operation Only," page 56, "VLAN Tagged Frames," page 66, and the enabled discussion in "Length/Type Field Error Checks."                                                                                                                                                                                                                                                                                                     |

|          |          | Chapter 4:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|          |          | • Updated Table 4-7, Table 4-8, Figure 4-1, Figure 4-4, and Figure 4-5.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|          |          | Updated "Introduction to the Ethernet MAC Host Interface."                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|          |          | Chapter 6: Updated "Overview of Operation."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|          |          | Appendix C: Updated "DCR Bus Modifications."                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|          |          | Added Appendix D, "Differences between Soft IP Cores and the Tri-Mode Ethernet MAC."                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 07/24/08 | 1.6      | Updated "Transmitting a PAUSE Control Frame," Table 5-6, and Table 5-7.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10/17/08 | 1.7      | • Added HOSTEMAC1SEL signal to Figure 4-6 and Figure 4-7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|          |          | • Added host_stats_lsw_rdy and host_stats_msw_rdy signals to Figure 7-1.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Date     | Version | Revision                                                                                                                                                                                                                               |

|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 04/28/09 | 1.8     | All chapters:                                                                                                                                                                                                                          |

|          |         | Changed references to FXT devices to include both TXT and FXT devices.                                                                                                                                                                 |

|          |         | • Replaced the term platform with the term device.                                                                                                                                                                                     |

|          |         | • Replaced the term SmartModel with the term SecureIP model.                                                                                                                                                                           |

|          |         | Chapter 2:                                                                                                                                                                                                                             |

|          |         | • Changed references to GTP transceiver to GTP/GTX transceiver in Figure 2-1, page 27, Figure 2-2, page 29, and Figure 2-3, page 32.                                                                                                   |

|          |         | Chapter 3:                                                                                                                                                                                                                             |

|          |         | • Revised the text of "Client-Supplied FCS Passing" on page 53.                                                                                                                                                                        |

|          |         | Chapter 5:                                                                                                                                                                                                                             |

|          |         | • Changed references to GTP transceiver to GTP/GTX transceiver in Figure 5-4, page 119, Figure 5-6, page 121, Figure 5-7, page 122, and Figure 5-8, page 130.                                                                          |

|          |         | Chapter 6:                                                                                                                                                                                                                             |

|          |         | • Revised Note 1 to indicate the clock input of IFD can be driven by a BUFIO in Figure 6-3, page 141, Figure 6-8, page 148, Figure 6-14, page 157, and Figure 6-15, page 159.                                                          |

|          |         | • Added Note 1 indicating a BUFG buffer can be replaced by a BUFR and the clock input of IFD can be driven by a BUFIO in Figure 6-4, page 142, Figure 6-6, page 145, Figure 6-7, page 147, and Figure 6-10, page 152.                  |

|          |         | • Added Note 1 indicating a BUFG buffer can be replaced by a BUFR and the clock input of IDDR can be driven by a BUFIO in Figure 6-12, page 154, Figure 6-13, page 156, Figure 6-16, page 160, and Figure 6-17, page 162.              |

|          |         | • Where a RocketIO® transceiver is shown, added the term RocketIO in Figure 6-21, page 169, Figure 6-22, page 170, Figure 6-36, page 191, and Figure 6-37, page 192.                                                                   |

|          |         | • Revised schematic by adding a BUFGMUX to the PHYEMAC#MIITXCLK input in Figure 6-8, page 148.                                                                                                                                         |

|          |         | • Revised schematic by changing the I0 input source for the BUFGMUX on the PHYEMAC#TXGMIIMIICLKIN input in Figure 6-8, page 148.                                                                                                       |

|          |         | • Revised schematic by adding a BUFG buffer between the transceiver REFCLKOUT output and the DCM CLKIN input in Figure 6-22, page 170, Figure 6-23, page 172, Figure 6-24, page 173, Figure 6-38, page 194, and Figure 6-39, page 195. |

|          |         | • Changed references to GTP transceiver to GTP/GTX transceiver in Figure 6-28, page 179, Figure 6-29, page 182, Figure 6-33, page 186, and Figure 6-41, page 198.                                                                      |

|          |         | • Added link to UG198 in "RX Elastic Buffer Implementations" on page 181 and<br>"The FPGA RX Elastic Buffer Requirement" on page 181.                                                                                                  |

| Date     | Version | Revision                                                                                                                            |

|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------|

| 10/01/09 | 1.9     | Chapter 1:                                                                                                                          |

|          |         | • Revised first paragraph in "Frame Transmission and Interframe Gap," page 23.                                                      |

|          |         | Chapter 2:                                                                                                                          |

|          |         | Revised EMAC#_RXFLOWCTRL_ENABLE and     EMAC#_TXFLOWCTRL_ENABLE descriptions in Table 2.17, page 45                                 |

|          |         | EMAC#_TXFLOWCTRL_ENABLE descriptions in Table 2-17, page 45.                                                                        |

|          |         | Chapter 3:                                                                                                                          |

|          |         | • Revised first paragraph in "Flow Control Block," page 73.                                                                         |

|          |         | Chapter 5:                                                                                                                          |

|          |         | • Revised Link Status description in Table 5-4, page 124.                                                                           |

| 02/14/11 | 1.10    | Updated description of EMAC#_PAUSEADDR[47:0] in Table 2-17.                                                                         |

|          |         | Added description of standard and alternative clock management to "Transmitter Statistics Vector" and "Receiver Statistics Vector." |

|          |         | Updated Table 4-14.                                                                                                                 |

|          |         | Added "Use of Clock Correction Sequences."                                                                                          |

## Table of Contents

| Guide Contents               | 11 |

|------------------------------|----|

| Additional Documentation     | 12 |

| Additional Support Resources | 13 |

| Jser Guide Conventions       | 13 |

| Acronyms                     |    |

| Typographical                | 15 |

| Online Document              | 15 |

## **Chapter 1: Introduction**

| <b>Key Features</b>                                     |

|---------------------------------------------------------|

| Typical Ethernet Application Overview    18             |

| Ethernet Switch or Router                               |

| Ethernet Communications Port for an Embedded Processor  |

| Ethernet Protocol Overview                              |

| Ethernet Sublayer Architecture 20                       |

| Ethernet Data Format                                    |

| Frame Transmission and Interframe Gap 23                |

| Using the Embedded Ethernet MAC 24                      |

| Accessing the Ethernet MAC from the CORE Generator Tool |

| Simulating the Ethernet MAC using SecureIP Models       |

## **Chapter 2: Ethernet MAC Overview**

| Architecture Description                    |

|---------------------------------------------|

| Ethernet MAC Configuration Options          |

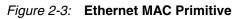

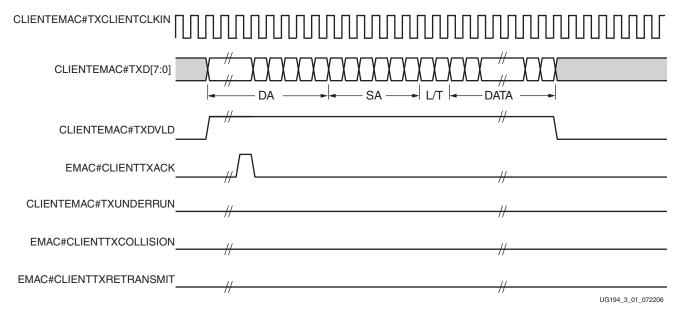

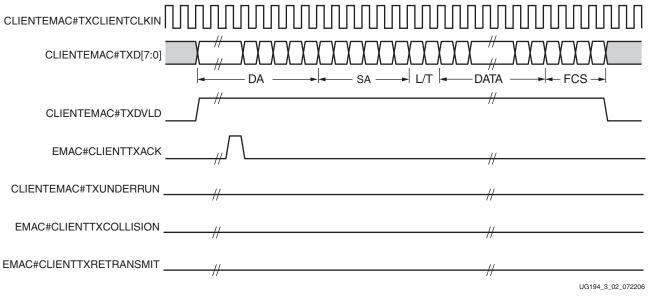

| Ethernet MAC Primitive                      |

| Ethernet MAC Signal Descriptions            |

| Client-Side Signals                         |

| Host Interface Signals 36                   |

| Management Data Input/Output (MDIO) Signals |

| MII/GMII/RGMII Physical Interface Signals   |

| RocketIO Serial Transceiver Signals         |

| Global Clock and Reset Signals 41           |

| Ethernet MAC Attributes                     |

## **Chapter 3: Client Interface**

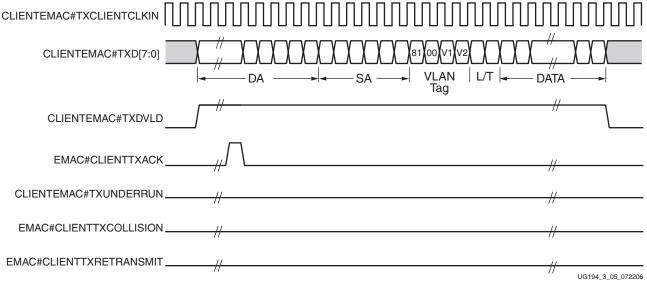

| Transmit (TX) Client: 8-Bit Interface (without Clock Enables) | . 52 |

|---------------------------------------------------------------|------|

| Normal Frame Transmission                                     | . 53 |

| In-Band Parameter Encoding                                    | . 53 |

| Padding                                                       | . 53 |

| Client-Supplied FCS Passing                                   | . 53 |

| Client Underrun                                               |      |

| Back-to-Back Transfers                                        | . 55 |

| Virtual LAN (VLAN) Tagged Frames                              | . 56 |

##

| Maximum Permitted Frame Length/Jumbo Frames                                                                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Frame Collisions - Half-Duplex 10/100 Mb/s Operation Only 56                                                                                                                                                                                                                                                                    |

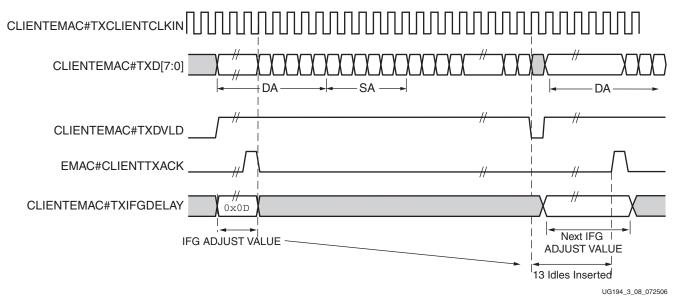

| IFG Adjustment                                                                                                                                                                                                                                                                                                                  |

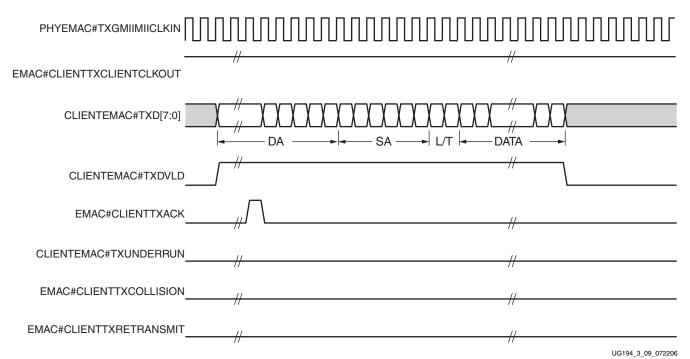

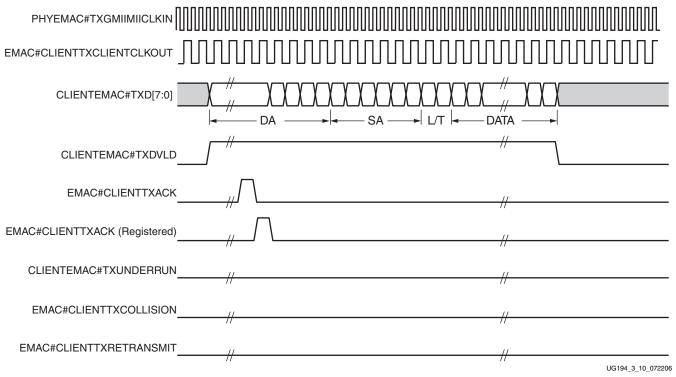

| Transmit (TX) Client: 8-Bit Interface (with Clock Enables)                                                                                                                                                                                                                                                                      |

| Normal Frame Transmission 59                                                                                                                                                                                                                                                                                                    |

| Transmit (TX) Client: 16-Bit Interface                                                                                                                                                                                                                                                                                          |

| Back-to-Back Transfers                                                                                                                                                                                                                                                                                                          |

| Receive (RX) Client: 8-Bit Interface (without Clock Enables)                                                                                                                                                                                                                                                                    |

| Normal Frame Reception                                                                                                                                                                                                                                                                                                          |

| Frame Reception with Errors                                                                                                                                                                                                                                                                                                     |

| Client-Supplied FCS Passing 66                                                                                                                                                                                                                                                                                                  |

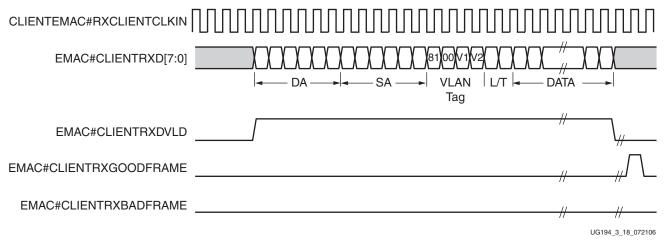

| VLAN Tagged Frames                                                                                                                                                                                                                                                                                                              |

| Maximum Permitted Frame Length/Jumbo Frames                                                                                                                                                                                                                                                                                     |

| Length/Type Field Error Checks                                                                                                                                                                                                                                                                                                  |

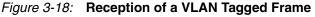

| Receive (RX) Client: 8-Bit Interface (with Clock Enables)                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                 |

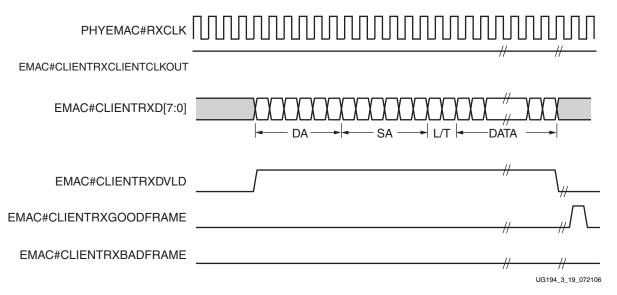

| Receive (RX) Client: 16-Bit Interface                                                                                                                                                                                                                                                                                           |

| <b>Receive (RX) Client: 16-Bit Interface</b>                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                 |

| Receive (RX) Client: 16-Bit Interface69Address Filtering71                                                                                                                                                                                                                                                                      |

| Receive (RX) Client: 16-Bit Interface69Address Filtering.71Address Filter Attributes71Client RX Data/Control Interface72                                                                                                                                                                                                        |

| Receive (RX) Client: 16-Bit Interface69Address Filtering.71Address Filter Attributes71Client RX Data/Control Interface72Flow Control Block.73                                                                                                                                                                                   |

| Receive (RX) Client: 16-Bit Interface69Address Filtering.71Address Filter Attributes71Client RX Data/Control Interface72Flow Control Block.73Requirement for Flow Control74                                                                                                                                                     |

| Receive (RX) Client: 16-Bit Interface69Address Filtering.71Address Filter Attributes71Client RX Data/Control Interface72Flow Control Block.73Requirement for Flow Control74Flow Control Basics74                                                                                                                                |

| Receive (RX) Client: 16-Bit Interface69Address Filtering.71Address Filter Attributes71Client RX Data/Control Interface72Flow Control Block.73Requirement for Flow Control74                                                                                                                                                     |

| Receive (RX) Client: 16-Bit Interface69Address Filtering.71Address Filter Attributes71Client RX Data/Control Interface72Flow Control Block.73Requirement for Flow Control74Flow Control Basics74Transmitting a PAUSE Control Frame75                                                                                            |

| Receive (RX) Client: 16-Bit Interface69Address Filtering.71Address Filter Attributes71Client RX Data/Control Interface72Flow Control Block.73Requirement for Flow Control74Flow Control Basics74Transmitting a PAUSE Control Frame75Receiving a PAUSE Control Frame75Flow Control Implementation Example76                      |

| Receive (RX) Client: 16-Bit Interface69Address Filtering.71Address Filter Attributes71Client RX Data/Control Interface72Flow Control Block.73Requirement for Flow Control74Flow Control Basics74Transmitting a PAUSE Control Frame75Receiving a PAUSE Control Frame75                                                           |

| Receive (RX) Client: 16-Bit Interface69Address Filtering.71Address Filter Attributes71Client RX Data/Control Interface72Flow Control Block.73Requirement for Flow Control74Flow Control Basics74Transmitting a PAUSE Control Frame75Receiving a PAUSE Control Frame75Flow Control Implementation Example76Statistics Vectors.78 |

## Chapter 4: Host/DCR Bus Interfaces

| Introduction to the Ethernet MAC Host Interface      | 85  |

|------------------------------------------------------|-----|

| Ethernet MAC Register Descriptions                   | 87  |

| Configuration Registers                              | 88  |

| Address Filter Registers                             | 94  |

| Using the Host Bus                                   | 97  |

| Clocking Requirements                                |     |

| Reading and Writing MAC Configuration Registers      |     |

| Reading and Writing Address Filter Registers         |     |

| PCS/PMA Sublayer or External Device Access via MDIO  | 100 |

| Using the DCR Bus                                    | 101 |

| Clocking Requirements                                |     |

| Device Control Registers                             | 102 |

| Interfacing to a Processor                           |     |

| DCR Interrupts                                       |     |

| Ethernet MAC Configuration and Address Filter Access |     |

| PCS/PMA Sublayer or External Device Access via MDIO  |     |

| Accessing FPGA Logic via Unused Host Bus Pins        | 113 |

## Chapter 5: MDIO Interface

| Introduction to MDIO                                           |

|----------------------------------------------------------------|

| MDIO Bus System                                                |

| MDIO Transactions 117                                          |

| MDIO Addressing                                                |

| MDIO Implementation in the Ethernet MAC                        |

| Accessing MDIO through the Host Interface                      |

| Accessing PCS/PMA Sublayer Management Registers using MDIO 121 |

| <b>1000BASE-X PCS/PMA Management Registers</b>                 |

| Link Status                                                    |

| SGMII Management Registers 130                                 |

## **Chapter 6: Physical Interface**

| Introduction to the Physical Interfaces 138                            |

|------------------------------------------------------------------------|

| Media Independent Interface (MII)                                      |

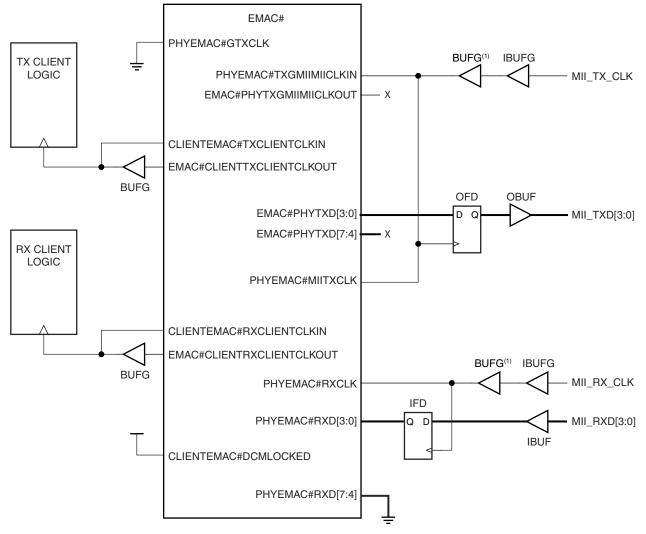

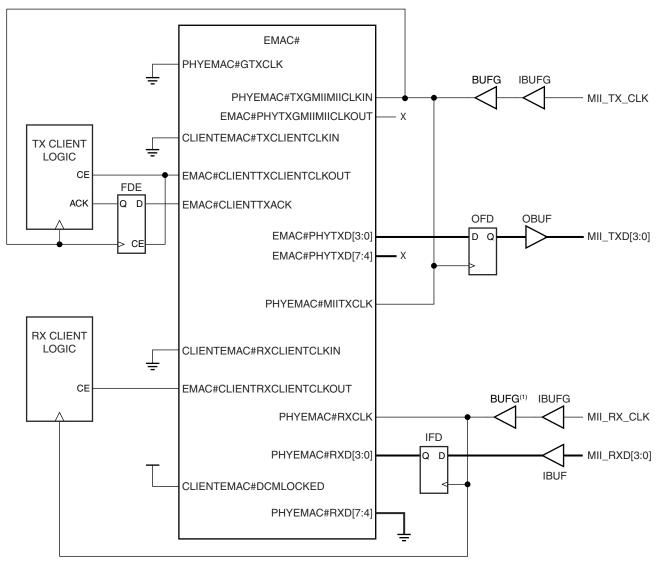

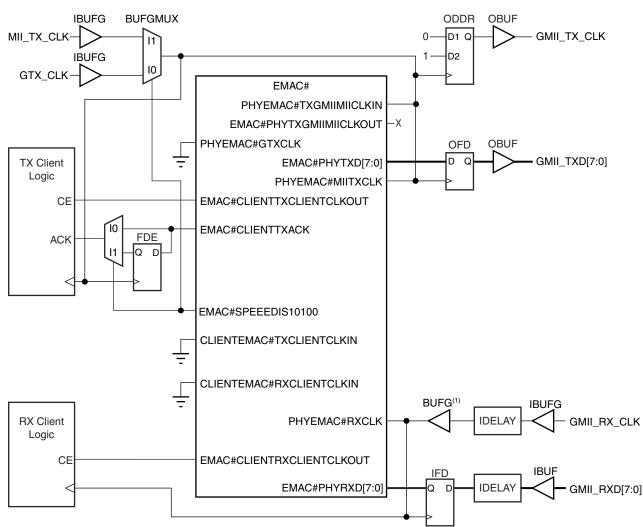

| MII Standard Clock Management 141                                      |

| MII Clock Management using Clock Enables 142                           |

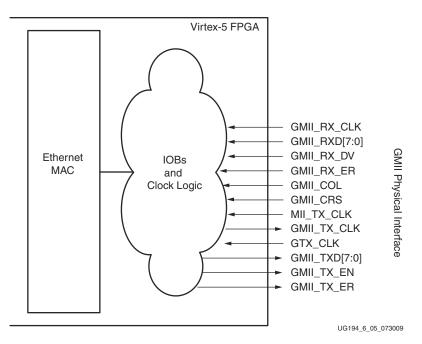

| Gigabit Media Independent Interface (GMII)                             |

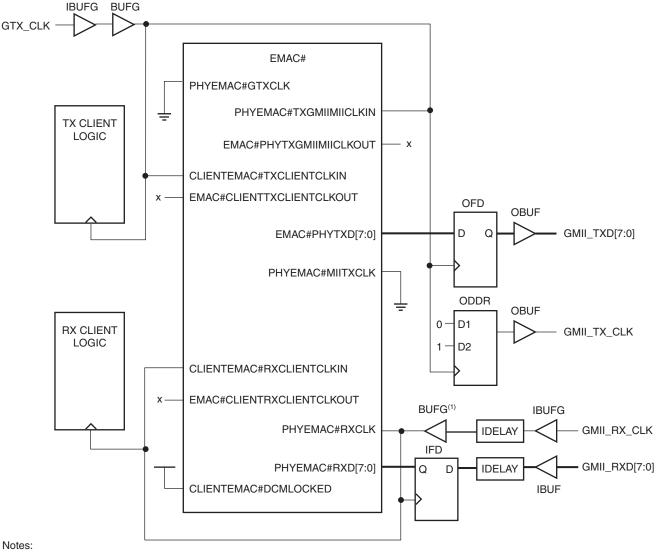

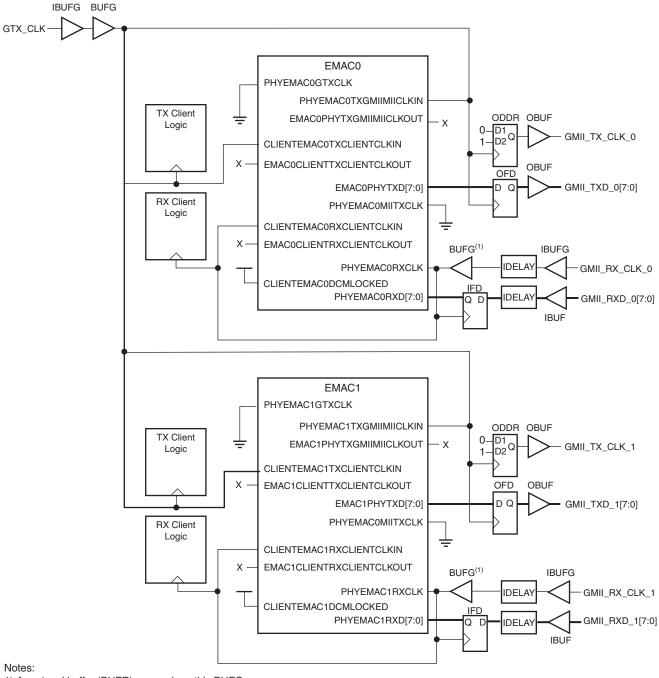

| GMII Clock Management for 1 Gb/s Only 144                              |

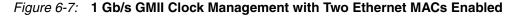

| GMII Standard Clock Management for Tri-Speed Operation                 |

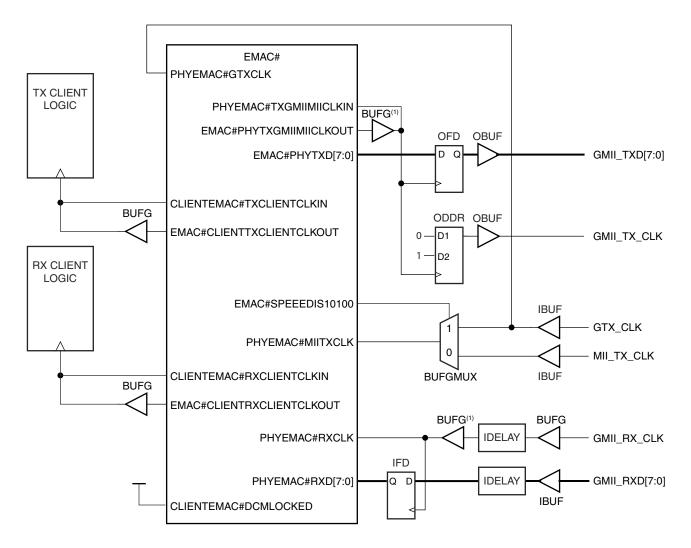

| GMII Clock Management for Tri-Speed Operation Using Byte PHY 149       |

| GMII Clock Management for Tri-Speed Operation Using Clock Enables 151  |

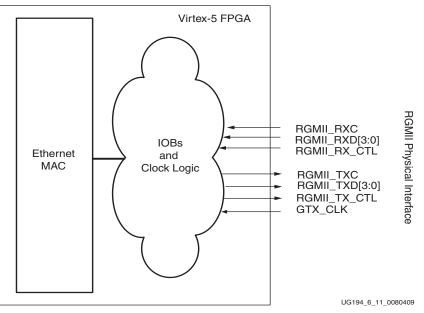

| Reduced Gigabit Media Independent Interface (RGMII)                    |

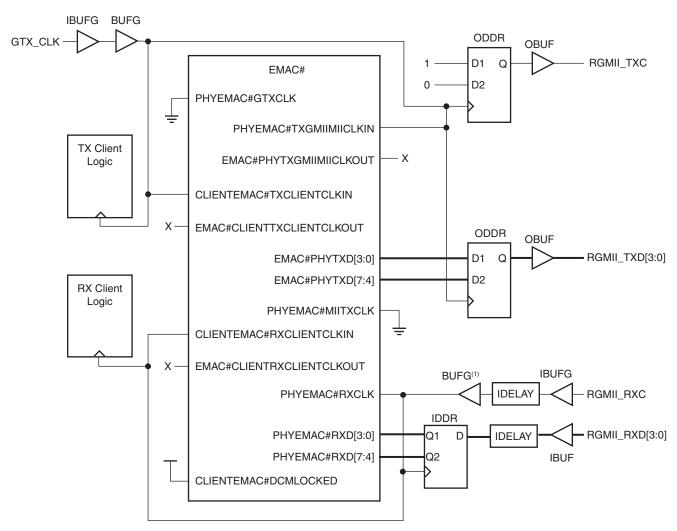

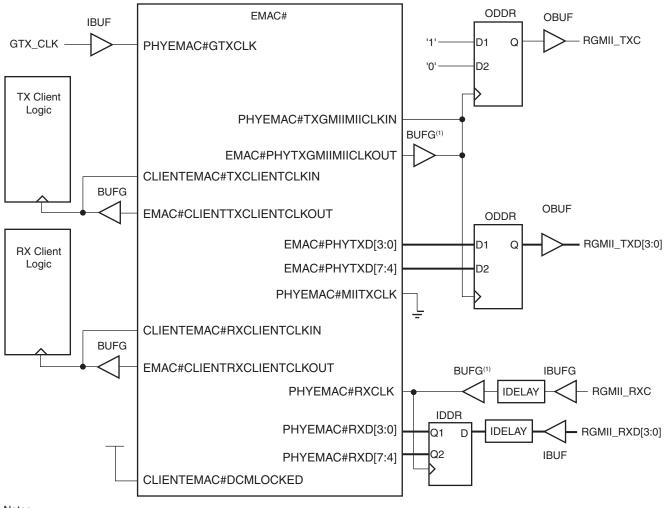

| RGMII Clock Management for 1 Gb/s Only 154                             |

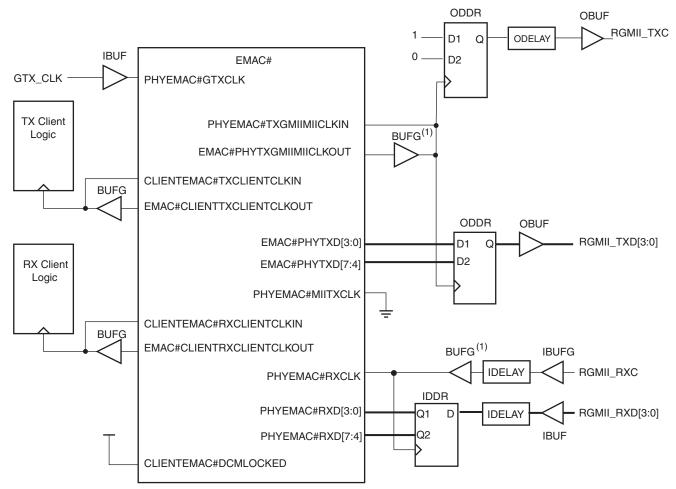

| RGMII Standard Clock Management for Tri-Speed Operation 157            |

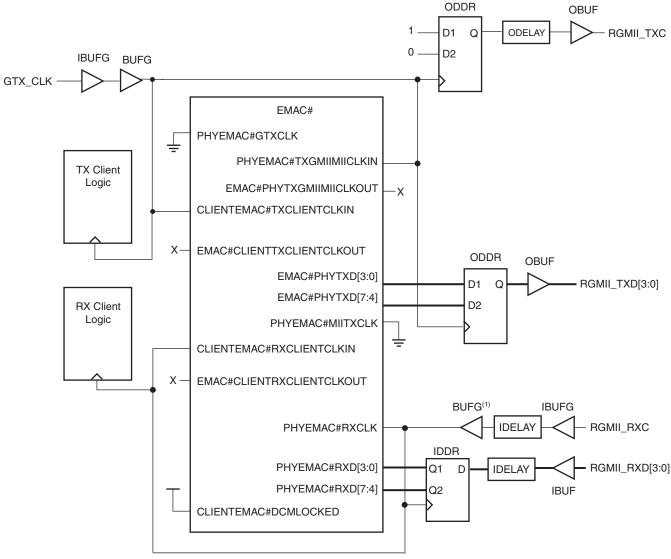

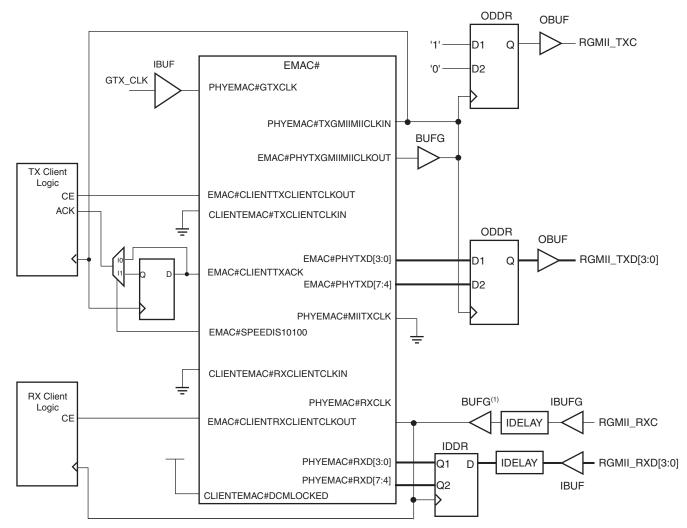

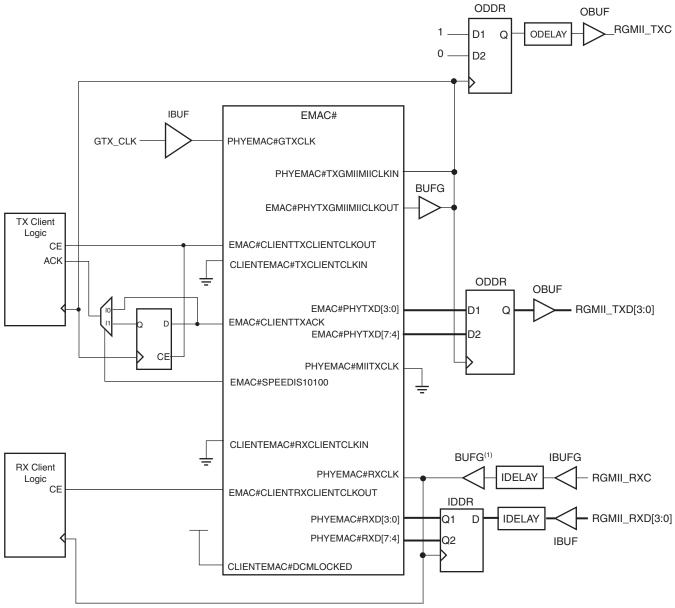

| RGMII Clock Management for Tri-Speed Operation Using Clock Enables 160 |

| <b>1000BASE-X PCS/PMA</b>                                              |

| Ethernet MAC PCS/PMA Sublayer 164                                      |

| Introduction to the 1000BASE-X PCS/PMA Implementation                  |

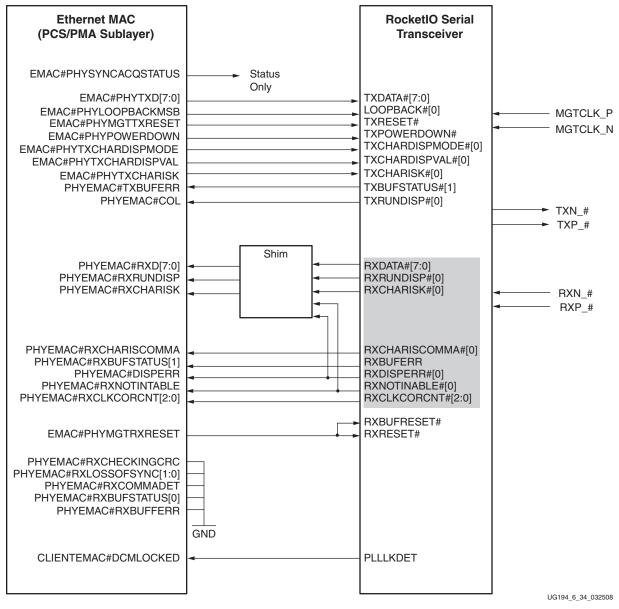

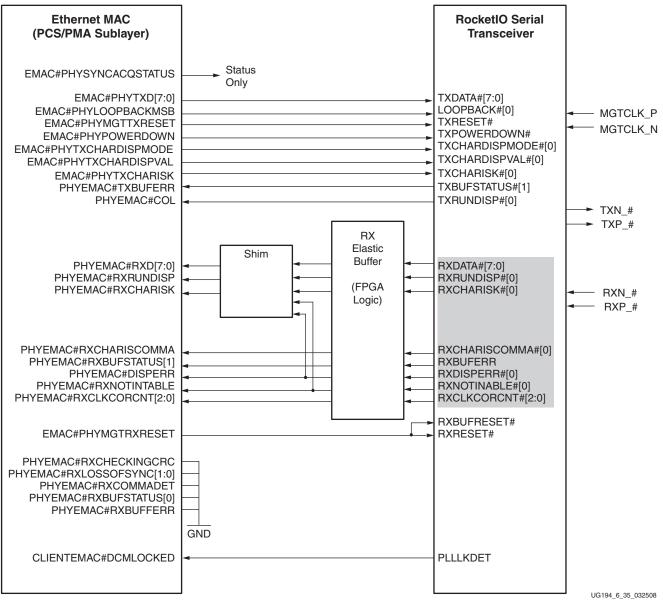

| Ethernet MAC to RocketIO Serial Transceiver Connections 167            |

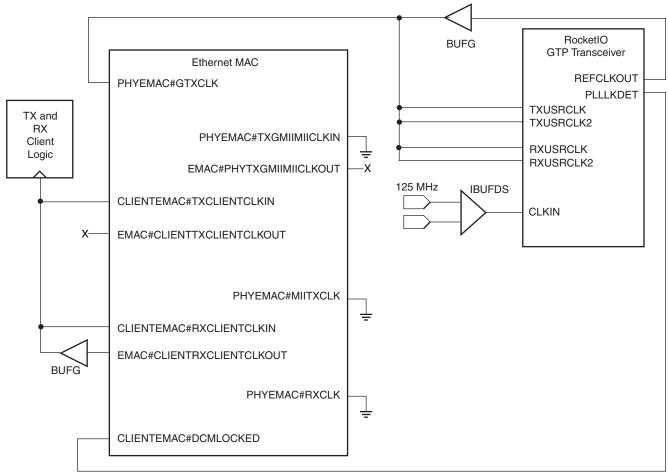

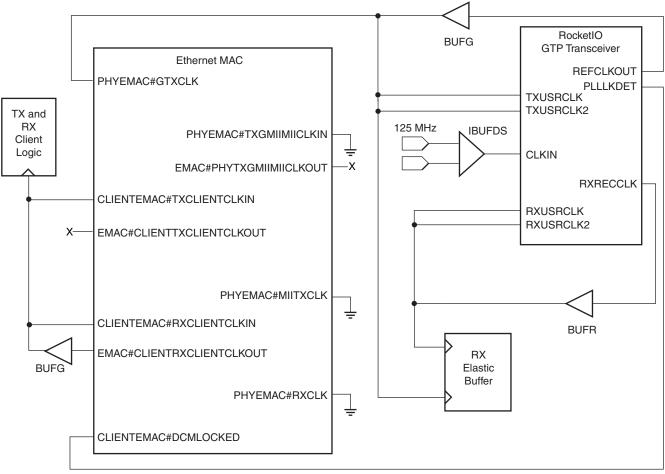

| 1000BASE-X PCS/PMA Clock Management (LXT and SXT Devices) 169          |

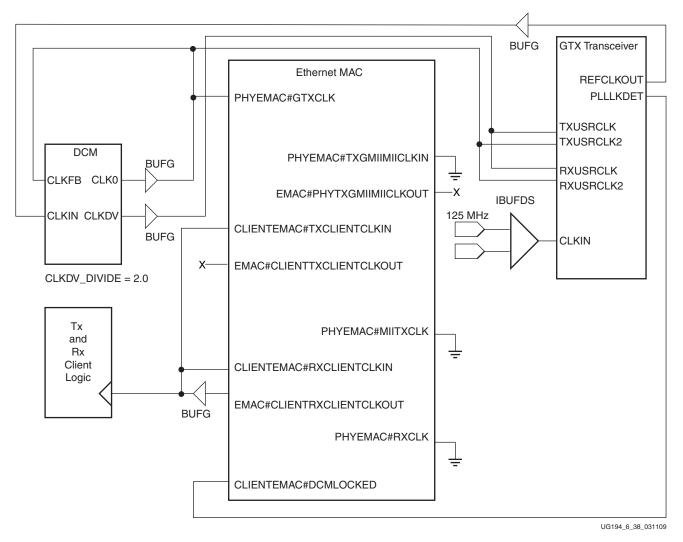

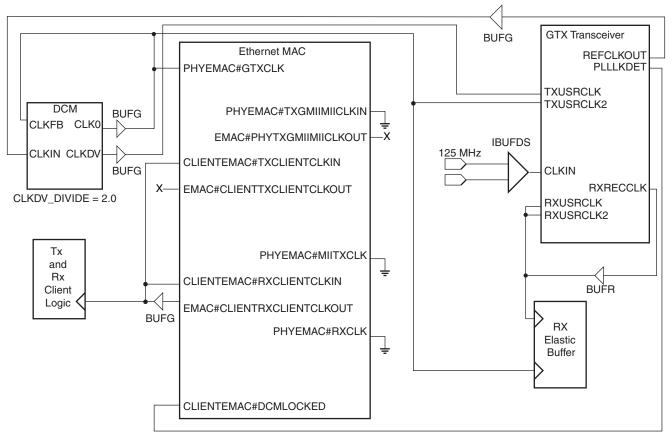

| 1000BASE-X PCS/PMA Clock Management (TXT and FXT Devices) 171          |

| 1000BASE-X Auto-Negotiation 174                                        |

| Loopback When Using the PCS/PMA Sublayer                               |

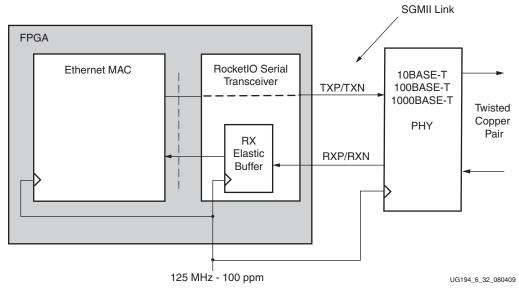

| Serial Gigabit Media Independent Interface (SGMII)                     |

| Ethernet MAC PCS/PMA Sublayer 178                                      |

| Introduction to the SGMII Implementation 179                           |

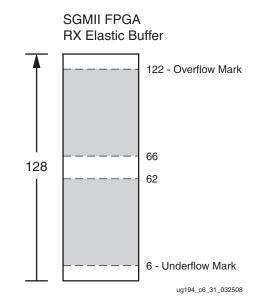

| SGMII RX Elastic Buffer 180                                            |

| SGMII Clock Management (LXT and SXT Devices)                           |

| SGMII Clock Management (TXT and FXT Devices) 193                       |

| SGMII Auto-Negotiation                                                 |

| Loopback When Using the PCS/PMA Sublayer 197                           |

## Chapter 7: Interfacing to a Statistics Block

| Using the Host Bus to Access Statistics Registers | 199 |

|---------------------------------------------------|-----|

| Using the DCR Bus to Access Statistics Registers  | 201 |

## **Appendix A: Pinout Guidelines**

## Appendix B: Ethernet MAC Clocks

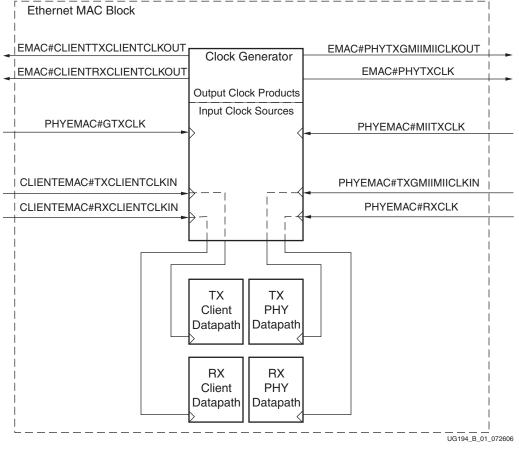

| Ethernet MAC Internal Clock Logic Overview          | . 205 |

|-----------------------------------------------------|-------|

| Ethernet MAC Clock Generation                       | . 206 |

| Ethernet MAC Input Clocks                           | . 206 |

| Clock Connections to and from FPGA Logic            | . 206 |

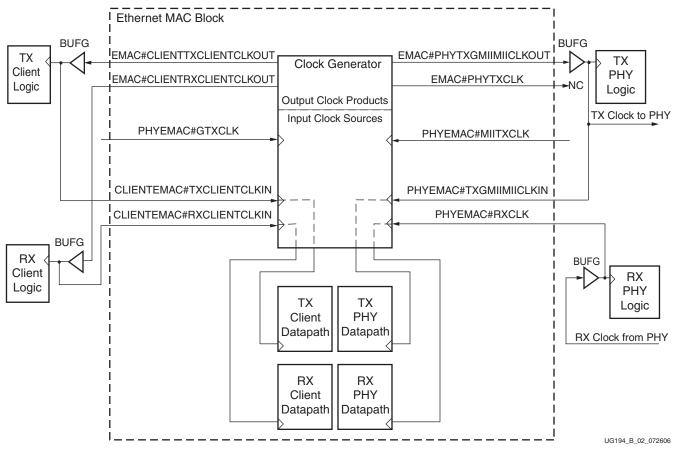

| Standard Clocking Scheme                            | . 207 |

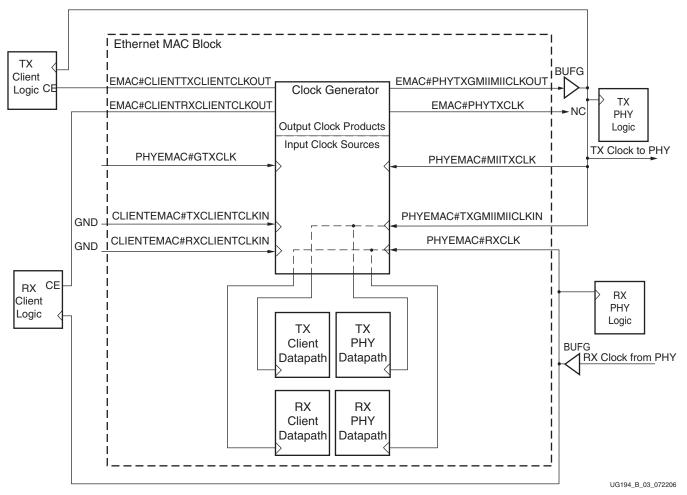

| Advanced Clocking Schemes                           | . 208 |

| Clock Definitions and Frequencies                   | . 211 |

| PHYEMAC#GTXCLK                                      | . 211 |

| PHYEMAC#MIITXCLK                                    | . 212 |

| PHYEMAC#RXCLK                                       | . 212 |

| EMAC#PHYTXGMIIMIICLKOUT, PHYEMAC#TXGMIIMIICLKIN     | . 213 |

| EMAC#PHYTXCLK                                       | . 214 |

| EMAC#CLIENTTXCLIENTCLKOUT, CLIENTEMAC#TXCLIENTCLKIN | . 214 |

| EMAC#CLIENTRXCLIENTCLKOUT, CLIENTEMAC#RXCLIENTCLKIN | . 215 |

## Appendix C: Virtex-4 to Virtex-5 FPGA Enhancements

| New Features                                    | 217 |

|-------------------------------------------------|-----|

| Unidirectional Enable                           | 217 |

| Programmable Auto-Negotiation Link Timer        | 217 |

| GT Loopback                                     |     |

| DCR Bus Modifications                           | 218 |

| Clocking Scheme Enhancements                    | 218 |

| Host Clock                                      | 218 |

| Advanced Clocking Schemes                       | 218 |

| Modifications Related to the Physical Interface | 219 |

| Collision Handling                              |     |

| RGMII Version 2.0 Clock Management              |     |

| Port Map Changes.                               | 219 |

| Tie-Off Pins Changed to Attributes              | 220 |

| Additional Attributes                           | 221 |

## Appendix D: Differences between Soft IP Cores and the Tri-Mode Ethernet MAC

| Features Exclusive to the Embedded Tri-Mode Ethernet MAC | . 223 |

|----------------------------------------------------------|-------|

| Features Exclusive to Soft IP Cores                      | . 223 |

## Preface

## About This Guide

This user guide is a description of the Virtex®-5 FPGA Embedded Tri-Mode Ethernet MAC. Complete and up-to-date documentation of the Virtex-5 family of FPGAs is available on the Xilinx® website at http://www.xilinx.com/virtex5.

### **Guide Contents**

This user guide contains the following chapters:

- Chapter 1, "Introduction," introduces the Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC and describes how to get started using the Ethernet MAC.

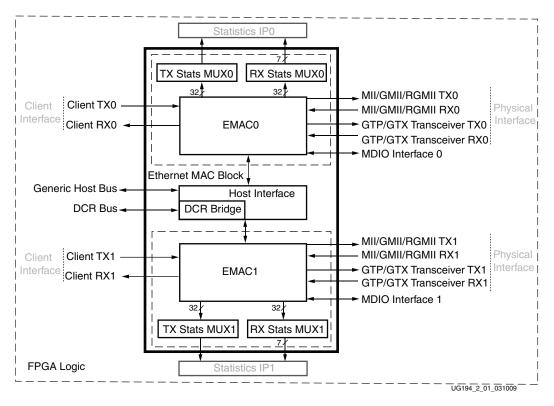

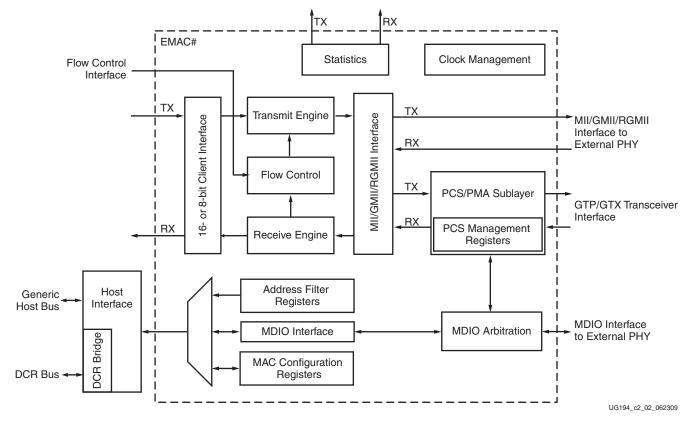

- Chapter 2, "Ethernet MAC Overview," describes the architecture of the Ethernet MAC, defines its signal interface, and gives an overview of its possible configurations.

- Chapter 3, "Client Interface," provides details of the client interface protocol and the Ethernet functionality associated with the client interface.

- Chapter 4, "Host/DCR Bus Interfaces," describes how to access registers in the Ethernet MAC using either the generic host bus or the DCR bus. The Ethernet MAC register descriptions are also found in this chapter.

- Chapter 5, "MDIO Interface," describes the MDIO interface protocol and the MDIO implementation in the Ethernet MAC. The SGMII and 1000BASE-X PCS/PMA management register descriptions are also found in this chapter.

- Chapter 6, "Physical Interface," describes all of the possible configurations for the physical interface and includes a description of optimized clocking schemes that can be used with the Ethernet MAC.

- Chapter 7, "Interfacing to a Statistics Block," provides details on how to use the Ethernet MAC with an FPGA logic-based statistics block.

- Appendix A, "Pinout Guidelines," lists recommendations to improve design timing when using the Virtex-5 FPGA Tri-Mode Ethernet MAC.

- Appendix B, "Ethernet MAC Clocks," gives an overview of the internal clock logic of the Ethernet MAC and summarizes the main clocking schemes. Definitions of each clock and its frequency, in all possible Ethernet MAC configurations, are also provided.

- Appendix C, "Virtex-4 to Virtex-5 FPGA Enhancements," documents some key enhancements and a few minor modifications.

- Appendix D, "Differences between Soft IP Cores and the Tri-Mode Ethernet MAC," explains the differences between soft IP cores and the Tri-Mode Ethernet MAC by listing the features exclusive to both.

## **Additional Documentation**

The following documents are also available for download at <u>http://www.xilinx.com/virtex5</u>.

- Virtex-5 Family Overview

The features and product selection of the Virtex-5 family are outlined in this overview.

- Virtex-5 FPGA Data Sheet: DC and Switching Characteristics

This data sheet contains the DC and Switching Characteristic specifications for the Virtex-5 family.

• Virtex-5 FPGA User Guide

This user guide includes chapters on:

- Clocking Resources

- Clock Management Technology (CMT)

- Phase-Locked Loops (PLLs)

- Block RAM

- Configurable Logic Blocks (CLBs)

- SelectIO<sup>TM</sup> Resources

- SelectIO Logic Resources

- Advanced SelectIO Logic Resources

- Virtex-5 FPGA RocketIO GTP Transceiver User Guide

This guide describes the RocketIO  $^{\rm TM}$  GTP transceivers available in the Virtex-5 LXT and SXT devices.

• Virtex-5 FPGA RocketIO GTX Transceiver User Guide

This guide describes the RocketIO GTX transceivers available in the Virtex-5 TXT and FXT devices.

• Virtex-5 FPGA Embedded Processor Block for PowerPC® 440 Designs

This reference guide is a description of the embedded processor block available in the Virtex-5 TXT and FXT devices.

• Virtex-5 FPGA Integrated Endpoint Block User Guide for PCI Express Designs

This guide describes the integrated Endpoint blocks in the Virtex-5 LXT, SXT, TXT, and FXT devices used for PCI Express® designs.

• XtremeDSP Design Considerations

This guide describes the XtremeDSP<sup>™</sup> slice and includes reference designs for using the DSP48E slice.

• Virtex-5 FPGA Configuration Guide

This all-encompassing configuration guide includes chapters on configuration interfaces (serial and SelectMAP), bitstream encryption, Boundary-Scan and JTAG configuration, reconfiguration techniques, and readback through the SelectMAP and JTAG interfaces.

• Virtex-5 FPGA System Monitor User Guide

The System Monitor functionality available in all the Virtex-5 devices is outlined in this guide.

• Virtex-5 FPGA Packaging and Pinout Specifications

This specification includes the tables for device/package combinations and maximum I/Os, pin definitions, pinout tables, pinout diagrams, mechanical drawings, and thermal specifications.

• Virtex-5 FPGA PCB Designer's Guide

This guide provides information on PCB design for Virtex-5 devices, with a focus on strategies for making design decisions at the PCB and interface level.

## **Additional Support Resources**

To search the database of silicon and software questions and answers, or to create a technical support case in WebCase, see the Xilinx website at: <u>http://www.xilinx.com/support</u>.

## **User Guide Conventions**

This document uses the following conventions.

#### Acronyms

Table 1-1 lists the acronyms and abbreviations that are used throughout this User Guide.

Table 1-1: Acronyms and Abbreviations in this User Guide

| Acronym  | Definition                                                                           |

|----------|--------------------------------------------------------------------------------------|

| Byte PHY | Name given to a particular Ethernet MAC clocking scheme described in this User Guide |

| CRC      | Cyclic Redundancy Check                                                              |

| CSMA/CD  | Carrier Sense Multiple Access with Collision Detection                               |

| DA       | Destination Address (MAC frame)                                                      |

| DCR      | Device Control Register                                                              |

| DMA      | Direct Memory Access                                                                 |

| EDK      | Embedded Development Kit (Xilinx software)                                           |

| FCS      | Frame Check Sequence (MAC frame)                                                     |

| FIFO     | First In, First Out memory                                                           |

| FPGA     | Field Programmable Gate Array                                                        |

| GBIC     | Gigabit Interface Converter (optical transceiver)                                    |

| Gb/s     | Gigabits per second                                                                  |

| GMII     | Gigabit Media Independent Interface                                                  |

| GTP      | High-speed serial transceivers offered in the Virtex-5 LXT and SXT platforms         |

| GTX      | High-speed serial transceivers offered in the Virtex-5 FXT and TXT platforms         |

| IFG      | Interframe Gap (MAC frame)                                                           |

www.xilinx.com

| Acronym | Definition                                                                                                                                                                                             |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IOB     | Input/Output Block                                                                                                                                                                                     |

| ISE     | Xilinx Integrated Software Environment                                                                                                                                                                 |

| L/T     | Length/Type field (MAC frame)                                                                                                                                                                          |

| LAN     | Local Area Network                                                                                                                                                                                     |

| MAC     | Media Access Controller                                                                                                                                                                                |

| Mb/s    | Megabits per second                                                                                                                                                                                    |

| MDIO    | Management Data Input/Output                                                                                                                                                                           |

| MII     | Media Independent Interface                                                                                                                                                                            |

| OP      | Operation code (read or write) for MDIO frame (sometimes called OPCODE in text)                                                                                                                        |

| OSI     | Open Systems Interconnection                                                                                                                                                                           |

| РСВ     | Printed Circuit Board                                                                                                                                                                                  |

| PCS     | Physical Coding Sublayer                                                                                                                                                                               |

| PHY     | Physical Layer                                                                                                                                                                                         |

|         | The term refers to all physical sublayers (PCS, PMA, PMD). Often<br>applied to a device, e.g., BASE-T PHY: an external chip which can<br>connect to the Ethernet MAC to perform this physical standard |

| PHYAD   | Physical Address (MDIO Frame)                                                                                                                                                                          |

| PLB     | Processor Local Bus                                                                                                                                                                                    |

| PMA     | Physical Medium Attachment                                                                                                                                                                             |

| PMD     | Physical Medium Dependent                                                                                                                                                                              |

| PRE     | Preamble (MDIO Frame)                                                                                                                                                                                  |

| REGAD   | Register Address (MDIO Frame)                                                                                                                                                                          |

| RGMII   | Reduced Gigabit Media Independent Interface                                                                                                                                                            |

| RX      | Receiver                                                                                                                                                                                               |

| SA      | Source Address (MAC frame)                                                                                                                                                                             |

| SFD     | Start of Frame Delimiter (MAC frame)                                                                                                                                                                   |

| SFP     | Small Form-factor Pluggable (optical transceiver)                                                                                                                                                      |

| SGMII   | Serial Gigabit Media Independent Interface                                                                                                                                                             |

| ST      | Start Code (MDIO Frame) or Start of Frame                                                                                                                                                              |

| Stats   | Abbreviation of Statistics                                                                                                                                                                             |

| TA      | Turnaround (MDIO Frame)                                                                                                                                                                                |

| TX      | Transmitter                                                                                                                                                                                            |

| VLAN    | Virtual Local Area Network                                                                                                                                                                             |

#### Table 1-1: Acronyms and Abbreviations in this User Guide

## Typographical

This document uses the following typographical conventions. An example illustrates each convention.

| Convention      | Meaning or Use                  | Example                                                  |

|-----------------|---------------------------------|----------------------------------------------------------|

| Italic font     | References to other documents   | See the <i>Virtex-5 User Guide</i> for more information. |

| nunc joni       | Emphasis in text                | The address (F) is asserted <i>after</i> clock event 2.  |

| Underlined Text | Indicates a link to a web page. | http://www.xilinx.com/virtex5                            |

### **Online Document**

The following conventions are used in this document:

| Convention            | Meaning or Use                                             | Example                                                                                                                 |

|-----------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Blue text             | Cross-reference link to a location in the current document | See the section "Additional<br>Documentation" for details.<br>Refer to "Address Filtering" in<br>Chapter 3 for details. |

| Blue, underlined text | Hyperlink to a website (URL)                               | Go to <u>http://www.xilinx.com</u><br>for the latest documentation.                                                     |

## Chapter 1

## Introduction

This chapter introduces the Virtex®-5 FPGA Embedded Tri-Mode Ethernet MAC and provides an overview of typical Ethernet applications and the Ethernet protocol. It also provides guidance on how to successfully incorporate the Virtex-5 FPGA Ethernet Media Access Controller (MAC) into a larger design using two alternative Xilinx® tools.

The Virtex-5 device family contains paired embedded Ethernet MACs that are independently configurable to meet all common Ethernet system connectivity needs. Table 1 in the *Virtex-5 Family Overview* lists the device type versus the number of available Ethernet MACs.

This chapter contains the following sections:

- "Key Features"

- "Typical Ethernet Application Overview"

- "Ethernet Protocol Overview"

- "Using the Embedded Ethernet MAC"

### **Key Features**

The key features of the Virtex-5 FPGA Ethernet MAC are:

- Fully integrated 10/100/1000 Mb/s Ethernet MAC

- Designed to the IEEE Std 802.3-2002 specification

- Configurable full-duplex operation in 10/100/1000 Mb/s

- Configurable half-duplex operation in 10/100 Mb/s

- Management Data Input/Output (MDIO) interface to manage objects in the physical layer

- User-accessible raw statistic vector outputs

- Support for VLAN frames

- Configurable interframe gap (IFG) adjustment in full-duplex operation

- Configurable in-band Frame Check Sequence (FCS) field passing on both transmit and receive paths

- Auto padding on transmit and stripping on receive paths

- Configured and monitored through a host interface

- Hardware-selectable Device Control Register (DCR) bus or generic host bus interface

- Configurable flow control through Ethernet MAC Control PAUSE frames; symmetrically or asymmetrically enabled

- Configurable support for jumbo frames of any length

- Configurable receive address filter for unicast, general, and broadcast addresses

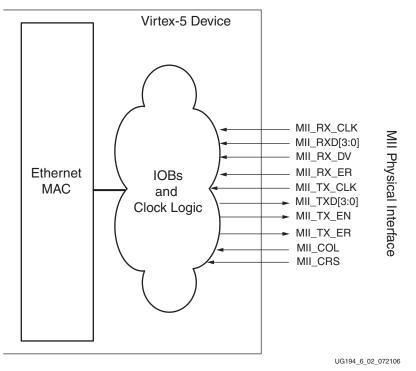

- Media Independent Interface (MII), Gigabit Media Independent Interface (GMII), and Reduced Gigabit Media Independent Interface (RGMII)

- 1000BASE-X Physical Coding Sublayer (PCS) and a Physical Medium Attachment (PMA) sublayer included for use with the Virtex-5 RocketIO<sup>™</sup> serial transceivers to provide a complete on-chip 1000BASE-X implementation

- Serial Gigabit Media Independent Interface (SGMII) supported through the RocketIO serial transceivers' interfaces to external copper PHY layer for full-duplex operation

## **Typical Ethernet Application Overview**

Typical applications for the Ethernet MAC include:

- "Ethernet Switch or Router"

- "Ethernet Communications Port for an Embedded Processor"

### Ethernet Switch or Router

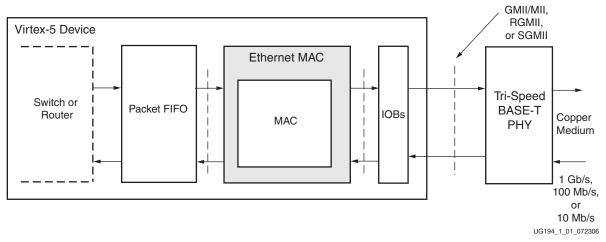

Figure 1-1 illustrates a typical application for a single Ethernet MAC. The PHY side of the core is connected to an off-the-shelf Ethernet PHY device, which performs the BASE-T standard at 1 Gb/s, 100 Mb/s, and 10 Mb/s speeds. The PHY device can be connected using any of the following supported interfaces: GMII/MII, RGMII, or SGMII.

The client side of the Embedded Ethernet MAC is connected to a FIFO to complete a single Ethernet port. This port is connected to a Switch or Routing matrix, which can contain several ports.

For this application, the recommended place to start is in "Accessing the Ethernet MAC from the CORE Generator Tool," page 25. The CORE Generator<sup>TM</sup> tool provides an example design for the Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC for any of the supported physical interfaces. A FIFO example is also generated, which can be used as the FIFO in the illustration, for a typical application.

Figure 1-1: Typical Application: Ethernet Switch or Router

### Ethernet Communications Port for an Embedded Processor

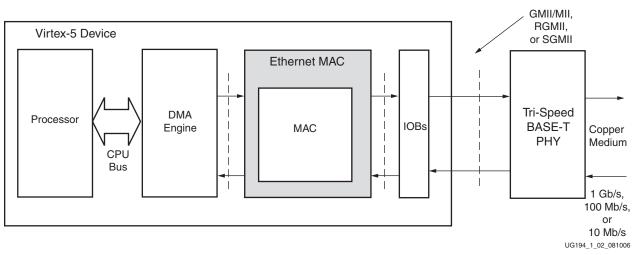

Figure 1-2 illustrates a typical application for a single Ethernet MAC. The PHY side of the core is connected to an off-the-shelf Ethernet PHY device, which performs the BASE-T standard at 1 Gb/s, 100 Mb/s, and 10 Mb/s speeds. The PHY device can be connected using any of the following supported interfaces: GMII/MII, RGMII, or SGMII.

A soft core is provided as part of the Xilinx Platform Studio (XPS), Embedded Development Kit (EDK) IP portfolio to connect the client interface of the Embedded Ethernet MAC to the DMA port of a processor. <u>DS537</u>, *XPSLL TEMAC Data Sheet*, describes the XPS\_LL\_TEMAC, which can be instantiated for an intended processor application.

Figure 1-2: Typical Application: Ethernet Communications Port for Embedded Processor

### **Ethernet Protocol Overview**

This section gives an overview of where the Ethernet MAC fits into an Ethernet system and provides a description of some basic Ethernet terminology.

#### Ethernet Sublayer Architecture

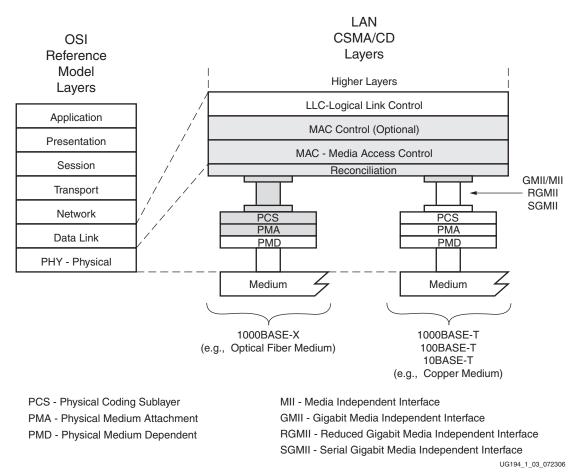

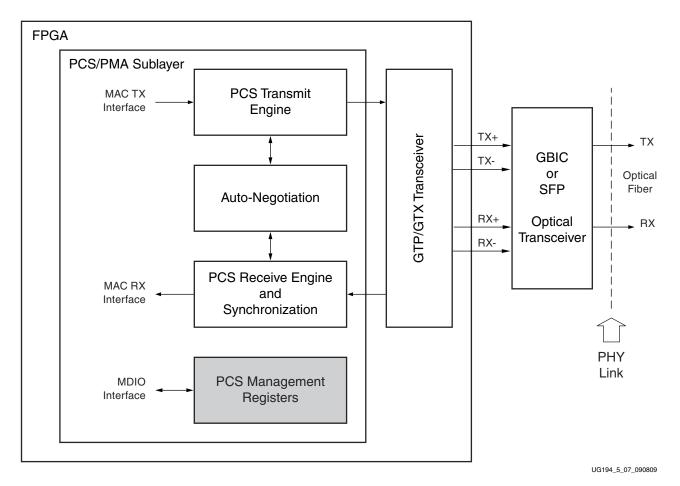

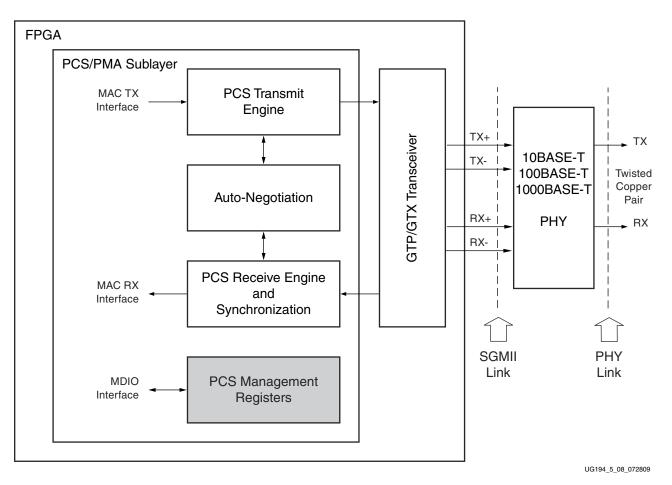

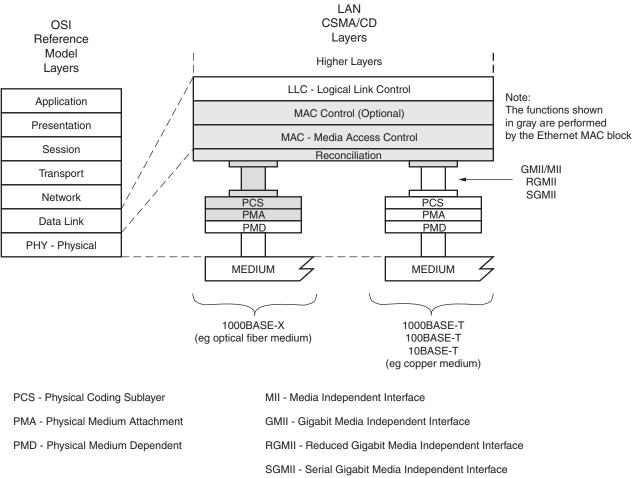

Figure 1-3 illustrates the relationship between the OSI reference model and the Ethernet MAC, as defined in the IEEE 802.3 specification. The grayed-in layers show the functionality that the Ethernet MAC handles. Figure 1-3 also shows where the supported physical interfaces fit into the architecture.

#### MAC and MAC CONTROL Sublayer

The Ethernet MAC is defined in the IEEE 802.3 specification in clauses 2, 3, and 4. A MAC is responsible for the Ethernet framing protocols described in "Ethernet Data Format" and error detection of these frames. The MAC is independent of and can connect to any type of physical layer device.

The MAC Control sublayer is defined in the IEEE 802.3 specification, clause 31. This provides real-time flow control manipulation of the MAC sublayer.

Both the MAC CONTROL and MAC sublayers are provided by the Ethernet MAC in all modes of operation.

#### Physical Sublayers PCS, PMA, and PMD

The combination of the Physical Coding Sublayer (PCS), the Physical Medium Attachment (PMA), and the Physical Medium Dependent (PMD) sublayer constitute the physical layers for the protocol. Two main physical standards are specified:

- **BASE-T** PHYs provide a link between the MAC and copper mediums. This functionality is not offered within the Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC. However, external BASE-T PHY devices are readily available on the market. These can connect to the Ethernet MAC, using GMII/MII, RGMII, or SGMII interfaces.

- **BASE-X** PHYs provide a link between the MAC and (usually) fibre optic mediums. The Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC is capable of supporting the 1 Gb/s BASE-X standard; 1000BASE-X PCS and PMA sublayers can be offered by connecting the Ethernet MAC to a RocketIO serial transceiver. An optical transceiver can be directly connected to the RocketIO serial transceiver to complete the PMD sublayer functionality.

#### **Ethernet Data Format**

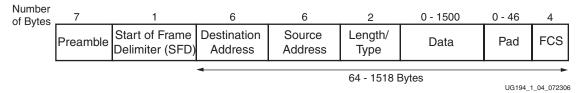

Ethernet data is encapsulated in frames, as shown in Figure 1-4, for standard Ethernet frames. The fields in the frame are transmitted from left to right. The bytes within the frame are transmitted from left to right (from least significant bit to most significant bit unless specified otherwise). The Ethernet MAC can handle jumbo Ethernet frames where the data field can be much larger than 1500 bytes.

Figure 1-4: Standard Ethernet Frame Format

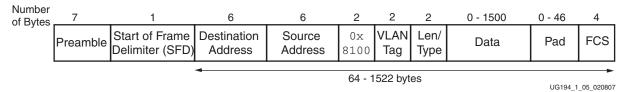

The Ethernet MAC can also accept VLAN frames. The VLAN frame format is shown in Figure 1-5. If the frame is a VLAN type frame, the Ethernet MAC accepts four additional bytes.

Figure 1-5: Ethernet VLAN Frame Format

Ethernet pause/flow control frames can be transmitted and received by the Ethernet MAC. Figure 3-29, page 75 shows how a pause/flow control frame differs from the standard Ethernet frame format.

The following subsections describe the individual fields of an Ethernet frame and some basic functionality of the Ethernet MAC.

#### Preamble

For transmission, this field is automatically inserted by the Ethernet MAC. The preamble field was historically used for synchronization and contains seven bytes with the pattern 0x55, transmitted from left to right. For reception, this field is always stripped from the incoming frame, before the data is passed to the client. The Ethernet MAC can receive Ethernet frames, even if the preamble does not exist, as long as a valid start of frame is available.

#### Start of Frame Delimiter

The start of frame delimiter field marks the start of the frame and must contain the pattern 0xD5.

For transmission on the physical interface, this field is automatically inserted by the Ethernet MAC. For reception, this field is always stripped from the incoming frame before the data is passed to the client.

#### **Destination Address**

The least significant bit of the destination address determines if the address is an individual/unicast (0) or group/multicast (1) address. Multicast addresses are used to group logically related stations. The broadcast address (destination address field is all 1s) is a multicast address that addresses all stations on the LAN. The Ethernet MAC supports transmission and reception of unicast, multicast, and broadcast packets.

This field is the first field of the Ethernet frame that is always provided in the packet data for transmissions and is always retained in the receive packet data.

#### Source Address

For transmission, the source address of the Ethernet frame should be provided by the client because it is unmodified by the Ethernet MAC. The unicast address for the Ethernet MAC is used as the source address when the Ethernet MAC creates pause control frames. The source address field is always retained in the receive packet data.

#### Length/Type

The value of this field determines if it is interpreted as a length or a type field, as defined by the IEEE 802.3 standard. A value of 1536 decimal or greater is interpreted by the Ethernet MAC as a type field.

When used as a length field, the value in this field represents the number of bytes in the following data field. This value does not include any bytes that can be inserted in the pad field following the data field.

A length/type field value of  $0 \times 8100$  hex indicates that the frame is a VLAN frame, and a value of  $0 \times 8808$  hex indicates a pause MAC control frame.

For transmission, the Ethernet MAC does not perform any processing of the length/type field.

For reception, if this field is a length field, the Ethernet MAC receive engine interprets this value and removes any padding in the pad field (if necessary). If the field is a length field and length/type checking is enabled, the Ethernet MAC compares the length against the actual data field length and flags an error if a mismatch occurs. If the field is a type field, the Ethernet MAC ignores the value and passes it along with the packet data with no further processing. The length/type field is always retained in the receive packet data.

#### Data

The data field can vary from 0 to 1500 bytes in length for a normal frame. The Ethernet MAC can handle jumbo frames of any length.

This field is always provided in the packet data for transmissions and is always retained in the receive packet data.

#### Pad

The pad field can vary from 0 to 46 bytes in length. This field is used to ensure that the frame length is at least 64 bytes in length (the preamble and SFD fields are not considered part of the frame for this calculation), which is required for successful CSMA/CD operation. The values in this field are used in the frame check sequence calculation but are not included in the length field value, if it is used. The length of this field and the data field combined must be at least 46 bytes. If the data field contains 0 bytes, the pad field is 46 bytes. If the data field has 0 bytes.

For transmission, this field can be inserted automatically by the Ethernet MAC or can be supplied by the client. If the pad field is inserted by the Ethernet MAC, the FCS field is calculated and inserted by the Ethernet MAC. If the pad field is supplied by the client, the FCS can be either inserted by the Ethernet MAC or provided by the client, as indicated by a configuration register bit.

For reception, if the length/type field has a length interpretation, any pad field in the incoming frame is not be passed to the client, unless the Ethernet MAC is configured to pass the FCS field on to the client.

#### FCS

The value of the FCS field is calculated over the destination address, source address, length/type, data, and pad fields using a 32-bit Cyclic Redundancy Check (CRC), as defined in IEEE Std 802.3-2002 para. 3.2.8:

$G(x) = x^{32} + x^{26} + x^{23} + x^{22} + x^{16} + x^{12} + x^{11} + x^{10} + x^8 + x^7 + x^5 + x^4 + x^2 + x^1 + x^0$

The CRC bits are placed in the FCS field with the  $x^{31}$  term in the left-most bit of the first byte, and the  $x^0$  term is the right-most bit of the last byte (i.e., the bits of the CRC are transmitted in the order  $x^{31}$ ,  $x^{30}$ ,...,  $x^1$ ,  $x^0$ ).

For transmission, this field can be either inserted automatically by the Ethernet MAC or supplied by the client, as indicated by a configuration register bit.

For reception, the incoming FCS value is verified on every frame. If an incorrect FCS value is received, the Ethernet MAC indicates to the client that it has received a bad frame. The FCS field can either be passed on to the client or be dropped by the Ethernet MAC, as indicated by a configuration register bit.

#### Frame Transmission and Interframe Gap

Frames are transmitted over the Ethernet medium with an interframe gap, as specified by IEEE Std 802.3. For full-duplex systems, the minimum IFG is 96 bit times (9.6 µs for 10 Mb/s, 0.96 µs for 100 Mb/s, and 96 ns for 1 Gb/s). For half-duplex systems, the minimum IFG is 208 bit times and 144 bit times for RGMII and MII respectively. The defined IFG is a minimum and can be increased with a resulting decrease in throughput.

The process for frame transmission is different for half-duplex and full-duplex systems.

#### Half-Duplex Frame Transmission

In a half-duplex system, the CSMA/CD media access method defines how two or more stations share a common medium.

- Even when it has nothing to transmit, the Ethernet MAC monitors the Ethernet medium for traffic by watching the carrier sense signal (CRS) from the external PHY. Whenever the medium is busy (CRS = 1), the Ethernet MAC defers to the passing frame by delaying any pending transmission of its own.

- 2. After the last bit of the passing frame (when the carrier sense signal changes from TRUE to FALSE), the Ethernet MAC starts the timing of the interframe gap.

- 3. The Ethernet MAC resets the interframe gap timer if the carrier sense becomes TRUE during the period defined by "interframe gap part 1 (IFG1)." The IEEE Std 802.3 states that this should be the first 2/3 of the interframe gap timing interval (64 bit times) but can be shorter and as small as zero. The purpose of this option is to support a possible brief failure of the carrier sense signal during a collision condition and is described in paragraph 4.2.3.2.1 of the IEEE standard.

- 4. The Ethernet MAC does not reset the interframe gap timer if carrier sense becomes TRUE during the period defined by "interframe gap part 2 (IFG2)" to ensure fair access to the bus. The IEEE Std 802.3 states that this should be the last 1/3 of the interframe gap timing interval.

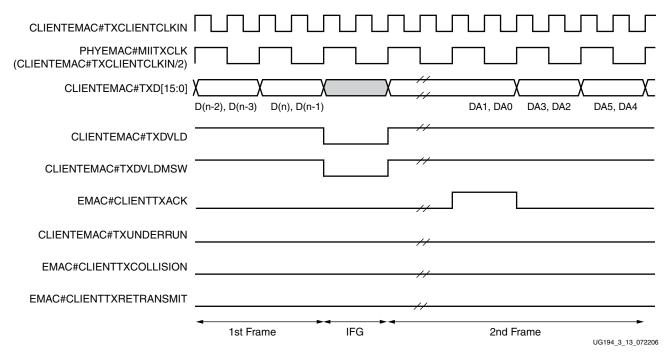

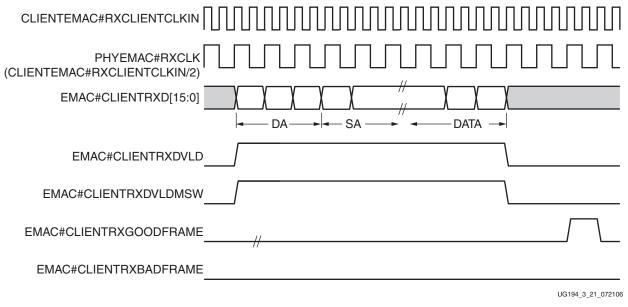

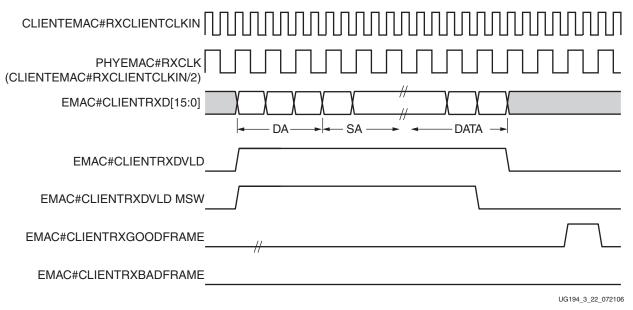

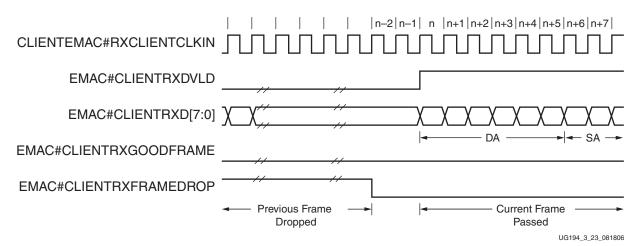

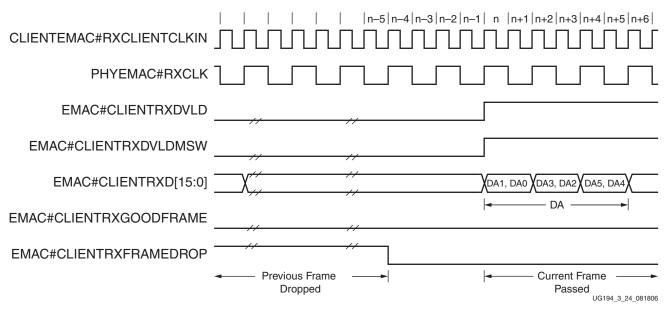

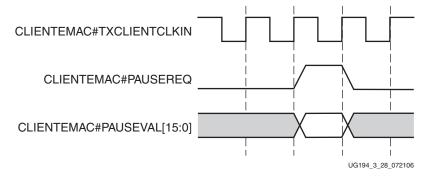

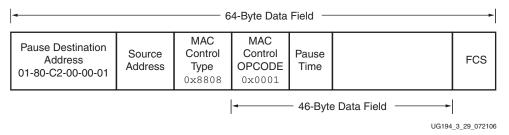

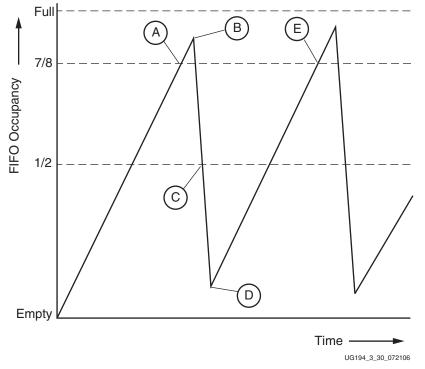

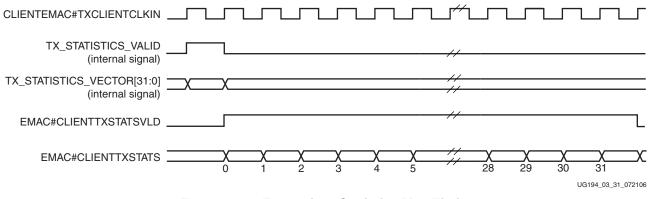

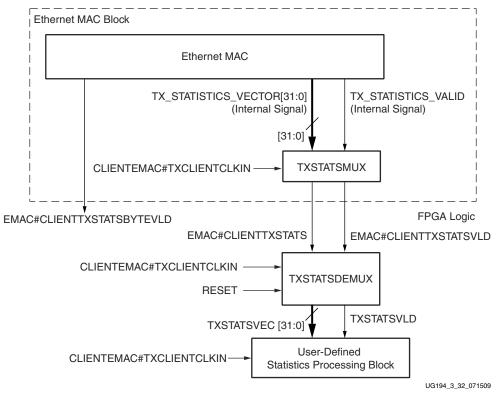

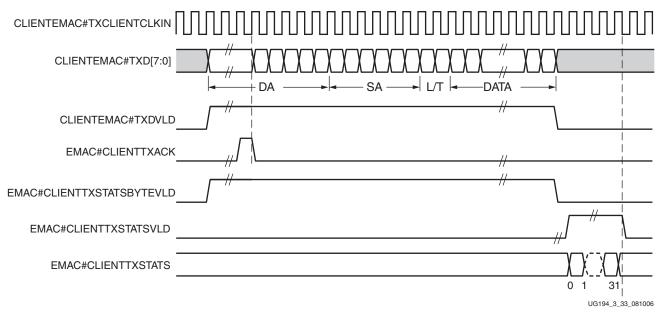

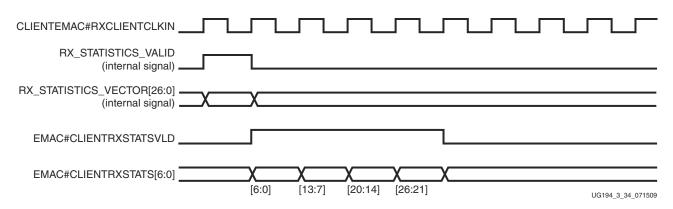

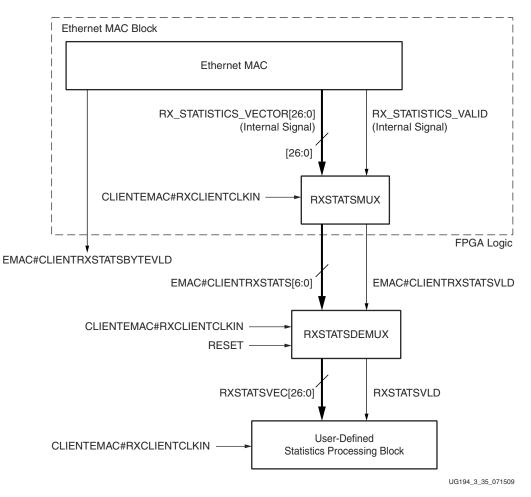

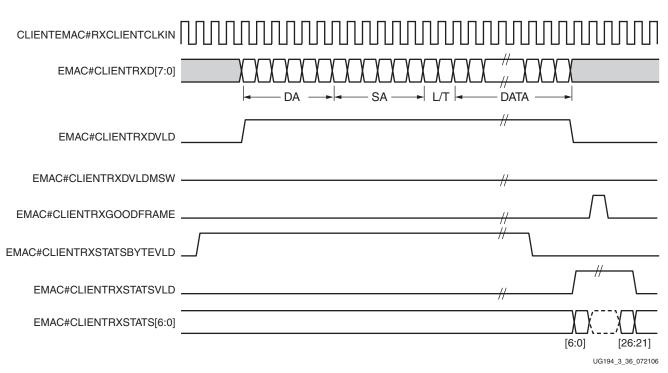

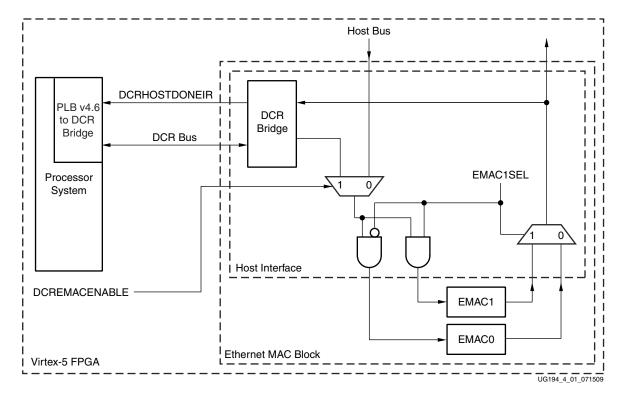

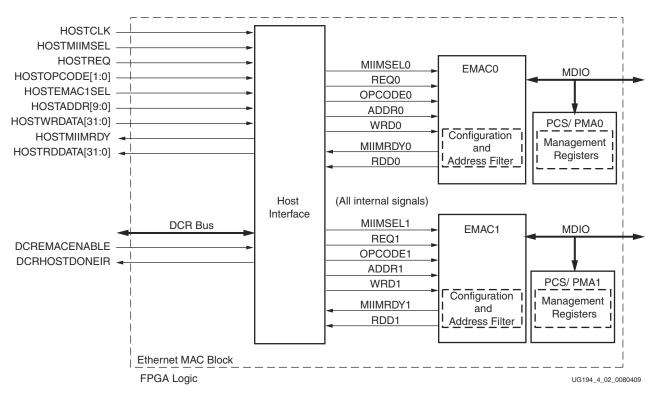

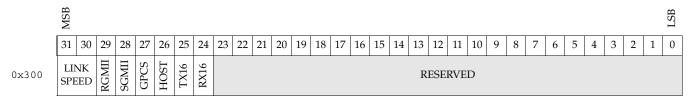

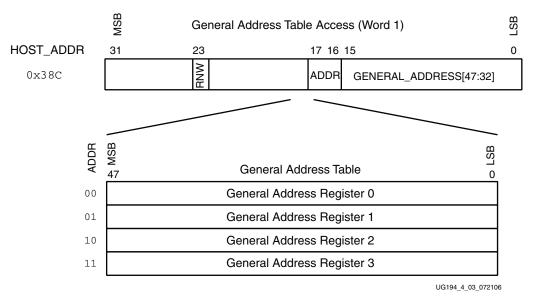

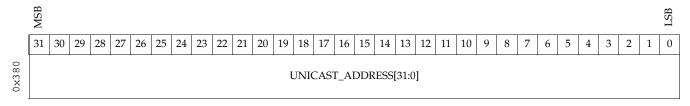

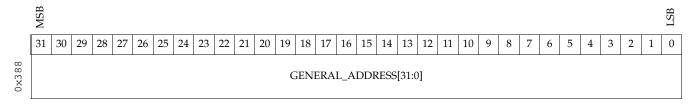

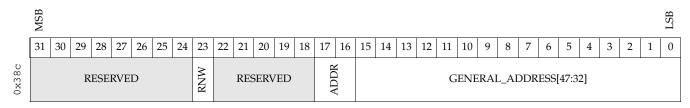

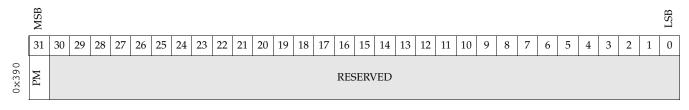

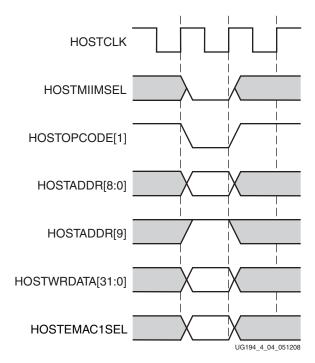

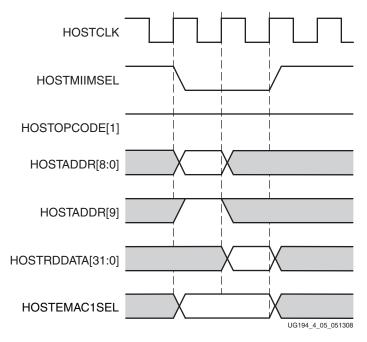

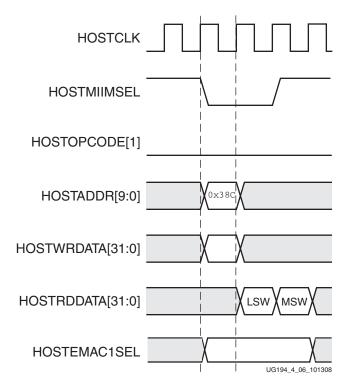

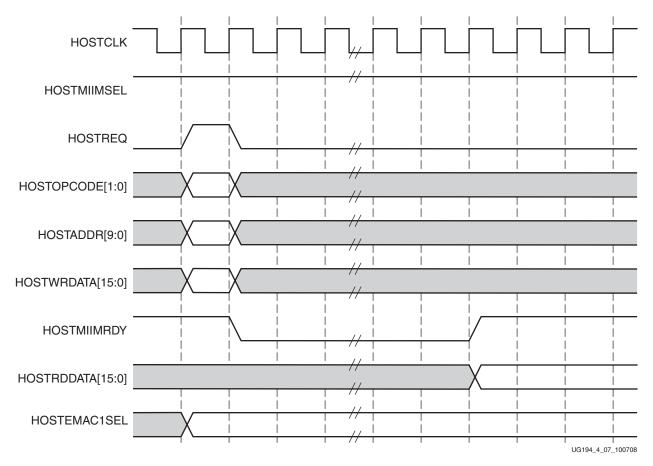

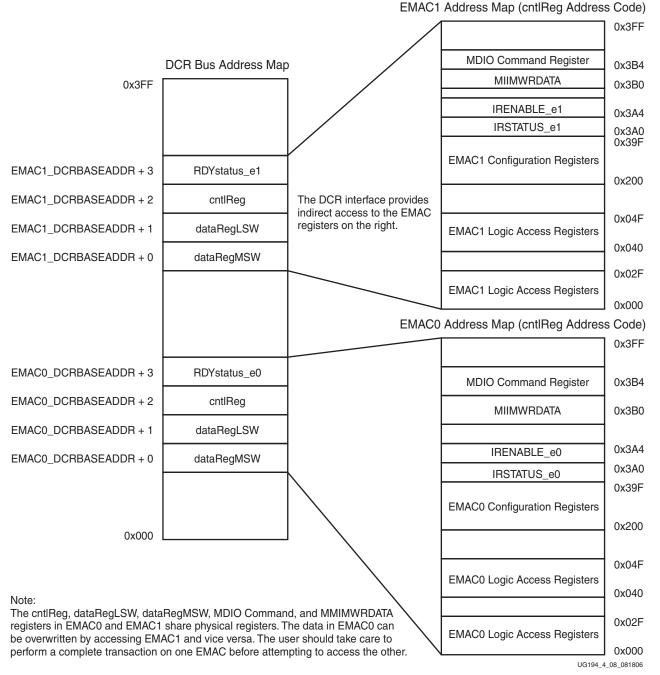

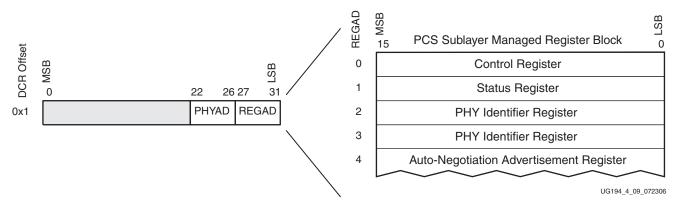

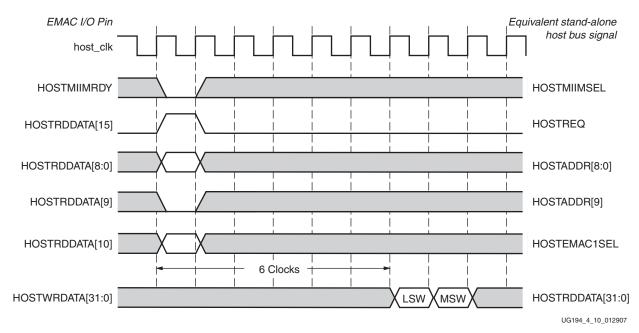

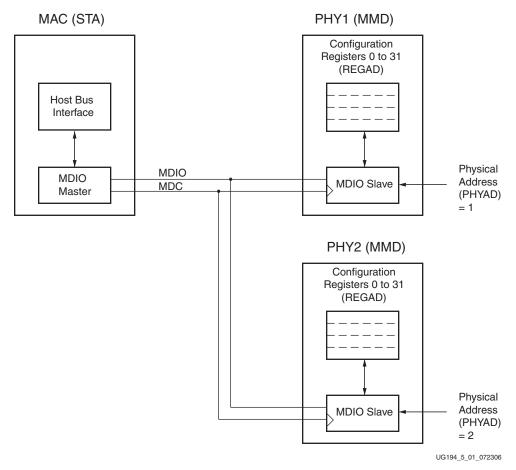

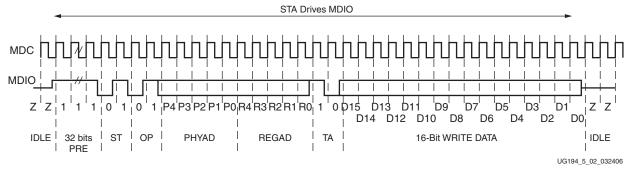

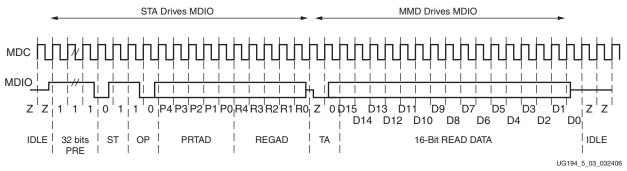

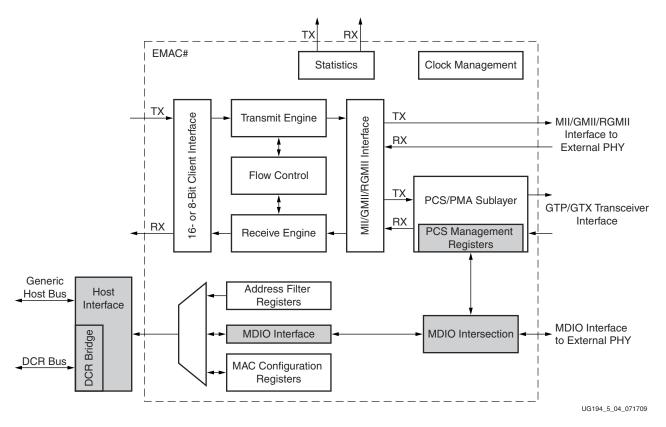

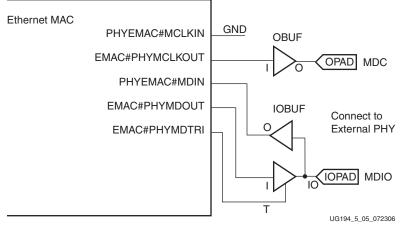

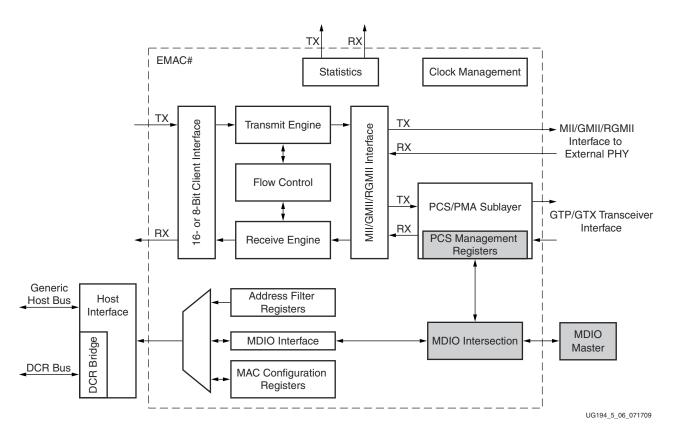

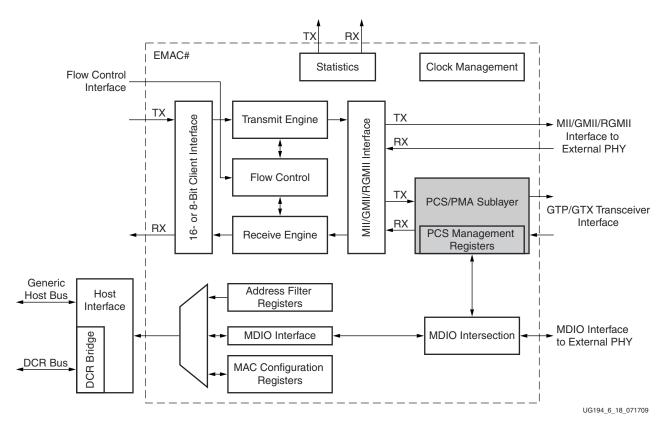

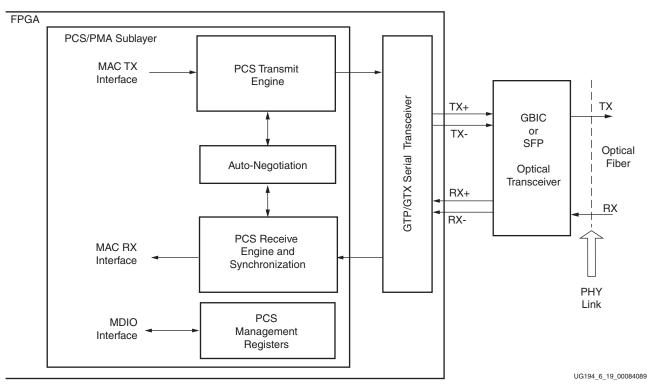

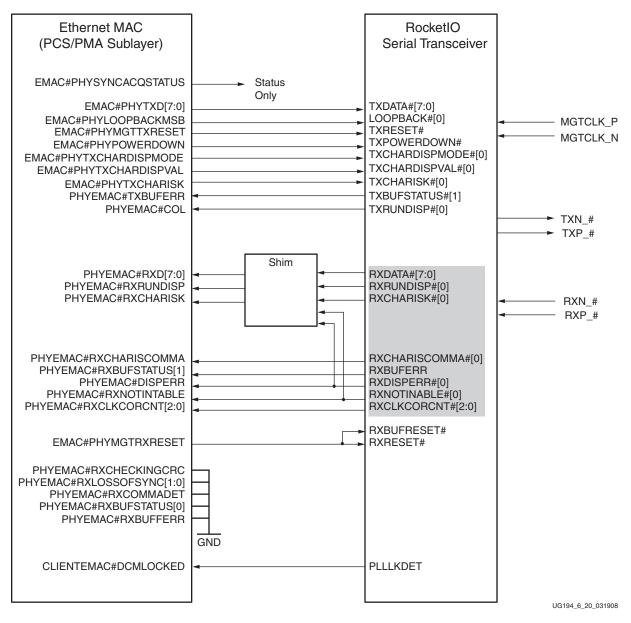

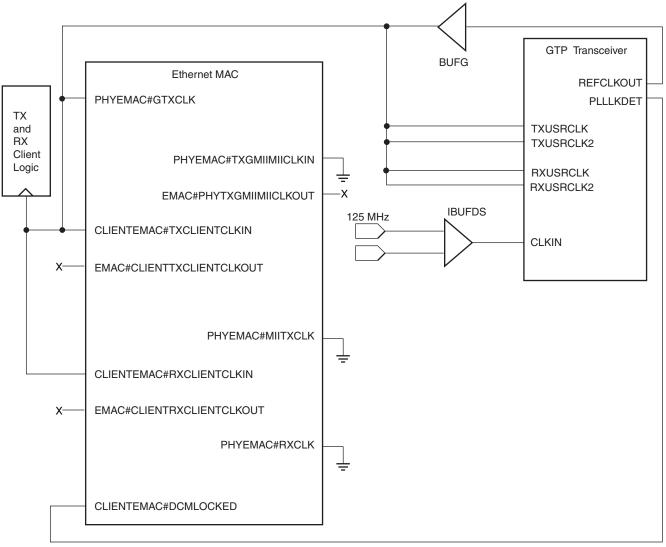

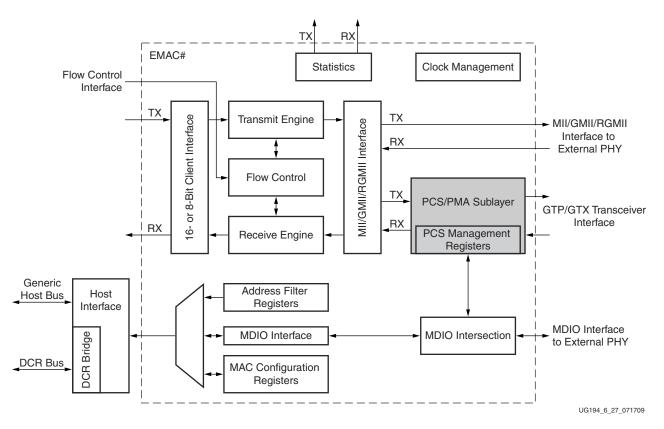

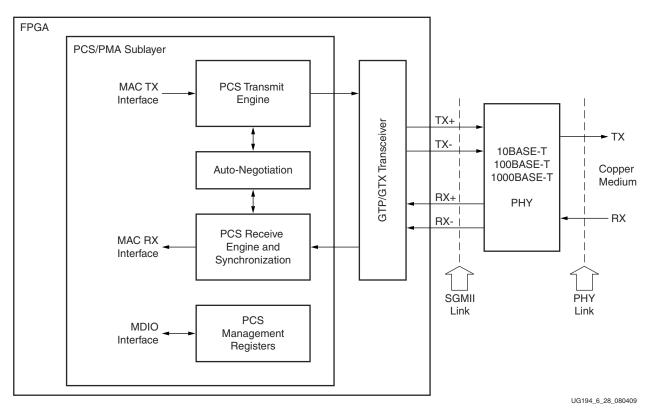

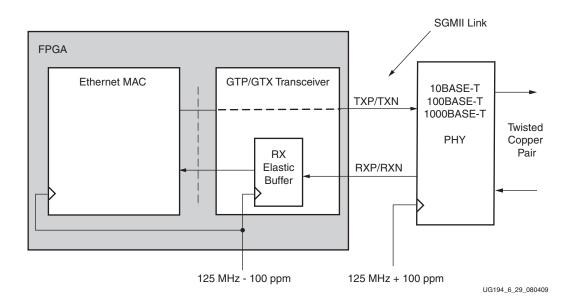

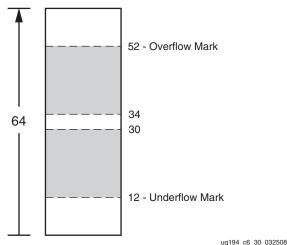

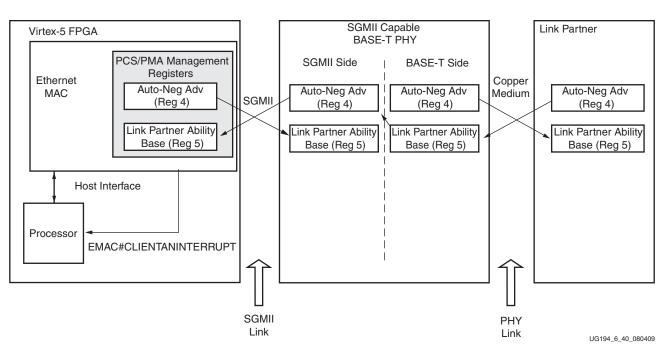

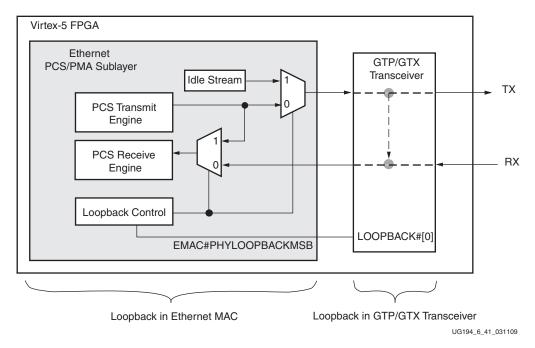

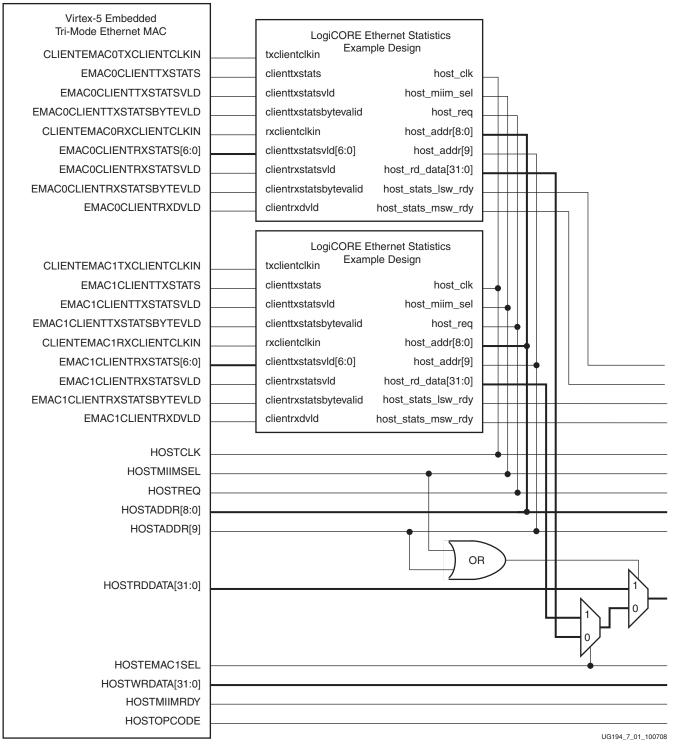

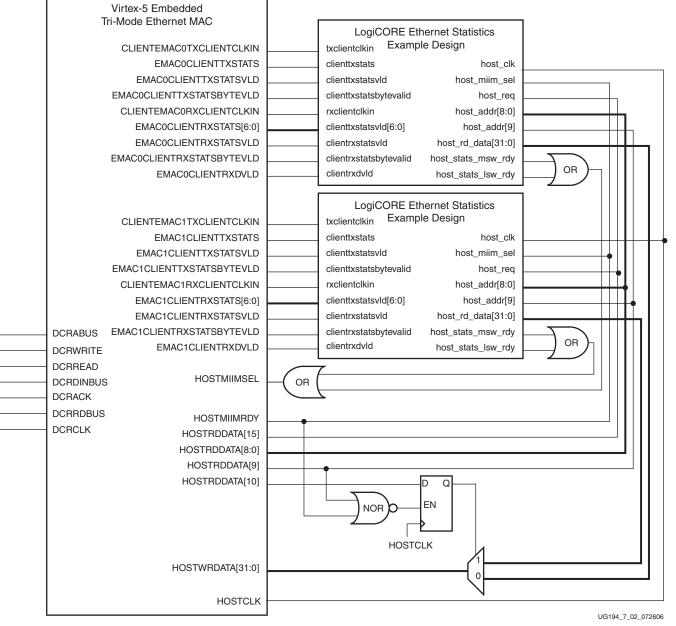

If, after initiating a transmission, the message collides with the message of another station (COL = 1), then each transmitting station intentionally continues to transmit (jam) for an additional predefined period (32 bit times for 10/100 Mb/s) to ensure propagation of the collision throughout the system. The station remains silent for a random amount of time (backoff) before attempting to transmit again.