# **RTL Technology and Schematic Viewers**

# Tutorial

UG685 (v11.2) July 17, 2009

Xilinx is disclosing this user guide, manual, release note, and/or specification (the "Documentation") to you solely for use in the development of designs to operate with Xilinx hardware devices. You may not reproduce, distribute, republish, download, display, post, or transmit the Documentation in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Xilinx expressly disclaims any liability arising out of your use of the Documentation. Xilinx reserves the right, at its sole discretion, to change the Documentation without notice at any time. Xilinx assumes no obligation to correct any errors contained in the Documentation, or to advise you of any corrections or updates. Xilinx expressly disclaims any liability in connection with technical support or assistance that may be provided to you in connection with the Information.

THE DOCUMENTATION IS DISCLOSED TO YOU "AS-IS" WITH NO WARRANTY OF ANY KIND. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DOCUMENTATION, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NONINFRINGEMENT OF THIRD-PARTY RIGHTS. IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOSS OF DATA OR LOST PROFITS, ARISING FROM YOUR USE OF THE DOCUMENTATION.

© 2009 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners.

## **Revision History**

The following table shows the revision history for this document.

| Date     | Version | Revision                      |

|----------|---------|-------------------------------|

| 05/18/09 | 1.0     | Initial Xilinx release.       |

| 07/17/09 | 1.1     | Updated for ISE 11.2 release. |

# Table of Contents

|      | Revision History                                              | iii |

|------|---------------------------------------------------------------|-----|

| Pref | face: About This Guide                                        |     |

|      | Guide Contents                                                | iii |

|      | Additional Resources                                          |     |

|      | Conventions                                                   |     |

|      | Typographical<br>Online Document                              | .iv |

| Cha  | pter 1: Schematic Viewer: Brief Overview                      |     |

|      | Design Flow Benefits                                          | . 1 |

|      | Key Features                                                  |     |

|      | RTL View                                                      |     |

|      | Post-Synthesis Netlist                                        |     |

|      | Critical Path View                                            |     |

|      | Flexibility for Both Project Navigator and Command Line Users |     |

|      | Case 1: You are a User of ISE Project Navigator               |     |

|      |                                                               |     |

| Cha  | pter 2: Tutorial Description                                  |     |

|      | Before Starting - Prerequisites                               | . 6 |

| Cha  | pter 3: Lab Preparation: Getting Started                      |     |

| Una  |                                                               | -   |

|      | Installing a Design                                           |     |

|      | Setting up Project Navigator Preferences                      | . 8 |

| Cha  | pter 4: Lab 1: Basic Features                                 |     |

|      | Objectives                                                    | . 9 |

|      | LAB                                                           | . 9 |

|      | Step 1: Create the Lab Project                                | . 9 |

|      | Step 2: Set XST Options and Synthesize Design                 |     |

|      | Step 3: Launch Schematic Wizard                               |     |

|      | Step 4: Schematic Viewer GUI Overview                         |     |

|      | Step 5: Zooming    Step 6: Schematic Expansion Methods        |     |

|      | Example                                                       |     |

|      | Step 7: Start/End Signal Markers                              |     |

|      | Step 8: History Navigation                                    | 16  |

|      | Step 9: Removing Elements from the Schematic                  | 18  |

### Chapter 5: Lab 2: Working with Hierarchical Netlists

| Objectives                                                      | 21 |

|-----------------------------------------------------------------|----|

| LAB                                                             |    |

| Step 1: Create Lab project                                      |    |

| Step 2: Set XST Options and Synthesize Design                   |    |

| Step 3: Launch Schematic Wizard                                 |    |

| Step 4: Understanding Hierarchical Block Symbols                |    |

| Step 5: Expanding Hierarchical Blocks                           | 23 |

| Step 6: Show/Hide Block Contents                                |    |

| Step 7: Bottom-Up Design Expansion                              |    |

| Step 8: Starting Schematic Exploration with the Top-Level Block |    |

| Conclusion                                                      |    |

### Chapter 6: Lab 3: Using Schematic Viewer for Timing Analysis

| <b>Objective</b>                                       |

|--------------------------------------------------------|

| LAB                                                    |

| Step 1: Create Lab project 29                          |

| Step 2: Specify Timing Constraints                     |

| Step 3: Specify XST options and Implement the Design   |

| Step 4: View the Critical Path in the Schematic Viewer |

| Step 5: Annotate Schematic with Timing Delays          |

| Conclusion                                             |

### Chapter 7: Lab 4: Simplifying Design Analysis

| <b>Objectives</b>                                                               |

|---------------------------------------------------------------------------------|

| LAB                                                                             |

| Step 1: Create Lab project                                                      |

| Step 2: Set XST Options and Synthesize Design                                   |

| Step 3: Working with Multiple Schematics of the Same Netlist                    |

| Step 4: Starting a New Schematic by Selecting Elements from the Current View 35 |

| Step 5: Using Colors to Highlight a Group of Specific Elements                  |

| Conclusion                                                                      |

### **Chapter 8: Lab 5: Comparing Two Design Implementations**

| <b>Objective</b>                                 |

|--------------------------------------------------|

| LAB                                              |

| Step 1: Create a Lab Project 41                  |

| Step 2: Set XST Options and Synthesize Design 41 |

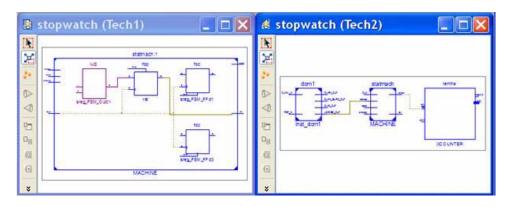

| Step 3: Load and Compare two Netlists 42         |

| Conclusion                                       |

### Chapter 9: Lab 6: Dealing with Large Designs

| Objective                              | 45 |

|----------------------------------------|----|

| Tip 1: Use Hierarchical Netlists       | 45 |

| Preserve Hierarchy                     | 45 |

| Rebuilding Hierarchy                   | 45 |

| Tip 2: Using Multiple Schematic Sheets | 46 |

| Conclusion |  |  |

|------------|--|--|

|------------|--|--|

## Chapter 10: Lab 7: Using the Schematic Viewer as a Standalone Tool

| Objectives                                                  | 47 |

|-------------------------------------------------------------|----|

| LAB                                                         | 47 |

| Step 1: Create Lab project                                  | 47 |

| Step 2: Set XST Options and Synthesize Design               | 47 |

| Step 3: Open the Post Synthesis Netlist in Schematic Viewer |    |

| Conclusion                                                  | 48 |

## Preface

# About This Guide

The goal of this tutorial is to provide a quick introduction to the main Schematic Viewer capabilities and how they can be used for design analysis and debugging.

This document contains a series of labs with step-by-step exercises which will enable you to learn different aspects of the Schematic Viewer.

### **Guide Contents**

This manual contains the following chapters:

- Chapter 1, "Schematic Viewer: Brief Overview," provides a brief overview of the Schematic Viewers, explaining how they can enhance your analysis and debugging productivity. In addition, we will highlight key features and capabilities available in the latest version of the Schematic Viewers.

- Chapter 2, "Tutorial Description," provides general information about features covered in each lab. We also describe the time required to complete each lab segment.

- Chapter 3, "Lab Preparation: Getting Started," contains instructions on how to get the designs for each lab and install them. In addition, we list preferences which must be set up before you start each lab.

- Chapters 4 through 10 contain labs.

- Chapter 4, "Lab 1: Basic Features"

- Chapter 5, "Lab 2: Working with Hierarchical Netlists"

- Chapter 6, "Lab 3: Using Schematic Viewer for Timing Analysis"

- Chapter 7, "Lab 4: Simplifying Design Analysis"

- Chapter 8, "Lab 5: Comparing Two Design Implementations"

- Chapter 9, "Lab 6: Dealing with Large Designs"

- Chapter 10, "Lab 7: Using the Schematic Viewer as a Standalone Tool"

### **Additional Resources**

To find additional documentation, see the Xilinx website at:

http://www.xilinx.com/support/documentation/index.htm.

To search the Answer Database of silicon, software, and IP questions and answers, or to create a technical support WebCase, see the Xilinx website at:

http://www.xilinx.com/support/mysupport.htm.

## Conventions

This document uses the following conventions. An example illustrates each convention.

## Typographical

The following typographical conventions are used in this document:

| Convention                  | Meaning or Use                                                                                                         | Example                                                                                                  |  |  |  |  |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--|--|--|--|

| Courier font                | Messages, prompts, and<br>program files that the system<br>displays                                                    | speed grade: - 100                                                                                       |  |  |  |  |

| Courier bold                | Literal commands that you enter in a syntactical statement                                                             | ngdbuild design_name                                                                                     |  |  |  |  |

| Helvetica bold              | Commands that you select from a menu                                                                                   | $File\toOpen$                                                                                            |  |  |  |  |

|                             | Keyboard shortcuts                                                                                                     | Ctrl+C                                                                                                   |  |  |  |  |

|                             | Variables in a syntax statement<br>for which you must supply<br>values                                                 | ngdbuild design_name                                                                                     |  |  |  |  |

| Italic font                 | References to other manuals                                                                                            | See the <i>Command Line Tools User Guide</i> for more information.                                       |  |  |  |  |

|                             | Emphasis in text                                                                                                       | If a wire is drawn so that it<br>overlaps the pin of a symbol, the<br>two nets are <i>not</i> connected. |  |  |  |  |

| Square brackets []          | An optional entry or parameter.<br>However, in bus specifications,<br>such as <b>bus [7:0]</b> , they are<br>required. | <b>ngdbuild</b> [option_name]<br>design_name                                                             |  |  |  |  |

| Braces { }                  | A list of items from which you must choose one or more                                                                 | lowpwr ={on off}                                                                                         |  |  |  |  |

| Vertical bar                | Separates items in a list of choices                                                                                   | lowpwr ={on off}                                                                                         |  |  |  |  |

| Vertical ellipsis<br>•<br>• | Repetitive material that has been omitted                                                                              | IOB #1: Name = QOUT'<br>IOB #2: Name = CLKIN'                                                            |  |  |  |  |

| Horizontal ellipsis         | Repetitive material that has been omitted                                                                              | <b>allow block</b> block_name loc1 loc2 locn;                                                            |  |  |  |  |

### **Online Document**

The following conventions are used in this document:

| Convention            | Meaning or Use                                             | Example                                                                                                         |  |  |  |

|-----------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|

| Blue text             | Cross-reference link to a location in the current document | See the section "Additional<br>Resources" for details.<br>Refer to "Title Formats" in<br>Chapter 1 for details. |  |  |  |

| Blue, underlined text | Hyperlink to a website (URL)                               | Go to <u>http://www.xilinx.com</u><br>for the latest speed files.                                               |  |  |  |

# Chapter 1

# Schematic Viewer: Brief Overview

### **Design Flow Benefits**

With the rapid growth in the size and complexity of FPGA designs, it is critical to have tools that ease the way you analyze and debug your designs.

Some common questions can be answered by using the Schematic Viewer:

- How is my HDL code interpreted by the synthesis tool?

- How is my HDL code mapped to the target technology?

- Where is my critical timing path situated?

In addition, today's advanced designs are often completed by several designers located in different parts of the world, where each designer is responsible for a part of the design. This complicates design analysis even further, and good debugging tools become critical.

Graphical tools such as Schematic Viewer, PlanAhead<sup>™</sup>, and FPGA Editor significantly simplify design analysis.

In this tutorial we introduce the latest version of the ISE<sup>®</sup> Schematic Viewer, a tool which provides powerful ways to view and analyze your designs from different perspectives.

### **Key Features**

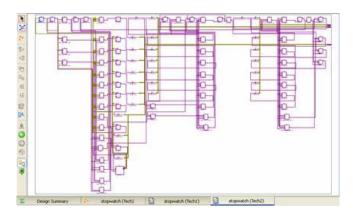

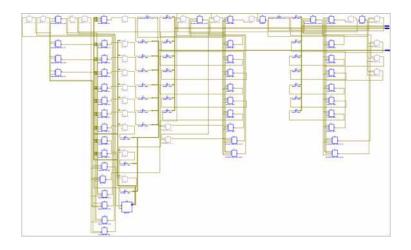

In prior releases, the Schematic Viewer was capable of showing you the entire RTL or postsynthesis netlist, typically spread across multiple pages. The new ISE 11 Schematic Viewer provides a more flexible interface by allowing you to focus on the particular part of the design that interests you. This ability to "localize" and incrementally expand the view on demand provides a significantly faster means to navigate through your design.

The ISE 11 Schematic Viewer provides you with powerful analysis features, such as:

- Drawing the schematic by selecting the only elements of interest

- Input/Output logic cone extraction

- Removing objects that are not of interest

- "Forward/Back" history navigation of previous analysis steps

- Capability to work with multiple schematics of the same netlist

| → □ → □ → □ → □ → □ → □ → □                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | inv             |                                                                     |      |       |                                          | <br>statmach:1    |            |                  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------------------------------------------------------|------|-------|------------------------------------------|-------------------|------------|------------------|--|--|

| Image: State State - Hegitild         Image: State State - Hegitild           Image: State State - Hegitild         Image: State State - Hegitild           Image: State State - Hegitild         Image: State - Hegitild           Image: State - Hegitild         Image: State - Hegitild | (Soperaticity,<br>ACH - BDHb<br>(COM), James<br>(COM), James<br>(COM) | strtsto         | pinv1_INV                                                           | _0   |       | C <u>LK</u><br>lockgg<br>mggt<br>attatop | in<br>0<br>sreg_F | lut<br>SM_ | 3<br>FFd3-Ir     |  |  |

| Check Syntax<br>Generate Post-Synt<br>Generate Post<br>Generate Postgamming<br>Generate Programming<br>Confraum Tarost Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | thesis Sende                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <u>.</u>        |                                                                     | 1.5  |       | 120070070                                |                   | IACH       |                  |  |  |

| wign Files Ubraries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | FPGA and CPLD 5 | slutions from Xilro, Inc.                                           | 1.92 | Desig | n Summary                                | stopwatch (Tech)  | E.         | stopwatch (Tech) |  |  |

| () compay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Design Objects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | of stopmatch    |                                                                     |      |       |                                          | Pr                | operties ( | No Selection)    |  |  |

| tances *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1               | Signals                                                             |      | *     | Name                                     |                   |            | Value            |  |  |

| A MACHEE<br>D sng FSM (F60-In F<br>D shtstopen1_DW_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | * A MORE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 | denable<br>dk_don<br>don_bok<br>don_bok<br>scist_bbuk<br>scist_bbuk |      |       |                                          |                   |            |                  |  |  |

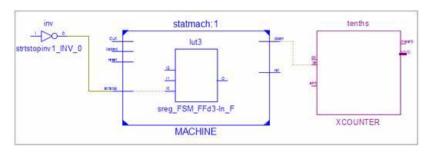

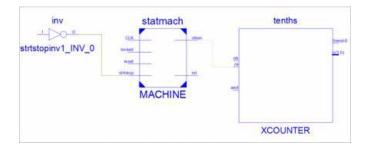

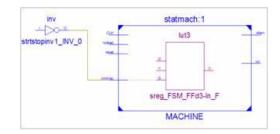

Figure 1-1: Schematic Viewer

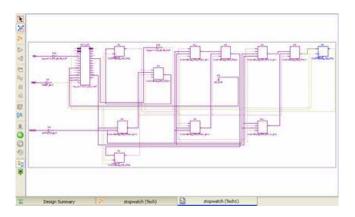

The Schematic Viewer as shown in Figure 1-1has significantly improved performance, which improves your ability to deal with higher complexity designs.

Ultimately, the Schematic Viewer provides you with the fundamental capabilities to visualize:

- RTL views of the design

- Post-synthesis netlists

- Critical timing path delays reported in the post place and route timing report (from Timing Analyzer)

#### **RTL** View

RTL View is a Register Transfer Level graphical representation of your design. This representation (**.ngr** file produced by Xilinx Synthesis Technology (XST)) is generated by the synthesis tool at earlier stages of a synthesis process when technology mapping is not yet completed. The goal of this view is to be as close as possible to the original HDL code. In the RTL view, the design is represented in terms of macro blocks, such as adders, multipliers, and registers. Standard combinatorial logic is mapped onto logic gates, such as AND, NAND, and OR.

#### Post-Synthesis Netlist

Graphical representation of the post-synthesis ("optimized and mapped") netlist (**.ngc** file produced by XST) contains Xilinx primitives as defined in the UNISIM library, such as LUTs, DCM, I/O buffers, and flip-flops. The Schematic Viewer allows you to visualize the primitive properties and the constraints attached to them.

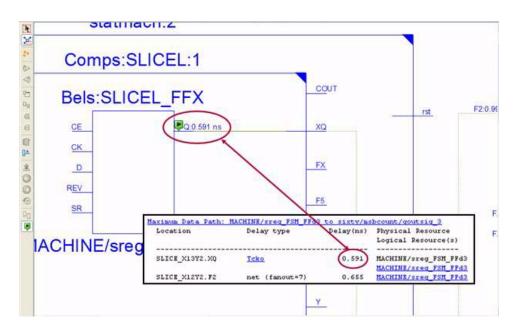

#### Critical Path View

When used as a cross-probe target from the Timing Analyzer report, the critical timing path of your design is represented using the post place and route netlist. This netlist is different from the post-synthesis netlist and represents your design in terms of slices.

## Flexibility for Both Project Navigator and Command Line Users

Your particular design methodology (command line vs. Project Navigator based) determines which set of features you can use in the Schematic Viewer. Please use the following table to familiarize yourself with the features available for you.

#### Case 1: You are a User of ISE Project Navigator

#### Table 1-1: Design Features

| Synthesis Tool | RTL View | Post-Synthesis<br>Netlist | Critical Path | Notes                                                                                     |

|----------------|----------|---------------------------|---------------|-------------------------------------------------------------------------------------------|

| XST            | Yes      | Yes                       | Yes           | Use ISE environment to fully implement your design, and XST is your synthesis tool        |

| 3rd party      | -        | -                         | Yes           | Use ISE environment to fully implement your design, and use a third-party synthesis tool. |

#### Case 2: You are a Command-line User

While you cannot launch Schematic Viewer in a standalone mode, there is a workaround to emulate this use model and enable you to use the Schematic Viewer to explore the XST RTL View or XST post-synthesis netlists (post-map, post-place, and route netlists are not yet handled in this mode).

Please refer to Chapter 10, "Lab 7: Using the Schematic Viewer as a Standalone Tool" for more information.

# Chapter 2

# **Tutorial Description**

Throughout this tutorial, we will use the small *stopwatch* design which is delivered with the Xilinx<sup>®</sup> ISE<sup>®</sup> software installation as an example design. We intentionally selected a small design to allow you to complete the labs as quickly as possible.

Less than one hour is required to complete the entire tutorial which covers all major features.

We suggest:

- Running the labs in order (Lab1, Lab2, etc.). That said, the labs are independent and can be run in any order if you wish to immediately focus on one particular functional area.

- Creating a separate design directory for each lab and copying the original design files to that directory. Please refer to Chapter 3, "Lab Preparation: Getting Started," for more information.

Because the majority of Schematic Viewer features can be accessed using either the RTL, Post-Synthesis netlist, or Critical Path views, we will use the Post-Synthesis netlist view in the majority of labs to demonstrate the main features.

The following table gives you a brief overview of all the labs.

| Title                                                  | Duration  | Covered Features                                                                                                                                                                                                                                                                                              |

|--------------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "Lab 1: Basic Features"                                | 9 minutes | <ul> <li>Selecting Schematic Viewer startup mode</li> <li>Using the Schematic Wizard</li> <li>Graphical User Interface (GUI) overview</li> <li>Zoom operations</li> <li>Expanding the schematic</li> <li>Coloring new elements</li> <li>History navigation</li> <li>Using Start/End signal markers</li> </ul> |

| "Lab 2: Working with<br>Hierarchical Netlists"         | 9 minutes | <ul> <li>Choosing hierarchical blocks in the Schematic Wizard</li> <li>Expanding hierarchical blocks</li> <li>Starting schematic exploration with the top-level block</li> </ul>                                                                                                                              |

| "Lab 3: Using Schematic<br>Viewer for Timing Analysis" | 6 minutes | <ul><li>Visualizing critical paths in the Schematic View</li><li>Annotating the critical path with path delays</li></ul>                                                                                                                                                                                      |

| Table 2-1: Lab Overview |

|-------------------------|

|-------------------------|

www.xilinx.com

| "Lab 4: Simplifying Design<br>Analysis"                     | 7 minutes | <ul> <li>Using Start/End signal markers</li> <li>Deleting schematic elements</li> <li>Using multiple schematics of the same netlist</li> <li>Starting a new schematic with selected elements</li> <li>Using colors to mark various elements</li> </ul> |

|-------------------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

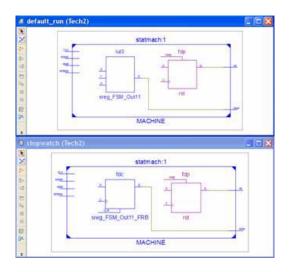

| "Lab 5: Comparing Two<br>Design Implementations"            | 5 minutes | • Loading and comparing two netlists of the same design                                                                                                                                                                                                |

| "Lab 6: Dealing with Large<br>Designs"                      | 3 minutes | • Overview of methods to handle large designs                                                                                                                                                                                                          |

| "Lab 7: Using the Schematic<br>Viewer as a Standalone Tool" | 3 minutes | • Learning how command line users may take advantage of the Schematic Viewer                                                                                                                                                                           |

## **Before Starting - Prerequisites**

The labs you will run through require some basic knowledge about the ISE Project Navigator environment. Before starting these labs, you should know:

- How to open and close an existing project

- How to add a new UCF (implementation constraint file) to the project and specify basic timing constraints using Constraint Editor

- How to run the basic implementation flow

- How to launch and use Timing Analyzer

# Chapter 3

# Lab Preparation: Getting Started

This chapter provides detailed instructions on:

- "Installing a Design" for each lab

- "Setting up Project Navigator Preferences" in ISE 11 software for each lab

### Installing a Design

Throughout the labs, you will use the small *stopwatch* design and target a Spartan<sup>®</sup>-3E xc3s100e-4-vq100 device. This design is delivered with the Xilinx<sup>®</sup> ISE<sup>®</sup> software installation and placed in the **ISEexamples** directory.

We **strongly suggest** creating a separate design directory for each lab and copying the original design files to each directory.

Instructions:

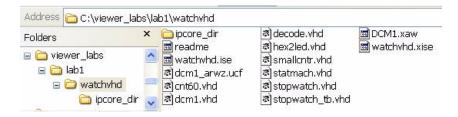

- 1. Create a **viewer\_labs** directory in the root directory of your **c**:\ drive and store all the schematic viewer labs there (**c**:\**viewer\_labs**).

- Created labn (where n is a lab number) sub-directories in viewer\_labs. For instance, c:\viewer\_labs\lab1.

- 3. Copy the **watchvhd.zip** file from the **ISEexamples** directory of the Xilinx ISE software installation to the **c:\viewer\_labs\labn** directory.

- 4. Unzip the **watchvhd.zip** file. Ultimately, you should have a directory structure similar to Figure 3-1.

Figure 3-1: Directory Structure

*Note:* Since there are seven labs altogether, we suggest that you prepare all the lab directories in advance to save time.

Launch the ISE Project Navigator and select watchvhd.xise project from the c:\viewer\_labs\labn\watchvhd directory.

*Note:* Starting from the ISE 11.1 software release, the ISE project is an XML file with the extension .xise.

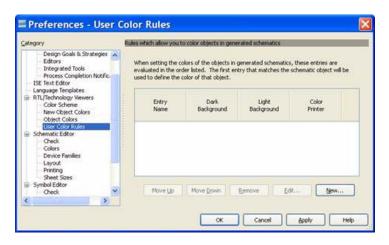

## **Setting up Project Navigator Preferences**

To ensure that the lab screenshots provided in this tutorial match the schematic you see on your screen, you have to setup the **Light Background Color Scheme** for Schematic Viewer before starting the lab.

Instructions:

- 1. Open the Preferences dialog box by selecting  $Edit \rightarrow Preferences...$

- 2. In the left pane, expand **RTL/Technology Viewers** and select the **Color Scheme** subcategory.

| Integrated Tools<br>Process Completion Nobi<br>TSE text Editor<br>Language Templetion<br>RTL/Technology Viewers<br>Color Scheme<br>New Object Colors<br>Object Colors                                                            | Preferred Display Color Scheme  Select one of the following color schemes:  Dark Background Color Scheme  Ught Background Color Scheme |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| User Color Rules     User Color Rules     Chematic Editor     Check     Colors     Device Families     Layout     Printing     Sheet Sizes     Symbol Editor     Check     Colors     Timing Analyzer     WebTalk     WinxUpdate | Export and Import You can export this set of colors to a file and import them later, or share the file with other users Export Import  |

| - Proxy Settings                                                                                                                                                                                                                 |                                                                                                                                        |

Figure 3-2: Color Scheme Selection

3. Select Light Background Color Scheme in zone 1 (see Figure 3-2) of the dialog box, click Applyand click OK to finish.

Now you are ready to start the labs.

# Chapter 4

# Lab 1: Basic Features

## **Objectives**

The goal of this lab is to familiarize you with the basic Schematic Viewer operations which will be used extensively in later exercises. These include:

- Selecting Schematic Viewer startup mode

- Working with the Schematic Wizard

- Understanding the Schematic Viewer GUI

- Zooming operations

- Expanding schematics in various ways

- Removing elements from a schematic

- Coloring new elements

- Navigating history

- Using Start/End signal markers

For the sake of clarity and simplicity, please note that all the above features will be demonstrated using a flattened post-synthesis netlist. Hierarchical netlist navigation will be introduced in the next lab.

## LAB

### Step 1: Create the Lab Project

Create and open the *stopwatch* project and set the **Light Background Color Scheme** for Schematic Viewer, as described in the Chapter 3, "Lab Preparation: Getting Started."

### Step 2: Set XST Options and Synthesize Design

- 1. In the Process panel, right-click on **Synthesis XST**, and select **Properties** to open the XST Synthesis Properties dialog box.

- 2. Set the Keep Hierarchy option to **No** as shown in Figure 4-1.

| Category                               | Property Name            | Value        |   |

|----------------------------------------|--------------------------|--------------|---|

| Synthesis Options                      | Library Search Order     |              |   |

| HDL Options<br>Xilinx Specific Options | Keep Hierarchy           | No           |   |

|                                        | Netlist Hierarchy        | As Optimized | * |

|                                        | Global Optimization Goal | AllClockNets | ~ |

Figure 4-1: Setting Keep Hierarchy Option

3. Synthesize the design by double-clicking the **Synthesize - XST** process in the Process panel:

#### Step 3: Launch Schematic Wizard

Before you can view a schematic of your design, you need to select the elements you would like to use as a starting point for your design exploration.

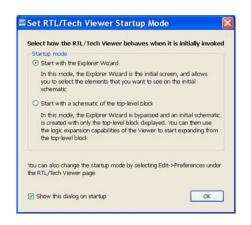

You can start design exploration in the two different startup modes.

- **Start with the Explorer Wizard**. In this mode, the Explore Wizard is the initial screen mode, and allows you to select the elements that you want to see on the initial schematic. This mode will be used in the current Lab.

- Start with a schematic of the top-level block. In this mode, the Explorer Wizard is bypassed and an initial schematic is created with only the top-level block displayed. You can then use the logic expansion capabilities of the Viewer to start expanding from the top-level block. You need to familiarize yourself with the basic Schematic Viewer operations and learn how you can manipulate hierarchical blocks before using this mode. Please refer to Chapter 5, "Lab 2: Working with Hierarchical Netlists" for more information on this startup mode.

- As soon as synthesis is completed, start the Schematic Viewer by double-clicking the View Technology Schematic process found in the Process panel, or, alternatively, by selecting Tools → Schematic Viewer → Technology View from the menu.

- 2. Select the Start with the Explorer Wizard startup mode as shown in Figure 4-2.

Figure 4-2: Set Viewer Startup Mode

The Schematic Wizard enables you to select elements for exploration start up. See Figure 4-3.

#### **Create Technology Schematic**

1) Select items you want on the schematic from the "Available Elements" list and move them to the "Selected Elements" list - Use the Filter control to filter the "Available Elements" list by name

| 2) Press the "Create Schematic" buttor | i to generate a schematic view using the it | ems in the "Selected Elements" list |

|----------------------------------------|---------------------------------------------|-------------------------------------|

|                                        |                                             |                                     |

| Available Elements  | ▲      |                   | Selected Elements |

|---------------------|--------|-------------------|-------------------|

| 🖻 🚣 stopwatch       |        | <u>A</u> dd ->    |                   |

| 😟 📁 Primitives      |        |                   |                   |

| 😟 📁 🗊 Signals       |        | <- <u>R</u> emove |                   |

| 🖅 📁 Top Level Ports |        |                   |                   |

|                     |        | < Remove All      |                   |

|                     |        |                   |                   |

| *                   | Filter |                   | Create Schematic  |

|                     |        |                   |                   |

Figure 4-3: Schematic Wizard

In the **Available Elements** window, you will find all the objects available in the design. They are classified in the following categories: primitives, signals, top level ports, and hierarchical blocks.

*Note:* Hierarchical blocks are visible in hierarchical netlists only. Please refer to Chapter 5, "Lab 2: Working with Hierarchical Netlists" for more information on working with hierarchical designs.

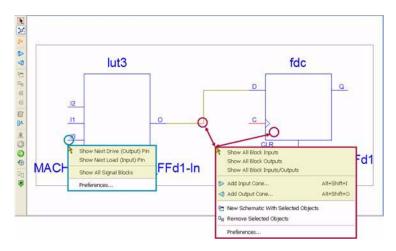

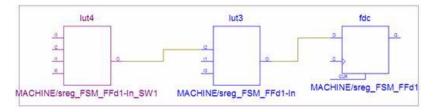

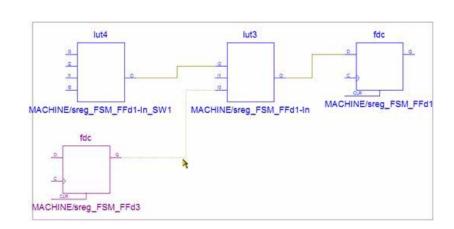

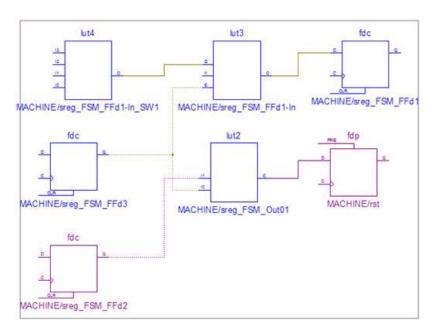

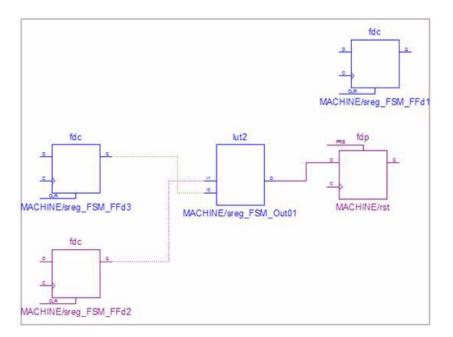

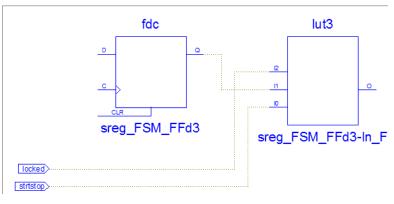

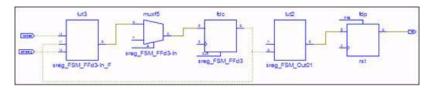

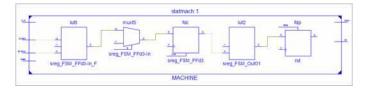

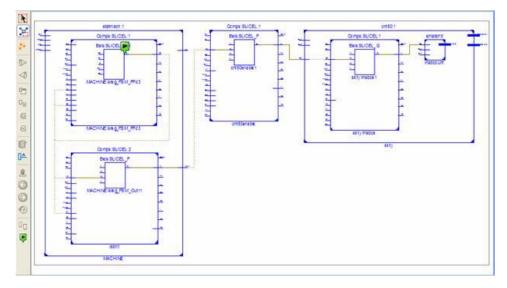

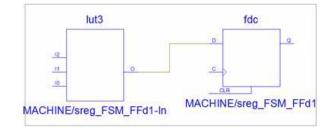

Select MACHINE/sreg\_FSM\_FFd1 and MACHINE/sreg\_FSM\_FFd1-In from the primitives category of Available Elements and add them to the Selected Elements list using the Add -> button. See Figure 4-4.

| Available Elements *             | ^ |                | Selected Elements        | 1.0 |

|----------------------------------|---|----------------|--------------------------|-----|

| MACHINE/rst                      | - | Add ->         | MACHINE/sreg_FSM_FFd1    |     |

| MACHINE/sreg_FSM_FFd1            |   |                | MACHINE/sreg_FSM_FFd1-In |     |

| MACHINE/sreg_FSM_FFd1-In         |   | <- Remove      |                          |     |

| MACHINE/sreg_FSM_FFd1-In_SW0     |   |                |                          |     |

| - D MACHINE/sreg FSM FFd1-In SW1 | Y | <<- Remove All |                          |     |

Figure 4-4: Available Elements

If the list of elements is too long, you can use the **Filter** to reduce the search scope. As an example in our case, you may specify **MACHINE/sreg\_FSM\_FFd1**\* as a search criteria as shown in Figure 4-5.

| Available Elements           | ^   |              | Selected Elements |

|------------------------------|-----|--------------|-------------------|

| 😑 📁 Primitives               |     | Add ->       |                   |

| MACHINE/sreg_FSM_FFd1        | 1   |              |                   |

| MACHINE/sreg_FSM_FFd1-In     |     | <- Remove    |                   |

| MACHINE/sreg_FSM_FFd1-In_SW0 | i i |              |                   |

| MACHINE/sreg_FSM_FFd1-In_SW1 | Y   | < Remove All |                   |

Figure 4-5: Filtering

4. Press the **Create Schematic** button to create the schematic.

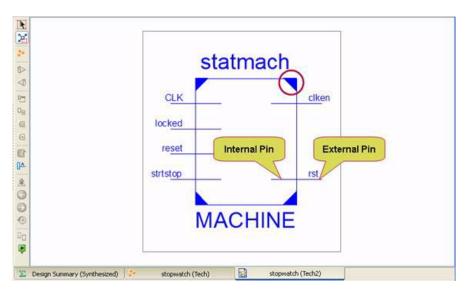

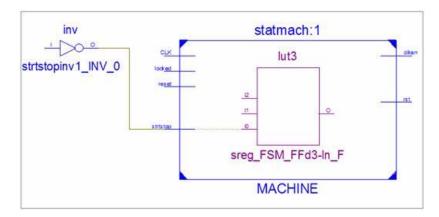

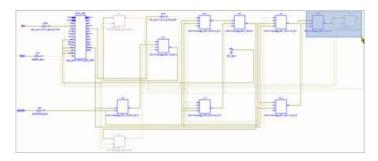

#### Step 4: Schematic Viewer GUI Overview

The Schematic Viewer GUI has the following components as shown in Figure 4-6.

|         | an ····································                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                                                                      | 0              |                  | IT                         |                |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------|------------------|----------------------------|----------------|

| 80 80 M | Wetch-hd     A readain     Xcalifore-fvq100     Montext-reader(stopwatch,vhd)     Montext-reader(stopwatch,vhd)     Montext-reader(stopwatch,vhd)     Montext-reader(stopwatch,vhd)     Montext-reader(stopwatch,vhd)     Montext-reader(stopwatch,vhd)     Montext-reader(stopwatch,vhd)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | AV D                                                                   |                | lut3             | 0                          | fdc            |

|         | XCOUNTER - tenths (pcore_de)tenths.     decode - behavioral (decode.     sity - creso - nade (creso.vhd)     S     Fracesses: stacewatch - made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                        | <u>e</u>       | 0                |                            |                |

| に元日     | Design Summary/Reports     Design Utilities     Over Combanets     Over Combanets     Over Ris Schematic     Over Sin Schematic     Over Sinchadogy Schematic     Over Sinchado Sinchado     Over     Over Sinchado     Over     Over Sinchado     Over Sinchado | <ul> <li>S = 0</li> <li>S = 0</li> <li>S = 0</li> <li>S = 0</li> </ul> | MACHINE/sre    | g_FSM_FFd1-      | in                         | sreg_FSM_FFc   |

|         | sign Files Libraries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2                                                                      | Design Summary | stopsatch (Tech) | stopwatch (Tech1)          |                |